数字系统的逻辑电路分为两大类

- 格式:doc

- 大小:414.50 KB

- 文档页数:23

大学课程《数字电子技术基础》试题及答案一、填空题组合逻辑电路1. 数字电路按逻辑功能的不同特点可分为两大类,即: 逻辑电路和 逻辑电路 。

答:组合 、时序2. 从一组输入数据中选出一个作为数据传输的常用组合逻辑电路叫做 。

答:数据选择器3.用于比较两个数字大小的逻辑电路叫做 。

答:数值比较器4. 驱动共阳极七段数码管的译码器的输出电平为 有效,而驱动共阴极的输出电平为 有效。

答:低、高5.一个8选1的多路选择器(数据选择器),应具有 个地址输入端。

答:3个6.编码器的逻辑功能是把输入的高低电平编成一个 ,目前经常使用的编码器有普通编码器和优先编码器两类。

答:二值代码7.译码器的逻辑功能是把输入的二进制代码译成对应的 信号,常用的译码器有二进制译码器,二-十进制译码器和显示译码器三类。

答:输出高、低电平8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

答:10111111二、选择题组合逻辑电路1.74LS138是3线-8线译码器,译码输出为低电平有效,若输入A 2A 1A 0=100时,输出= 。

A 、00010000,B 、11101111C 、11110111D 、10000000答:B2.在下列逻辑电路中,不是组合逻辑电路的是( )。

A 、译码器B 、编码器C 、全加器D 、寄存器 答:D3.在下列逻辑电路中,不是组合逻辑电路的是( )。

A. 译码器B. 编码器C. 全加器D.寄存器 答:D4. 八选一数据选择器组成电路如下图所示,该电路实现的逻辑函数是Y= 。

A. ABC ABC ABC ABC +++ B. ABC ABC + C. BC ABC +D. ABC ABC ABC ABC +++ 答:D5.七段显示译码器是指 的电路。

A. 将二进制代码转换成0~9数字B. 将BCD 码转换成七段显示字形信号C. 将0~9数字转换成BCD 码D. 将七段显示字形信号转换成BCD 码 答:B6.组合逻辑电路通常由 组合而成。

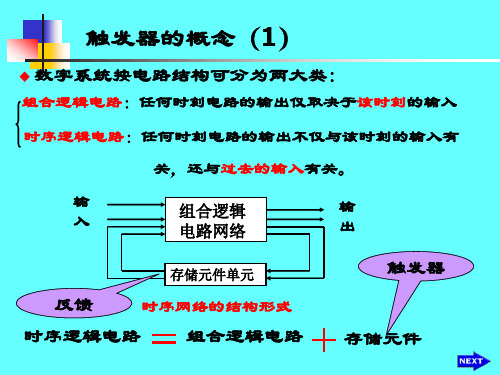

数字逻辑电路的分类与特点从整体上来看,数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。

在逻辑功能方面,组合逻辑电路在任一时刻的输出信号仅与当时的输入信号有关,与信号作用前电路原来所处的状态无关;而时序逻辑电路在任一时刻的输出信号不仅与当时的输入信号有关,而且还与电路原来的状态有关。

在电路结构方面,组合逻辑电路仅由若干逻辑门组成,没有存储电路,也没有输出到输入的反馈回路,因而无记忆能力;而时序逻辑电路除包含组合电路外,还含有存储电路,因而具有记忆能力。

在时序逻辑电路中,存储电路常由触发器组成,根据这些触发器时钟接法的不同,时序分为同步时序逻辑电路和异步时序逻辑电路。

在同步时序逻辑电路中,存储电路内所有触发器的时钟输入端都接同一个时钟脉冲源,因而,所有触发器的状态(即时序逻辑电路的状态)的变化都与所加时钟脉冲信号同步。

在异步时序逻辑电路中,没有统一的时钟脉冲,某些触发器的时钟输入端与时钟脉冲源相连,这些触发器的状态变化与时钟脉冲同步,而其他触发器状态的变化并不与时钟脉冲同步。

同步时序电路的速度高于异步时序电路,但电路结构一般较后者复杂;而异步时序电路的瞬时功耗要小于同步时序电路,但各触发器不同时翻转,容易引发事故。

数字电路研究和处理的对象是数字信号,而数字信号在时间上和数值上均是离散的,因而数字电路中的电子器件通常工作在饱和区和截止区,信号通常只有高电平和低电平两种状态。

这两种状态可用二进制的1和0来表示,因而可以用二进制对数字信号进行编码。

由于数字信号的高电平和低电平表示的都是一定的电压范围,所以我们可以着重考虑信号的有无,而不必过多关心信号的大小。

数字电路主要研究电路单元系统的输入和输出状态之间的逻辑关系,即逻辑功能。

数字电路的以上特点,决定了数字电路具有速度快、精度高、抗干扰能力强和易于集成等优点,在当今的自动控制、测量仪表、数字通信和智能计算等领域,都得到了相当广泛的应用。

习题答案第一章数制和码制1.数字信号和模拟信号各有什么特点?答:模拟信号——量值的大小随时间变化是连续的。

数字信号——量值的大小随时间变化是离散的、突变的(存在一个最小数量单位△)。

2.在数字系统中为什么要采用二进制?它有何优点?答:简单、状态数少,可以用二极管、三极管的开关状态来对应二进制的两个数。

3.二进制:0、1;四进制:0、1、2、3;八进制:0、1、2、3、4、5、6、7;十六进制:0、1、2、3、4、5、6、7、8、9、A、B、C、D、E、F。

4.(30.25)10=( 11110.01)2=( 1E.4)16。

(3AB6)16=( 0011101010110110)2=(35266)8。

(136.27)10=( 10001000.0100)2=( 88.4)16。

5.B E6.ABCD7.(432.B7)16=( 010*********. 10110111)2=(2062. 556)8。

8.二进制数的1和0代表一个事物的两种不同逻辑状态。

9.在二进制数的前面增加一位符号位。

符号位为0表示正数;符号位为1表示负数。

这种表示法称为原码。

10.正数的反码与原码相同,负数的反码即为它的正数原码连同符号位按位取反。

11.正数的补码与原码相同,负数的补码即为它的反码在最低位加1形成。

12.在二进制数的前面增加一位符号位。

符号位为0表示正数;符号位为1表示负数。

正数的反码、补码与原码相同,负数的反码即为它的正数原码连同符号位按位取反。

负数的补码即为它的反码在最低位加1形成。

补码再补是原码。

13.A:(+1011)2的反码、补码与原码均相同:01011;B: (-1101)2的原码为11101,反码为10010,补码为10011.14.A: (111011)2 的符号位为1,该数为负数,反码为100100,补码为100101. B: (001010)2 的符号位为0,该数为正,故反码、补码与原码均相同:001010.15.两个用补码表示的二进制数相加时,和的符号位是将两个加数的符号位和来自最高有效数字位的进位相加,舍弃产生的进位得到的结果就是和的符号。

数字系统的逻辑电路分为两大类,即组合逻辑电路和()<答案>时序逻辑电路填空题 0.4 2 1时序电路的输出与()有关。

<答案>当前输入和当前状态填空题 0.4 2 1组合电路中的险态是由于()引起的<答案>门电路的延时填空题 0.4 2 1组合电路中的险态是由于()引起的。

①门电路的逻辑关系②门电路的延时③电路干扰④随机信号<答案>2选择题 0.4 2 4在数字逻辑电路中,高电平用“1”表示,低电平用“ 0”表示。

<答案>F判断题 0.2 1 0功能相同的两个逻辑电路,若其中一个有险象,则另外一个也有险象()<答案>F判断题 0.2 1 0并不是所有的竞争都会产生冒险()<答案>T判断题 0.2 1 0设S i为一位全加器的和,(S i)d为S i的对偶式,则有S i=(S i)d ()<答案>T判断题 0.5 7 0时序电路的结构特征是包含有存储元件。

()<答案>T判断题 0.2 1 0设A,B均为一位二进制数,则它的半加和S H=AB+AB或A⊕B ()<答案>T功能相同的逻辑电路,若其中有一个有险象,则其它电路也有险象()<答案>F判断题 0.7 1 0从电路结构来看,组合逻辑电路具有哪两个特点?<答案>1)电路由逻辑门组成,没有存储器件,无记忆功能;2)输入信号是单向传输的,电路中不存在任何反馈回路。

问答题 0.4 10 0判断函数F=(A + B )(A + C )组成的逻辑电路是否存在冒险,若存在则消除可能出现的冒险<答案>可以出现险态,当B=1,C=1时,F=A A,出现险态,通过增加冗余项来消除险态。

F=(A+B)(A+C)(B+C)分析题 0.6 10 0用基本公式和基本规则证明下列等式A⊕B⊕C=A⊙B⊙C<答案>证明原式左边=A⊕B⊕C=AB⊕C+AB⊕C = A (B C + B C ) + A ( B C + B C )= A B C + A B C + A B C + A B C原式右边=A⊙B⊙C=A B⊙C + A (B⊙C) = A ( B C + B C ) + A ( B C + B C )= A B C + A B C + A B C + A B C原式左边=右边证明题 0.4 10 0用或非门实现函数F(A,B,C,D)=∏M(0,1,2,3,8,12)·∏d(4,5)<答案> A设计题 0.5 10 0用或非门实现函数F(A,B,C,D)=AB D+AC+A C D+AD<答案>设计一个代码转换电路,将一位8421BCD码转换成余3码。

要求:1)建立真值表2)写出函数的最小项表达式3)化简函数表达式4)将表达式表示成“与非”形式(要求按设计步骤做,不要求画逻辑图)。

<答案>真值表2)函数表达式W(A,B,C,D)=∑m(5,6,7,8,9)+∑d(10,11,12,13,14,15)X(A,B,C,D)=∑m(1,2,3,4,9)+∑d(10,11,12,13,14,15)Y(A,B,C,D)=∑m(0,3,4,7,8)+∑d(10,11,12,13,14,15)Z(A,B,C,D)=∑m(0,2,4,6,8)+∑d(10,11,12,13,14,15)3) 化简函数表达式W(A,B,C,D) = A+BC+BDX(A,B,C,D) = B C + B D + B C DY (A,B,C,D) = C D + C DZ(A,B,C,D) = D3) 将表达式表示成“与非”形式W(A,B,C,D)= A+BC+BD = A B C B DX(A,B,C,D)= B C + B D + B C D = B C B D B C DY(A,B,C,D)= C D + C D =C D +C DZ(A,B,C,D) = D设计题 0.5 14 0用与非门设计一个组合电路,该电路输入为一位十进制821BCD码,但输入的数字为素数时,输出F为1,否则F为0。

要求:1)建立真值表2)写出输出函数的最小项表达式3)化简函数表达式4)将表达式表示成“与非”形式(要求按设计步骤做,不要求画逻辑图)<答案>设计题 0.5 17 0设计一个代码转换电路,将一位十进制数的余三码转换成2421码。

要求:a)建立真值表b)写出函数的最小项表达式c)化简函数表达式d)将表达式表示成“与非”形式(要求按设计步骤做,不要求画逻辑图)。

<答案>设计题 0.6 16 0用与或非门设计一个BCD码变余3码的转换电路。

(要求按设计步骤做,最后得到与或非形式的表达式即可,不要求画逻辑图)。

<答案>设计题 0.5 14 0用门电路设计一个比较两个两位二进制数A 及B 的电路,要求当A=B 时,输出F =1。

<答案>设A=x1x2 B=y1y2F = x1 x2 y1 y2 + x1 x2 y1 y2 + x1 x2 y1 y2+ x1 x2 y1 y2 设计题 0.5 10 0设计一个奇偶判别电路,其输入为一位十进制的BCD 码。

当输入为偶数时,电路输出为0;当输入为奇数时,电路输出为1,如图所示。

列出描述该电路的布尔函数真值表并得到最简代数式,并画出逻辑电路图。

<答案>BAD CF设计题 0.4 10 0已知X=x1x2,Y=y1y2,其中x1,x2,y1,y2∈{0,1},试用与非门设计一个判X ≤Y的逻辑电路。

要求:①列出真值表②写出X≤Y的表达式③卡诺图化简④用与非门表示化简后的函数表达式<答案>设计题 0.5 12 0某执行机构只有在接收到三路信息完全相同时才能正常工作,否则就会产生告警。

(假设工作信息用“1”表示,告警信息用“0”表示)试用四选一多路选择器,设计一个满足上述要求的逻辑电路。

<答案> 工作信息 F1 = A B C + A B C = ∑m(0,7)报警信息 F2 = A B C + A B C = ∑m(1,2,3,4,5,6)四路选择器的输出 W = A1 A0 D0 + A1 A0 D1 + A1 A0 D2 + A1 A0 D3欲使W=F1,则应有四路选择器的第一组 D0=C D1=0 D2=0 D3=CF2(A,B,C) = A B C + A B C + A B C + A B C + A B C + A B C= A B C + A B (C + C) + A B (C + C) + A B C欲使W=F2,则应有四路选择器的第二组D0=C D1=1 D2=1 D3=C设计题 0.7 10 0判断函数F (A,B,C) = A B + A C是否发生竞争?竞争结果是否会产生险象?若可能产生险象,试用增加冗余项的办法消除<答案>会发生竞争,并导致险象,若增加一项BC可以消除险态即 F(A,B,C) = A B + A C + B C分析题 0.4 4 0判断逻辑函数 F = A C + A C D + B C D实现的逻辑电路是否存在冒险,若有,如何消除。

<答案>存在冒险当A=B=D=1和 A=1 B=0 D=1时 F = C + C消除的办法是增加冗余项F = A C + A C D + B C D +A D分析题 0.5 4 0设计一个逻辑电路,其输入为四位二进制数,当输入二进制数能被4或5整除时,电路给出指示,要求用“与非”门设计。

<答案>设计题 0.5 12 0判断逻辑函数 F = (A + B )(B + C )(A + C)实现的逻辑电路是否存在冒险,若有,如何消除<答案>存在冒险F = (A + B )(B + C )(A + C)C分析题 0.6 5 0判断逻辑函数 F(A,B,C,D)= A D + B D实现的逻辑电路是否存在冒险,若有,如何消除。

<答案>存在冒险当A=B=1时, F = D + D消除 F(A,B,C,D) = A D + B D + A B分析题 0.4 3 0判断逻辑函数 F = A C + A C D + B C D实现的逻辑电路是否存在冒险,若有,如何消除。

<答案>存在冒险消除 F = A C + A C D + B C D + A B D分析题 0.5 5 0组合逻辑电路的特点是( )<答案>无记忆功能,无反馈回路填空题 0.4 2 1所谓组合电路的险象是( )<答案>由于门电路的延时,当输入变化时,产生竞争,有的竞争导致电路产生错误输出填空题 0.4 2 1在数字电路中高电平用“1”表示,低电平用“0”表示。

……………()<答案>F判断题 0.2 1 0用与非门设计一个无冒险的组合逻辑电路。

该电路的输入为一位十进制数的余3码,当输入的数值能被3整除时,输出F为1,否则F为0。

要求:1、作出该电路的真值表;2、用卡诺图法化简逻辑函数;3、所设计的电路没有险象。

<答案>设计题 0.6 10 0用与非门设计一个无冒险的组合逻辑电路。

该电路的输入为一位十进制数的8421码,当输入的数值不为0且能被3整除时,输出F为1,否则F为0。

要求:1、作出该电路的真值表;(8分)2、用卡诺图法化简逻辑函数;(6分)3、所设计的电路没有险象。

(6分)<答案>设计题 0.6 13 0设计一个检测器的组合电路,检测四位二进制码中1的个数是否为偶数,若为偶数个1,则输出F为1,否则F为0。

<答案>设计题 0.5 12 0已知描述某组合逻辑电路的函数表达式为 F = A B C + A C + A D,用增加冗余项的办法消除该电路中可能产生的险象(10分)<答案>CD AB 00 01 11 10存在冒险消除 F = A B C + A C + A D + A B D分析题 0.4 4 0试设计一个8421BCD码的检码电路,要求当输入量ABCD<=2,或>=7时,电路输出F为高电平,否则为低电平。

试设计该电路,并用与非门实现之。

要求:1建立真值表2写出函数的最小项表达式3化简函数表达式(要求按设计步骤做,不要求画逻辑图)。

<答案>设计题 0.5 10 0组合逻辑电路的定义是什么?<答案>指电路任何时刻产生的稳定输出仅仅取决于该时刻各输入值的组合,而与过去的输入值无关问答题 0.4 3 0用与非门设计一个三变量的奇数电路。