《数字逻辑电路》期末考试试题

- 格式:doc

- 大小:268.50 KB

- 文档页数:5

期末考试试题(答案)一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

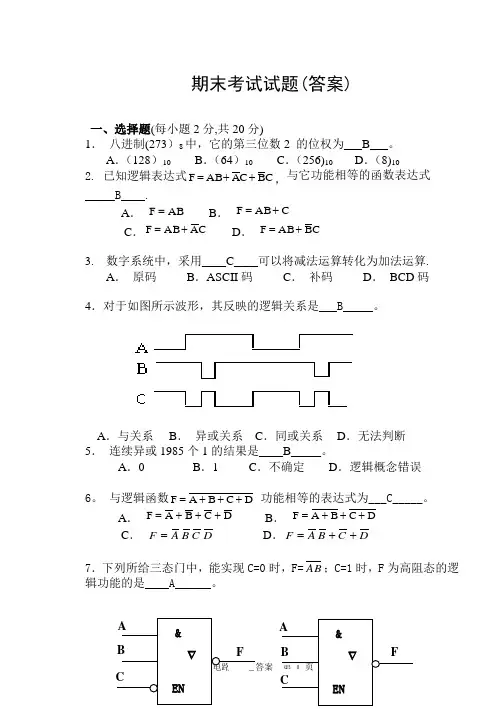

A .(128)10B .(64)10C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____.A .AB F = B .C AB F += C .C A AB F +=D . C B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算.A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断 5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6。

与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D C B A F +++= B . D C B A F +++=C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。

B A F & ∇ F B A &8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。

A. 500KHz B.200KHzC. 100KHz D.50KHz9.下列器件中,属于时序部件的是_____A_____.A.计数器B.译码器C.加法器D.多路选择器10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。

A. 0100100 B.1100011 C. 1011011 D.0011011二、填空题(每小题2分,共20分)11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2。

数字电路期末考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑(AND)B. 或逻辑(OR)C. 非逻辑(NOT)D. 异或逻辑(XOR)答案:C2. 下列哪个不是数字电路的特点?A. 精确度高B. 稳定性好C. 功耗大D. 抗干扰能力强答案:C3. 一个简单的触发器可以存储多少位二进制信息?A. 1位B. 2位C. 3位D. 4位答案:A4. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B5. 在数字电路中,同步计数器与异步计数器的主要区别是:A. 同步计数器速度更快B. 同步计数器结构更复杂C. 同步计数器计数更准确D. 异步计数器计数更准确答案:A6. 一个4位二进制计数器最多能计数到:A. 15B. 16C. 8D. 4答案:B7. 以下哪个是数字电路中常用的存储元件?A. 电阻B. 电容C. 电感D. 晶体管答案:D8. 以下哪个不是数字电路中的逻辑门?A. NANDB. NORC. XORD. TRIAC答案:D9. 一个完整的数字电路设计流程包括以下哪些步骤?A. 需求分析B. 电路设计C. 仿真测试D. 所有选项答案:D10. 以下哪个是数字电路中的时序逻辑电路?A. 门电路B. 触发器C. 运算放大器D. 模数转换器答案:B二、简答题(每题5分,共20分)1. 简述数字电路与模拟电路的区别。

答案:数字电路主要处理离散的数字信号,具有逻辑功能,而模拟电路处理连续的模拟信号,主要用于信号放大、滤波等。

2. 解释什么是触发器,并说明其在数字电路中的作用。

答案:触发器是一种具有记忆功能的逻辑电路,能够存储一位二进制信息。

在数字电路中,触发器用于存储数据,实现计数、定时等功能。

3. 什么是组合逻辑电路?请举例说明。

答案:组合逻辑电路是由逻辑门组成的电路,其输出只依赖于当前的输入状态,不具有记忆功能。

学习中心/函授站_姓名学号西安电子科技大学网络与继续教育学院2020 学年下学期《数字逻辑电路》期末考试试题(综合大作业)题号一二三四总分题分30 10 30 30得分考试说明:1、大作业试题于2020 年10 月15 日公布:(1)毕业班学生于2020 年10 月15 日至2020 年11 月1 日在线上传大作业答卷;(2)非毕业班学生于2020 年10 月22 日至2020 年11 月8 日在线上传大作业答卷;(3)上传时一张图片对应一张A4 纸答题纸,要求拍照清晰、上传完整;2、考试必须独立完成,如发现抄袭、雷同均按零分计;3、答案须用《西安电子科技大学网络与继续教育学院标准答题纸》手写完成,要求字迹工整、卷面干净。

一、单项选择题(每小题2 分,共40 分)1、下列各数中与十进制数101 不相等的数是( D )。

A.(0100 0011 0100)余3BCD B.(141)8C.(1100101)2D.(66)162、八进制数(35)8的8421BCD 是( B )。

A.0011 1000B.0010 1001C.0011 0101D.0010 11003、为使与非门输出为1 则输入( A )。

A.只要有0 即可B.必须全为0C.必须全为1D.只要有1 即可4、函数F AC BC AB与其相等的表达式是( B )。

A.BC B.C+AB C.AC AB D.AB5、使函数F AB AC BC 等于 0 的输入 ABC 的组合是( C )。

A .ABC=111 B .ABC=110 C .ABC=100 D .ABC=0116、四变量的最小项ABCD 的逻辑相邻项是( A )。

A .ABCDB .ABCDC .ABCD D .ABCD 7、函数 F ABC B .C (A D )BC 的对偶式是( C )。

A .G (A B C )(B C )(AD B C )B .G A BC (B C )ADB CC .G A B C (B C )(AD B C )D .G A BC (B C )AD B C8、FA B C ADE BDE ABC 的最简式为( A )。

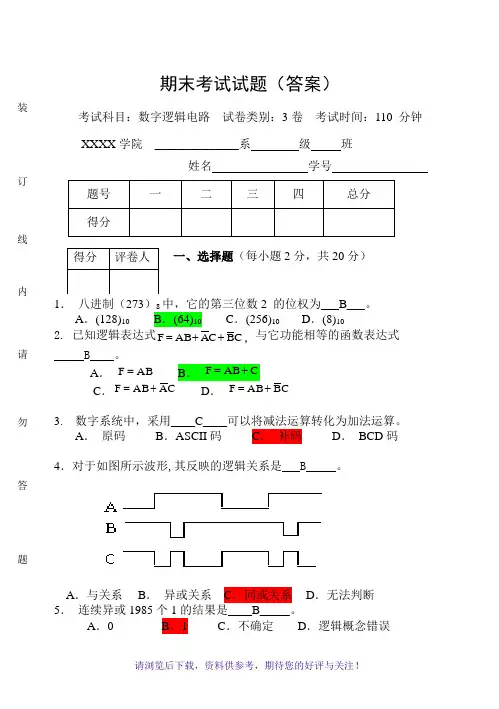

请浏览后下载,资料供参考,期待您的好评与关注!期末考试试题(答案)考试科目:数字逻辑电路 试卷类别:3卷 考试时间:110 分钟 XXXX 学院 ______________系 级 班姓名 学号题号 一 二 三 四 总分 得分一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10C .(256)10D .(8)102. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。

A .AB F = B .C AB F += C .C A AB F +=D . C B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断 5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误得分 评卷人装订线内请勿答题6. 与逻辑函数DCBAF+++=功能相等的表达式为___C_____。

DCBAF+++=B.DCBAF+++=D.DCBAF++=7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。

8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。

A. 500KHz B.200KHzC. 100KHz D.50KHz9.下列器件中,属于时序部件的是_____A_____。

A.计数器B.译码器C.加法器D.多路选择器装请浏览后下载,资料供参考,期待您的好评与关注!请浏览后下载,资料供参考,期待您的好评与关注!10.下图是共阴极七段LED 数码管显示译码器框图,若要显示字符“5”,则译码器输出a ~g 应为____C______。

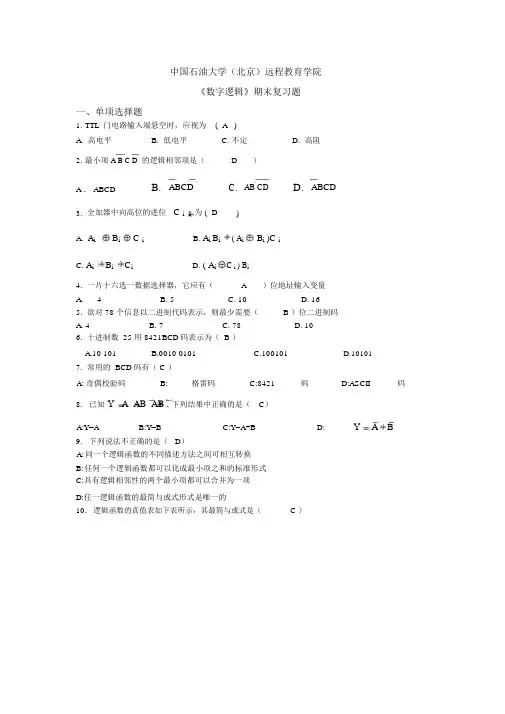

中国石油大学(北京)远程教育学院《数字逻辑》期末复习题一、单项选择题1.TTL 门电路输入端悬空时,应视为 ( A )A. 高电平B. 低电平C. 不定D. 高阻2. 最小项A B C D的逻辑相邻项是(D)A . ABCD B. ABCD C. AB CD D. ABCD3.全加器中向高位的进位 C i 1为( D)A. A i B i C iB. A i B i( A i B i )C iC. A i B i C iD. ( A i C i ) B i4.一片十六选一数据选择器,它应有(A)位地址输入变量A.4B. 5C. 10D. 165.欲对 78 个信息以二进制代码表示,则最少需要( B )位二进制码A. 4B. 7C. 78D. 106.十进制数 25 用 8421BCD码表示为( B )A.10 101B.0010 0101C.100101D.101017.常用的 BCD码有( C )A: 奇偶校验码B:格雷码C:8421码D:ASCII码8.已知 Y A AB AB ,下列结果中正确的是(C)A:Y=A B:Y=B C:Y=A+B D:Y A B 9.下列说法不正确的是( D)A:同一个逻辑函数的不同描述方法之间可相互转换B:任何一个逻辑函数都可以化成最小项之和的标准形式C:具有逻辑相邻性的两个最小项都可以合并为一项D:任一逻辑函数的最简与或式形式是唯一的10.逻辑函数的真值表如下表所示,其最简与或式是( C )A: ABC ABC ABC B: ABC ABC ABC C: BC ABD: BC AC11.以下不是逻辑代数重要规则的是( D ) 。

A. 代入规则B. 反演规则C. 对偶规则D. 加法规则12.已知函数 FAB (C DE)的反函数应该是 (A) 。

A. F A B C (D E)B. F A BC (DE)C. F A B C (D E)D.F A B C (DE)13.组合逻辑电路一般由(A)组合而成。

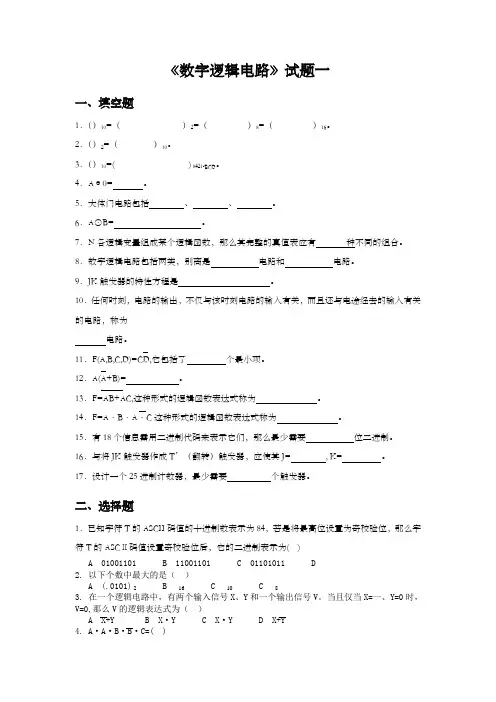

《数字逻辑电路》试题一一、填空题1.()10=()2=()8=()16。

2.()2=()10。

3.()10=( ) 8421-BCD。

4.A⊕0= 。

5.大体门电路包括、、。

6.A⊙B= 。

7.N各逻辑变量组成某个逻辑函数,那么其完整的真值表应有种不同的组合。

8.数字逻辑电路包括两类,别离是电路和电路。

9.JK触发器的特性方程是。

10.任何时刻,电路的输出,不仅与该时刻电路的输入有关,而且还与电途经去的输入有关的电路,称为电路。

11.F(A,B,C,D)=CD,它包括了个最小项。

12.A(A+B)= 。

13.F=AB+AC,这种形式的逻辑函数表达式称为。

14.F=A·B·A·C这种形式的逻辑函数表达式称为。

15.有18个信息需用二进制代码来表示它们,那么最少需要位二进制。

16.与将JK触发器作成T’(翻转)触发器,应使其J= , K= 。

17.设计一个25进制计数器,最少需要个触发器。

二、选择题1.已知字符T的ASCII码值的十进制数表示为84,若是将最高位设置为奇校验位,那么字符T的ASCⅡ码值设置奇校验位后,它的二进制表示为( )A 01001101B 11001101C 01101011 D2. 以下个数中最大的是()A (.0101) 2B 16C 10 C 83. 在一个逻辑电路中,有两个输入信号X、Y和一个输出信号V。

当且仅当X=一、Y=0时,V=0,那么V的逻辑表达式为()A X+YB X·YC X·YD X+Y4. A·A·B·B·C=( )A ABC C 1D 05. A+BC+AB+A=( )A AB AC 1D 06. F(A,B,C)=ABC+ABC+ABC=( )A ∑m(0,2,4)B ∑m(3,5,7)C ∑m(1,3,5)D ∑m(4,5,7)7. A⊕B=( )A AB+ AB B AB + ABC A BD A B8. 对正逻辑而言,某电路是与门,那么对负逻辑而言是()A 与门B 与非门C 或非门D 或门触发器在同步工作时,假设现态Q n=0,要求抵达次态Q n+1=1,那么应使JK=( )A 00B 01C 1XD X110.图(1)中要求输出F=B,那么A应为( )A 0B 1 A =1 FC B BD B 图(1)三、化简以下函数表达式一、代数化简:Y=(AB+A B+A B)(A+B+D+A B D)二、Y=AB+A B+A B3、卡诺图化简:F=(A,B,C,D)=∑m(0,1,2,3,4,6,8,9,10,11,12,14)四、芯片的应用1.别离用74138和74153实现逻辑函数表达式F=AB+BC+AC2.用1.用与非门设计一个组合电路,用来检测并行输入的四位二进制数B4B3B2B1当其值大于或等于5时,输出F=1,反之F=0。

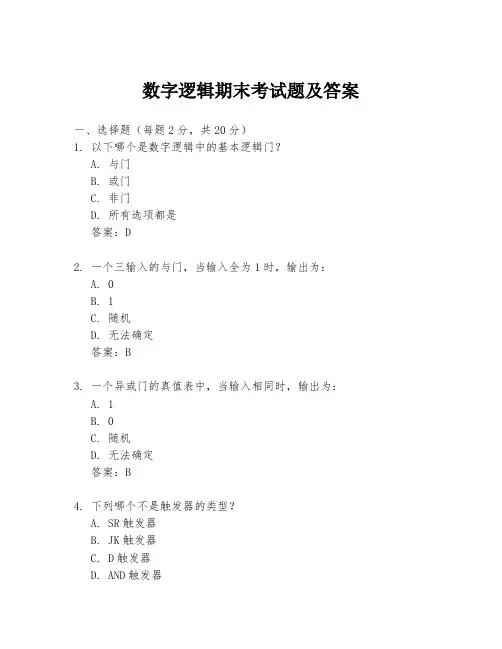

数字逻辑期末考试题及答案一、选择题(每题2分,共20分)1. 以下哪个是数字逻辑中的基本逻辑门?A. 与门B. 或门C. 非门D. 所有选项都是答案:D2. 一个三输入的与门,当输入全为1时,输出为:A. 0B. 1C. 随机D. 无法确定答案:B3. 一个异或门的真值表中,当输入相同时,输出为:A. 1B. 0C. 随机D. 无法确定答案:B4. 下列哪个不是触发器的类型?A. SR触发器B. JK触发器C. D触发器D. AND触发器答案:D5. 在数字电路中,同步计数器和异步计数器的主要区别在于:A. 计数范围B. 计数速度C. 计数精度D. 计数方式答案:B6. 一个4位二进制计数器,其最大计数值为:A. 15B. 16C. 32D. 64答案:A7. 以下哪个不是数字逻辑设计中常用的简化方法?A. 布尔代数简化B. 卡诺图简化C. 逻辑门替换D. 逻辑表简化答案:C8. 在数字电路中,一个信号的上升沿指的是:A. 信号从0变为1的瞬间B. 信号从1变为0的瞬间C. 信号保持不变D. 信号在变化答案:A9. 一个D触发器的Q输出端在时钟信号上升沿时:A. 保持不变B. 翻转状态C. 跟随D输入端D. 随机变化答案:C10. 以下哪个不是数字逻辑中的状态机?A. Moore机B. Mealy机C. 有限状态机D. 无限状态机答案:D二、填空题(每空2分,共20分)11. 在布尔代数中,逻辑与操作用符号______表示。

答案:∧12. 一个布尔函数F(A,B,C)=A∨B∧C的最小项为______。

答案:(1,1,1)13. 在数字电路设计中,卡诺图是一种用于______的工具。

答案:布尔函数简化14. 一个4位二进制加法器的输出端最多有______位。

答案:515. 一个同步计数器在计数时,所有的触发器都______时钟信号。

答案:接收16. 一个JK触发器在J=K=1时,其状态会发生______。

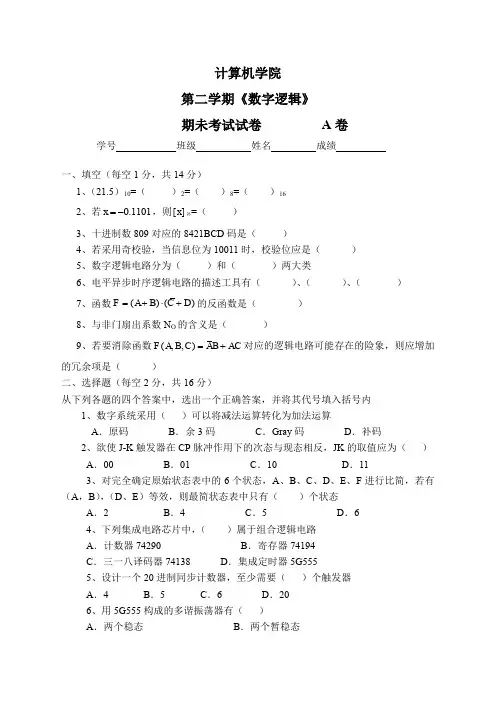

计算机学院 第二学期《数字逻辑》 期未考试试卷 A 卷学号 班级 姓名 成绩一、填空(每空1分,共14分)1、(21.5)10=( )2=( )8=( )162、若0.1101x =-,则[]x 补=( )3、十进制数809对应的8421BCD 码是( )4、若采用奇校验,当信息位为10011时,校验位应是( )5、数字逻辑电路分为( )和( )两大类6、电平异步时序逻辑电路的描述工具有( )、( )、( )7、函数()()F A B C D =+⋅+的反函数是( )8、与非门扇出系数N O 的含义是( )9、若要消除函数(,,)F A B C AB AC =+对应的逻辑电路可能存在的险象,则应增加的冗余项是( )二、选择题(每空2分,共16分)从下列各题的四个答案中,选出一个正确答案,并将其代号填入括号内1、数字系统采用( )可以将减法运算转化为加法运算A .原码B .余3码C .Gray 码D .补码2、欲使J-K 触发器在CP 脉冲作用下的次态与现态相反,JK 的取值应为( ) A .00 B .01 C .10 D .113、对完全确定原始状态表中的6个状态,A 、B 、C 、D 、E 、F 进行比简,若有(A ,B ),(D 、E )等效,则最简状态表中只有( )个状态A .2B .4C .5D .6 4、下列集成电路芯片中,( )属于组合逻辑电路 A .计数器74290 B .寄存器74194 C .三一八译码器74138 D .集成定时器5G555 5、设计一个20进制同步计数器,至少需要( )个触发器 A .4 B .5 C .6 D .20 6、用5G555构成的多谐振荡器有( )A .两个稳态B .两个暂稳态C .一个稳态,一个暂稳态D .既没有稳态,也没有暂稳态 7、可编程逻辑阵列PLA 的与、或陈列是( )A .与阵列可编程、或阵列可编程B .与阵列不可编程、或阵列可编程C .与阵列可编程、或阵列不可编程D .与阵列不可编程、或阵列不可编程 8、最大项和最小项的关系是( )A .i i m M =B .i i m M =C .1i i m M ⋅=D .无关系 三、逻辑函数化简(6分)把(,,,)(0,1,5,14,15)(4,7,10,11,12)F A B C D m d =∑+∑化成最简与—或式 四、分析题(每小题12分,共24分)1、分析图1所示组合逻辑电路① 写出输出函数表达式 ② 列出真值表 ③ 说明电路功能2、分析图2所示脉冲异步时序逻辑电路① 写出输出函数和激励函数表达式 ② 列出次态真值表,作出状态表和状态图 ③ 说明电路功能④ 设初态2100y y =,作出x 输入4个异步脉冲后的状态y 2y 1和输出z 的波形图。

院系: 专业班级: 学号: 姓名: 座位号:A. 4B. 3C. 6D. 57. 下列电路中属于时序逻辑电路的是 【 】A. 加法器B. 数据分配器C. 计数器D. 译码器8. 下列关于门电路的使用,描述不正确的是 【 】A. TTL 与非门闲置输入端可以直接接电源B. 具有推拉输出结构的TTL 门电路的输出端可以直接并联使用C. CMOS 或门闲置输入端应接地D. CMOS 门电路的闲置输入端不允许悬空 9. 为了降低555定时器组成多谐振荡器的振荡频率,外接R 、C 值应为 【 】A. 同时增大R 、C 值B. 同时减小R 、C 值C. 同比增大R 值减小C 值D. 同比增大C 值减小R 值 10. 若停电数分钟后恢复供电,下列选项中信息能够保持不变的是 【 】A. ROMB. 动态RAMC. MUXD. 静态RAM1. 8位D/A 转换器的理论分辨率是_____________________。

2. 64个输入端的编码器按二进制数编码时,输出端的个数是__________________。

3. 变量数相同时,下标编号相同的最大项i M 和最小项i m 的关系是_____________。

4. 图2.1所示集成计数器的模M=_____________________。

图2.1 (题2.4图)5. 共阳极接法数码显示器需要配用输出 电平有效的译码器。

二、填空题(每小题2分,共20分)。

6. 对于T 触发器,当T=______时,触发器处于保持状态。

7. 逻辑函数C B AB F +=的反函数F 为_____________________。

8. 5个变量的逻辑函数全部最大项有_____________________个。

9. 二进制数()20110.101110转换成十进制数是___________________。

10. 同步RS 触发器的特性方程中,约束条件为RS=0,说明这两个输入信号不能同时为_____________________。

试题一一、填空题。

(每空1分,共30分)。

1、(11001.01)2 =( )8=( )|6=( )102、十进制整数转换成二进制时采用 ______ 法;十进制小数转换成二进制时采用 _______ 法。

3、由三种最基本的逻辑关系有导出的几种常用的逻辑运算 ________ 、4、逻辑函数有四种表示方法,它们分别是 _______ 、_____ 、____ 和 _______ O5、消除竞争冒险的方法有 _____ 、______ 、_____ 等。

6、按逻辑功能分类,触发器可分为 _______ 、_______ 、________________ 等四种类型。

7、从结构上看,吋序逻辑电路的基本单元是 ___________ 。

8、J K触发器特征方程为____________ o9、A/D转换的一般步骤为:取样、 _______ 、_______ 、编码。

10、___________________________________________________ 一个EPROM有18条地址输入线,其内部存储单元有_____________ 个。

11、_____________________________ D/A转换器的主要参数有、和o12、__________________________________________________ 就逐次逼近型和双积分型两种A/D转换器而言,____________________ 的抗干扰能力强, _______ 的转换速度快。

二、选择题。

(每题1分,共15分)1、以下说法正确的是():(A)数字信号在大小上不连续,时间上连续,模拟信号则反之;(B)数字信号在大小上连续,时间上不连续,模拟信号则反之;(C)数字信号在大小和时间上均连续,模拟信号则反之;(D)数字信号在大小和吋间上均不连续,模拟信号则反之;2、A+BC=()。

(A)A+B (B) A+C (C) (A+B) (A+C) (D) B+C3、具有“有1出0、全0出1”功能的逻辑门是()。

《数字电路与数字逻辑》期末考试试卷考生注意:1.本试卷共有五道大题,满分100分。

2.考试时间90分钟。

3.卷面整洁,字迹工整。

1. 将下列二进制数转为十进制数(1010001)B = ( )D (11.101)B = ( )D 2. 将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码 (+254.25)=( )真值 = ( )原码=( )反码 = ( )补码3. 把下列4个不同数制的数(76.125)D 、(27A)H 、(10110)B 、(67)O 按从大到小的次序排列()>( )>( )>( ) 。

4. 对于D 触发器,欲使Q n+1=Q n,输入D=( ),对于T 触发器,欲使Q n+1=Q n,输入T=( )5. 一个512*8位的ROM 芯片,地址线为( )条,数据线为()条。

6. 对32个地址进行译码,需要( )片74138译码器。

7. 存储器起始地址为全0,256K*32的存储系统的最高地址为( )。

8. 将下列各式变换成最简与或式的形式=+B A ( )=+B A A ()=++C B C A AB ())进制。

二、组合电路设计题(每空10分,共20分)1. 用八选一数据选择器74LS151实现逻辑函数AC BC AB C B A L ++=),,( (10分) 2、用74LS138设计一个电路实现函数F = AB+ B C (提示:在74LS138的示意图上直接连线即可)(10分)三、组合电路分析题(共10分) 已知逻辑电路如下图所示,分析该电路的功能。

四、分析题(共24分) 1、分析如下的时序逻辑电路图,画出其状态表和状态图,并画出Q1,Q2的波形图,Q1Q2初态为00。

(14分)2、电路如图所示,要求写出它们的输出函数表达式,化简,并说出它们的逻辑功能。

(10分)五、设计题(共26分)1.用JK 触发器设计一个“111”序列检测器,允许重复,要求用一个输出信号来表示检测结果。

数字逻辑期末考试试卷含答案一、选择题(共10题,每题2分,共20分)在下列选项中选择正确答案,并在答题卡上填写对应答案的字母。

1. 逻辑门是数字电路中最基本的组成单元,它由多个电子器件组合而成,能够实现逻辑运算。

下列不属于逻辑门的是:A. 与门B. 或门C. 非门D. 电容门2. 在数字电路中,最简单的存储单元是:A. 寄存器B. 计数器C. 缓存器D. 锁存器3. 二进制数是由二个字符0和1组成的数,它在计算机中占有重要地位。

下面哪个是5的十进制表示?A. 101B. 0101C. 110D. 00001014. 半加器是指具有两个输入端和两个输出端的二进制加法器。

下列选项中,不属于半加器的是:A. 异或门B. 与门C. 或门D. 非门5. 在数字电路中,集成电路是指将多个电子器件集成到一个芯片上,以实现特定功能。

下列选项中不属于集成电路的是:A. 与门B. 或门C. 霍尔开关D. 计数器6. 在计算机中,ALU指的是运算器,负责进行各种算术和逻辑运算。

下面哪个选项不属于ALU的功能?A. 加法运算B. 乘法运算C. 与门逻辑运算D. 异或门逻辑运算7. 时钟信号是数字电路中常见的同步信号,用于控制电路的工作时间。

下列选项中,不属于时钟信号的是:A. 脉冲信号B. 方波信号C. 高电平信号D. 低电平信号8. 译码器是指将输入的数字代码转换为特定信号输出,用于对输入数字进行解码。

下面哪个选项不属于译码器?A. 74LS138B. 74LS74C. 74LS47D. 74LS869. 在数字电路中,多路选择器是一种常用的逻辑电路,具有多个输入和一个输出。

下列选项中不属于多路选择器的是:A. 2:1选择器B. 4:1选择器C. 8:1选择器D. 16:1选择器10. D触发器是一种常用的时序元件,能够存储一个比特的数据。

下列选项中,不属于D触发器的是:A. RS触发器B. JK触发器C. T触发器D. D触发器与门二、填空题(共5题,每题4分,共20分)根据题目所给条件,在答题卡上填写正确的答案。

数电期末考试题及答案一、选择题(每题2分,共20分)1. 以下哪个不是数字电路的特点?A. 精度高B. 抗干扰能力强C. 体积大D. 可靠性高答案:C2. 数字信号的特点是什么?A. 连续变化B. 离散变化C. 模拟变化D. 随机变化答案:B3. 逻辑门电路中最基本的逻辑关系是?A. ANDB. ORC. NOTD. XOR答案:C4. 下列哪个不是组合逻辑电路的特点?A. 输出只依赖于当前输入B. 输出与输入之间存在时延C. 没有记忆功能D. 可以进行复杂的逻辑运算答案:B5. 触发器的主要功能是什么?A. 放大信号B. 存储信息C. 转换信号D. 滤波答案:B6. 以下哪个不是数字电路设计中的优化目标?A. 减小功耗B. 提高速度C. 增加成本D. 减少面积答案:C7. 在数字电路中,同步信号的主要作用是什么?A. 同步时钟B. 同步数据C. 同步电源D. 同步信号源答案:A8. 以下哪个是数字电路中的时序逻辑电路?A. 门电路B. 触发器C. 计数器D. 译码器答案:C9. 以下哪个不是数字电路中的编码方式?A. 二进制编码B. 格雷码编码C. 十进制编码D. BCD编码答案:C10. 以下哪个是数字电路中的存储元件?A. 电阻B. 电容C. 电感D. 逻辑门答案:B二、填空题(每空2分,共20分)1. 数字电路中最基本的逻辑运算包括________、________和________。

答案:与、或、非2. 一个完整的数字系统通常包括________、________、________和输入/输出设备。

答案:算术逻辑单元、控制单元、存储器3. 在数字电路中,________是用来表示信号状态的最小单位。

答案:位(bit)4. 一个二进制数的位数越多,其表示的数值范围________。

答案:越大5. 触发器的输出状态取决于________和________。

答案:当前输入、前一状态6. 同步计数器与异步计数器的主要区别在于________是否受时钟信号的控制。

学习中心/函授站_姓名答案+3225776615学号西安电子科技大学网络与继续教育学院2020 学年上学期《数字逻辑电路》期末考试试题(综合大作业)考试说明:1、大作业试题于2020 年4 月23 日公布,2020 年4 月24 日至2020 年5 月10 日在线上传大作业答卷(一张图片对应一张A4 纸答题纸),要求拍照清晰、上传完整;2、考试必须独立完成,如发现抄袭、雷同均按零分计;3、答案须用《西安电子科技大学网络与继续教育学院标准答题纸》手写完成,要求字迹工整、卷面干净。

一、单项选择题(每题 2 分,共 30 分)1、与(76)H 相等的数是[ ]。

A (76)OB (116)DC (76)D D (1110110)B2、(100011.1)B 的8421BCD 是[ ]。

A 00110101.0101B 00111000.1000C 00111000.0101D 100011.10003、或非门的输出完成F =A , 则多余输入端[ ]。

A 全部接高电平B 全部接低电平C 只需一个接地即可D 只需一个接高电平即可4、逻辑函F (ABC )=A ⋅B +AC 的最小项标准式为[ ]。

A F(ABC)= ∑(0,1,4,6)B F(ABC)= ∑(2,3,5,7)C F(ABC)= ∑(2,6,7)D F(ABC)= ∑(0,1,4,6)5、与AB+AC+B ⋅C 相等的表达式为[ ]。

A ACB ABC AB+ACD A+ B ⋅C6、函数F=(A B +C)(B+ACD )的对偶式函数表达式是[ ]。

A G=( A +B)·C +B ·A +C +DB G=A+B C+B·A +C +DC G=(A+B )·C+B·A +C +DD G=(A B )·C +(B+ A +C +D )7、逻辑函数A B C D 的逻辑相邻项是[ ]。

第1页,共8页第2页,共8页院系: 专业班级: 学号: 姓名: 座位号:20 -20 学年第 学期期末考试试卷《数字逻辑电路》(A )卷一、选择题(每小题2分,共20分)1、下列数中最大的数是 【D 】 A 、(3C )16 B 、(57)8C 、(70)10D 、(1110010)22、8个输入端的编码器按二进制数编码时,输出端的个数是 【B 】 A 、2个 B 、3个C 、4个D 、8个3、逻辑电路中的晶体管一般工作在【B 】A 、放大区B 、饱和区或截至区C 、截至区D 、饱和区4、同步时序电路和异步时序电路比较,其差异在于后者 【B 】 A 、没有触发器; B 、没有统一的时钟脉冲控制; C 、没有稳定状态; D 、输出只与内部状态有关;5、n 个变量的逻辑函数全部最大项的个数有 【C 】 A 、n B 、2n C 、2nD 、2n -16、555定时器的结构如图1.1所示,如果芯片的5脚悬空;RD =V CC =5V ,6脚输入4V 电压,2脚输入2V 电压,下列关于555电路说法正确的是 【 A 】U CC U CO U 6(TH)(TR)U oR D U 2放电端图1.1(题1.6图)A 、U O 输出低电平,放电开关V 1导通;B 、U O 输出高电平,放电开关V 1截止;C 、U O 输出低电平,放电开关V 1截止;D 、U O 输出高电平,放电开关V 1导通; 7、图1.2所示用74LS161(同步16进制计数器,Cr 异步清零端、LD 同步置数端、OC 进位输出端,P 、T 计数允许端)构成的计数器正确的说法是 【D 】A 、同步置数法组成的9进制计数器;B 、异步置数法组成的8进制计数器;C 、同步置数法组成的10进制计数器;D 、异步复位法组成的9进制计数器; 图1.2( 题1.7图) 8、要使由与非门组成的基本RS 触发器保持原状态不变,D S 、D R 端输入的信号应取 【A 】 A 、1==D D S RB 、10==D D S R 、C 、01==D DS R 、 D 、0==D D S R9、为获得输出频率非常稳定的脉冲信号,应采用 【C 】A 、对称多谐振荡器B 、555定时器组成的对称多谐振荡器第3页,共8页第4页,共8页装订线内不许答题 C 、石英晶体振荡器 D 、单稳态触发器 10、下列关于TTL 与非门闲置输入端的处理不正确的是 【D 】 A 、直接接电源电压VccB 、与有用输入端并联使用C 、外界干扰小时,可以剪断或悬空D 、直接接地1、二进制数-110011的补码是 1001101 。

.数字逻辑考试题数字逻辑考试题(一)一、填空(共17分,每空1分)1. (1011.11)B =( ) D =( )H2. (16)D =( )8421BCD 码。

3. 三态门的输出有 、 、 三种状态。

6. ABC C B A Y =),,( 的最简式为Y= 。

7. 由n 位寄存器组成的扭环型移位寄存器可以构成 进制计数器。

10. 四位环型计数器初始状态是1000,经过5个时钟后状态为 。

11. 在RS 、JK 、T 和D 触发器中, 触发器的逻辑功能最多。

12. 设一个包围圈所包围的方格数目为S ,消去的变量数目为N ,那么S 与N 的关系式应是 。

13. 在卡诺图化简逻辑函数时,圈1求得 的最简与或式,圈0求得 的最简与或式。

二、选择(共10分,每题1分)1. DE BC A Y +=的反函数为Y =( )。

A. E D C B A Y +++⋅=B. E D C B A Y +++⋅=C. )(E D C B A Y +++⋅=D. )(E D C B A Y +++⋅=3. 十进制数25用8421BCD 码表示为( )。

A. 10101B. 0010 0101C. 100101D. 101014. 若用1表示高电平,0表示低电平,则是( )。

A. 正逻辑B. 负逻辑C. 正、负逻辑D. 任意逻辑5. 下逻辑图的逻辑表达式为( )。

A. AC BC AB Y =B. BC AC AB Y ++=C. BC AC AB Y ++=D. BC AC AB Y =6. 三态门的逻辑值正确是指它有( )。

A. 1个B. 2个C. 3个D. 4个9. 组合逻辑电路在电路结构上的特点下列不正确的是( )。

A. 在结构上只能由各种门电路组成B. 电路中不包含记忆(存储)元件C. 有输入到输出的通路D. 有输出到输入的反馈回路10. 已知74LS138译码器的输入三个使能端(E 1=1,022==B A E E )时,地址码A 2A 1A 0=011,则输出07~Y Y 为( )。

t h数字逻辑电路 3卷答案 第 1 页 共 8 页期末考试试题(答案)考试科目:数字逻辑电路 试卷类别:3卷 考试时间:110 分钟XXXX 学院 ______________系级班姓名学号 题号一二三四总分得分一、选择题(每小题2分,共20分)1. 八进制(273 2 的位权为___B___。

A .(128)10 C .(256)10 D .(8)102. C B +,与它功能相等的函数表达式_____B____。

A .AB F = B .C AB F += C .C A AB F +=D . B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误得分评卷人装 订 线 内 请 勿答 题数字逻辑电路 3卷答案 第 2 页 共 8 页6. 功能相等的表达式为___C_____。

B .D C B A F +++=D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=;C=1时,F 为高阻态的逻AB 辑功能的是____A______。

8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。

A . 500KHzB .200KHzC . 100KHzD .50KHz 9.下列器件中,属于时序部件的是_____A_____。

A . 计数器B . 译码器C . 加法器D .多路选择器装a n t数字逻辑电路 3卷答案 第 3 页 共 8 页10.下图是共阴极七段LED 数码管显示译码器框图,若要显示字符“5”,则译码器输出a ~g 应为____C______。

《数字逻辑电路》期末考试试题

一、单项选择题(本大题共15小题,每小题2分,共30分) 1.下列数中最小的数是

A .(1000.1)2

B .(10.3)8

C . (8.3)10

D .(8.3)16 2.与(77)8相等的8421BCD 码数是

A .(01110111)85421BCD

B .(01100011)8421BCD

C .(10010011)8421BC

D D .(10010110)8421BCD

3.已知输入A 、B 和输出F 的波形如图1.1所示,由此判断F 与A 、B 的逻辑关系是 A .或非 B .异或 C .与非 D .同或

4.在下列电路中,能实现C AB F +=的电路是

5.函数C B A C B D C B A F ⋅+++=)(的反函数是 A .[]

C B A C B

D C B A F +++++=))(( B .[]C B A C B D C B A F +++++=))((

C .[]C B A C

D B C B A F ++++++=

D .

[]

C B A C B

D C B A F +++++=)(

6.与函数AD D C C A F ++=相等的函数式是

A .C A F =

B .D

C F = C .A

D C F += D .AD F = 7.已知函数C B A F ++=,问使函数0=F 的输入组合是

A B C A B C

A B

C

D

A

B F

图1.1

A .ABC=001

B .ABC=110

C .ABC=000

D .ABC=010 8.逻辑项CD B A ,其逻辑相邻项的是

A .BCD A

B .D B

C A C .

D C AB D .D C B A 9.逻辑函数D B A D AB D BC CD F +++=的最简与或式是 A .F CD BD =+ B .F CD BD =+ C .F BD CD =+ D .F BD CD =+

10.逻辑函数C B C A F +⋅=,其约束条件为0=AB ,它的最简与或非式是 A . F A C B C =+++ B . F A C B C =+++ C .F A C B C =+++ D .F A C B C =+++ 11.函数∑=

)15,13,12,9,8,7,5,1(F 的最简与或式是

A .D A C

B D

C F ⋅++= B .

D B D C C A F ⋅++= C .BD D C C A F ++= D .AD C B D C F ++= 12.D 触发器置1,其激励端D 的取值为

A .0=D

B .1=D

C .n Q

D = D .1

+=n Q D

13.T 触发器组成电路如图1.2所示,它完成的功能是 A .T 触发器 B .JK 触发器 C .D 触发器 D .RS 触发器 14.n 位DAC 电路的精度为

A .121-n

B .12

1-n C .n 2 D .12-n

15.555定时电路当R d =0时,其输出状态为

A .保持

B .对输出无影响

C .1

D .0

二、填空题(本大题共5小题,每小题2分,共10分) 16.余3BCD 码0111表示的十进制数是 。

17、1⊕⊕=A A F = 。

A

图1.2

18、5级触发器组成扭环型计数器,其无效状态数有。

19、将模拟量转换为数字量一般要经过采样保持和两部分电路。

20、为了检测出输入幅值大于某值的脉冲信号,应采用电路

三、分析题(本大题共4小题,每小题10分,共40分)

说明:中规模器件74LS90、74LS161和74LS194的功能表在第8页上。

21.数据选择器电路如图3.1所示

①写出F表达式;②填写出卡诺图;③写出最简与非式。

22.时序电路如图2.2所示。

①写出触发器的次态方程;②画出Q的波形(设Q初态为0)。

23.由74LS1和74LS194组成电路如图3.4(a)、(b)所示

①分别列出它们的状态迁移关系;(74LS194起始态为0000)

②指出其功能。

C

D

图3.1 A

CP

A

图2.2

cp

1

CP

11010

24.由译码器74LS138和计数器74LS161组成电路如图2.4所示。

① 列出74LS161的状态迁移关系; ② 列出输出F 的序列信号。

四、设计题(本大题共2小题,每小题10分,共20分)

25.用译码器和少量的门电路设计一个一位二进制数的全减器。

(A 为被减数,B 为减数,D 为差,C i 为低位的借位,C i +1为向高位的借位) ①作出真值表; ②写出方程式; ③画出逻辑图。

26.用74LS90设计七进制5421BCD 码计数器。

① 列出状态迁移关系; ② 决定反馈归零信号; ③ 画出逻辑图。

74LS90功能表输入输出R 01R 02S 91S 92CP 1CP 2

11111111

00

R 01R 02=0S 91S 92=000Q D Q A

二进制计数五进制计数

8421码十进制计数5421码十进制计数

Q A Q B Q C Q D 00000000100110

01

CP CP CP

CP

1

图2.4

74LS194功能表

74LS161功能表。