74LS74触发器知识讲解

- 格式:doc

- 大小:87.00 KB

- 文档页数:5

74LS74是一种双D型触发器,通过连接多个74LS74芯片可以构成四位移位寄存器。

以下是四位移位寄存器的工作原理:

1. 每个74LS74芯片有两个D输入端(D1和D2)和两个时钟输入端(CLK1和CLK2),以及两个输出端(Q和/ Q)。

2. 首先,将时钟信号(例如,CLK1)连接到第一个74LS74芯片的时钟输入端(CLK1)。

这个时钟信号用于控制数据的移位操作。

3. 将待存储的四位数据输入到四个74LS74芯片的D1输入端。

每个芯片都存储一个位。

4. 当时钟信号的边沿(上升沿或下降沿)到达时,数据会从D1输入端传输到Q 输出端,并且会被传递到下一个74LS74芯片的D2输入端。

5. 这样,数据会在四个74LS74芯片之间进行移位,最终被存储在最后一个74LS74芯片的Q输出端。

6. 如果需要从寄存器中读取数据,可以通过读取每个74LS74芯片的Q输出端来获取各个位的值。

7. 如果需要清除寄存器中的数据,可以将清除信号(CLR)连接到每个74LS74芯片的清除输入端(CLR)。

通过控制时钟信号的边沿和输入数据,可以实现数据的移位和存储操作。

这样,四个74LS74芯片组成的四位移位寄存器就能够完成数据的移位和存储功能。

1。

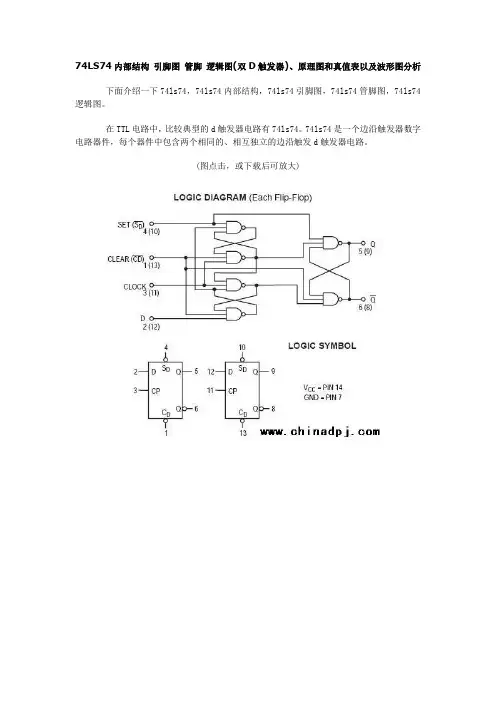

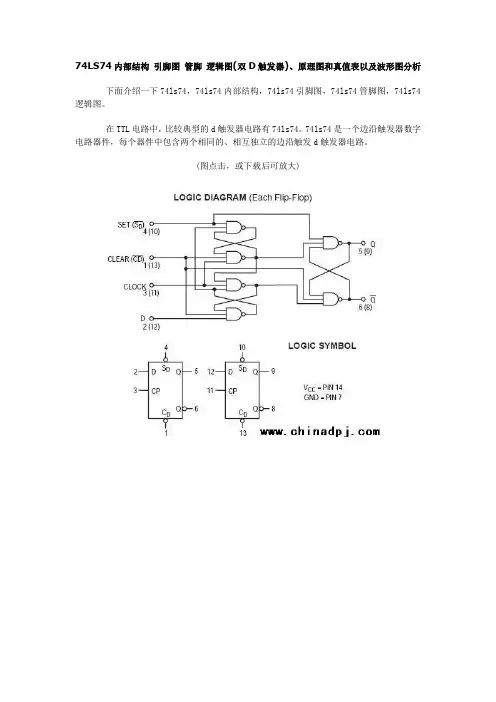

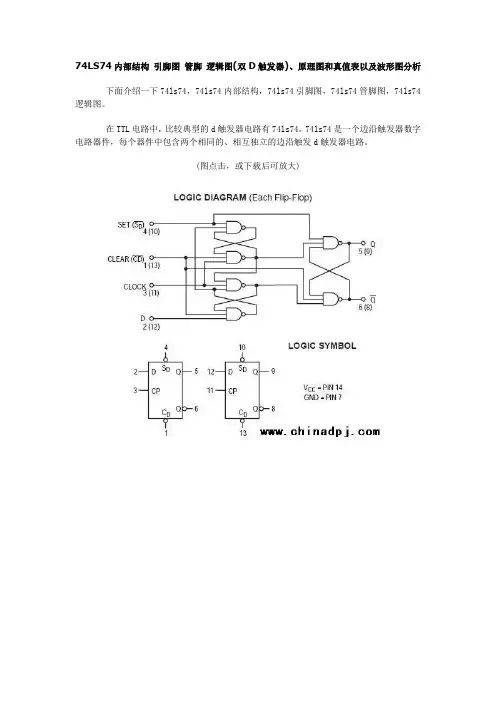

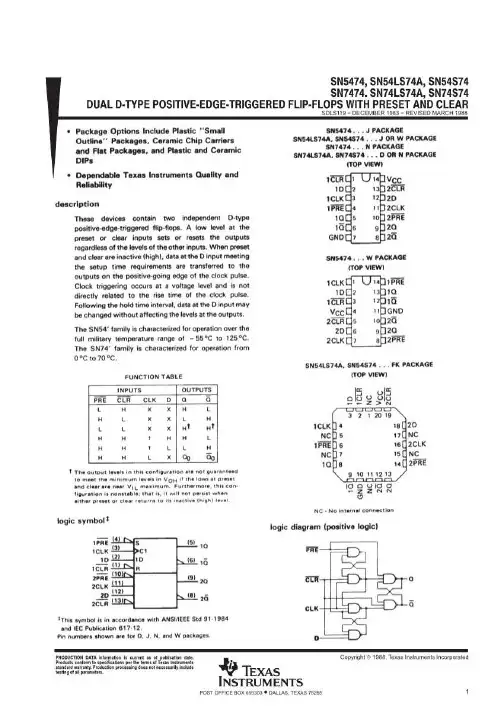

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

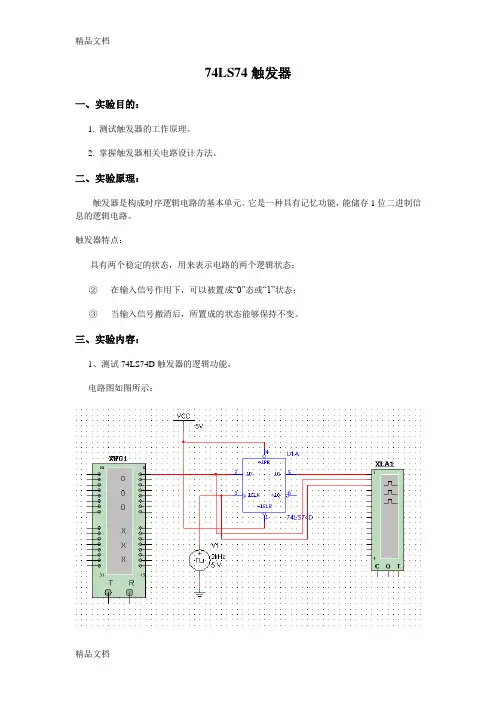

74LS74触发器一、实验目的:1. 测试触发器的工作原理。

2. 掌握触发器相关电路设计方法。

二、实验原理:触发器是构成时序逻辑电路的基本单元。

它是一种具有记忆功能,能储存1位二进制信息的逻辑电路。

触发器特点:具有两个稳定的状态,用来表示电路的两个逻辑状态;②在输入信号作用下,可以被置成“0”态或“1”状态;③当输入信号撤消后,所置成的状态能够保持不变。

三、实验内容:1、测试74LS74D触发器的逻辑功能。

电路图如图所示:字发生器内参:逻辑分析仪分析图:2、测试74LS76JK触发器的逻辑功能,并将其填入下表。

电路图如图所示:字发生器内参:逻辑分析仪分析图:3、思考题:试设计一个3人抢答器,要求如下:每位参赛者有一个按钮;主持人有一个复位按钮,能够完成电路的复位;当其中一位参赛者按动按钮对应的数码管亮之后,其他参赛者再按动按钮无效。

设计说明:当其中一个触发器工作时,~1Q端输出低电平,与该端相连的LED发光,数码管显示相应的数字(1、2、3)。

这时该低电平将与非门锁住,使时钟脉冲无法到达各触发器,其他触发器便不能工作。

当给清零信号时,~1Q端输出高电平,与该端相连的LED 熄灭,数码管显示0,与非门重新打开,时钟脉冲进入各触发器。

如此循环,就达到了设计要求。

电路设计图如下:四、实验分析:1、通过实验,进一步熟悉了触发器的原理。

2、能利用触发器进行简单的电路设计,如抢答器。

3、在进行实验设计时,查阅相关资料很重要。

在对所得资料进行自己的改进,就得到了自己的设计电路。

在设计抢答器时,我在资料上找到了用LED显示的设计电路,经过思考,我加进了数码管显示器,这样就使的显示结果更直观,更具有实用性。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

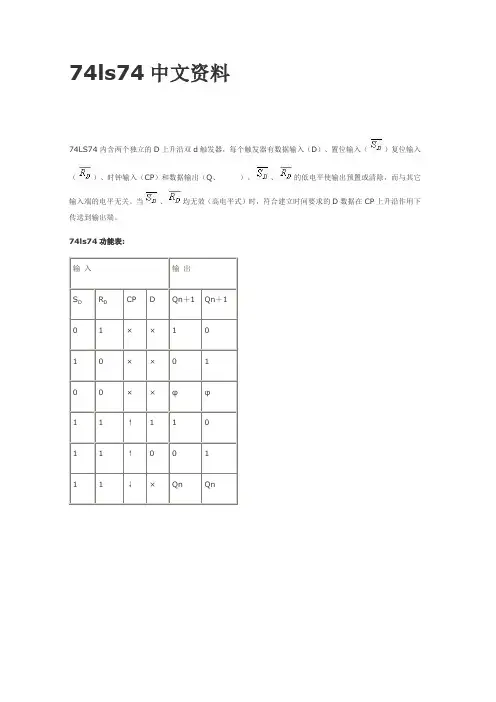

74ls74中文资料74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:输入输出S D R D CP D Qn+1 Qn+10 1 ×× 1 01 0 ××0 10 0 ××φ φ1 1 ↑ 1 1 01 1 ↑0 0 11 1 ↓×Qn Qn图1 74ls74引脚图实验:用74LS74构成4位寄存器一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;(3) 先清零;(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

并入并出:D3D2D1D0=10111个CP脉冲Q3Q2Q1Q0=结论:并入串出D3D2D1D0=10114个CP脉冲Q3=结论串入并出D3=10114个CP脉冲Q3Q2Q1Q0=结论串入串出D3=10118个CP脉冲Q3=结论图274ls153芯片管脚图引脚逻辑功能以及封装2007年12月17日 23:53 本站原创作者:本站用户评论()关键字:74ls153管脚图逻辑功能图封装:74LS163引脚功能表及管脚定义图(带时序波形图)发布:2011-08-30 | 作者: | 来源: huangjiapeng| 查看:2620次 | 用户关注:定时器由与系统秒脉冲(由时钟脉冲产生器提供)同步的计数器构成,要求计数器在状态信号ST作用下,首先清零,然后在时钟脉冲上升沿作用下,计数器从零开始进行增1计数,向控制器提供模5的定时信号TY和模25的定时信号TL。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

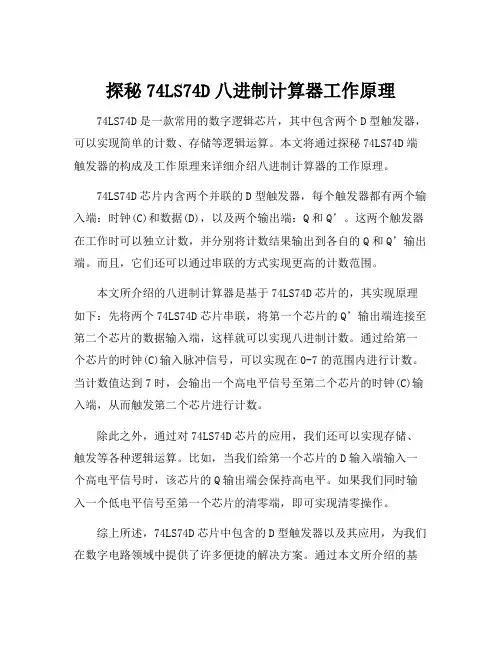

探秘74LS74D八进制计算器工作原理

74LS74D是一款常用的数字逻辑芯片,其中包含两个D型触发器,可以实现简单的计数、存储等逻辑运算。

本文将通过探秘74LS74D端触发器的构成及工作原理来详细介绍八进制计算器的工作原理。

74LS74D芯片内含两个并联的D型触发器,每个触发器都有两个输入端:时钟(C)和数据(D),以及两个输出端:Q和Q’。

这两个触发器在工作时可以独立计数,并分别将计数结果输出到各自的Q和Q’输出端。

而且,它们还可以通过串联的方式实现更高的计数范围。

本文所介绍的八进制计算器是基于74LS74D芯片的,其实现原理如下:先将两个74LS74D芯片串联,将第一个芯片的Q’输出端连接至第二个芯片的数据输入端,这样就可以实现八进制计数。

通过给第一个芯片的时钟(C)输入脉冲信号,可以实现在0-7的范围内进行计数。

当计数值达到7时,会输出一个高电平信号至第二个芯片的时钟(C)输入端,从而触发第二个芯片进行计数。

除此之外,通过对74LS74D芯片的应用,我们还可以实现存储、触发等各种逻辑运算。

比如,当我们给第一个芯片的D输入端输入一个高电平信号时,该芯片的Q输出端会保持高电平。

如果我们同时输入一个低电平信号至第一个芯片的清零端,即可实现清零操作。

综上所述,74LS74D芯片中包含的D型触发器以及其应用,为我们在数字电路领域中提供了许多便捷的解决方案。

通过本文所介绍的基

于74LS74D的八进制计算器,相信您对其工作原理有了更深入的了解,能够更好地应用于实际工程中。

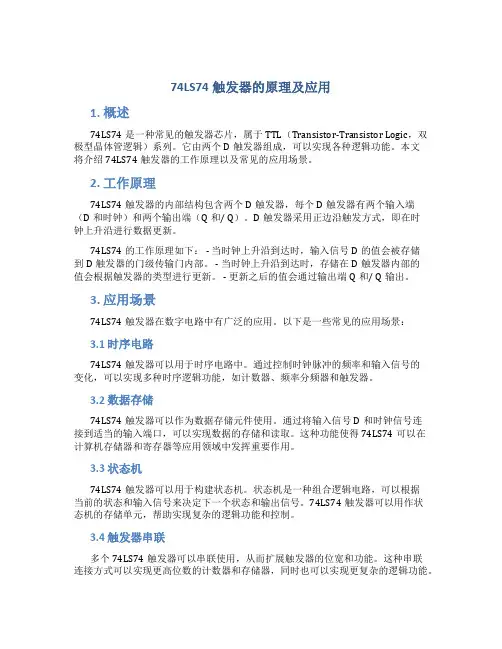

74LS74触发器的原理及应用1. 概述74LS74是一种常见的触发器芯片,属于TTL(Transistor-Transistor Logic,双极型晶体管逻辑)系列。

它由两个D触发器组成,可以实现各种逻辑功能。

本文将介绍74LS74触发器的工作原理以及常见的应用场景。

2. 工作原理74LS74触发器的内部结构包含两个D触发器,每个D触发器有两个输入端(D和时钟)和两个输出端(Q和/ Q)。

D触发器采用正边沿触发方式,即在时钟上升沿进行数据更新。

74LS74的工作原理如下: - 当时钟上升沿到达时,输入信号D的值会被存储到D触发器的门级传输门内部。

- 当时钟上升沿到达时,存储在D触发器内部的值会根据触发器的类型进行更新。

- 更新之后的值会通过输出端Q和/ Q输出。

3. 应用场景74LS74触发器在数字电路中有广泛的应用。

以下是一些常见的应用场景:3.1 时序电路74LS74触发器可以用于时序电路中。

通过控制时钟脉冲的频率和输入信号的变化,可以实现多种时序逻辑功能,如计数器、频率分频器和触发器。

3.2 数据存储74LS74触发器可以作为数据存储元件使用。

通过将输入信号D和时钟信号连接到适当的输入端口,可以实现数据的存储和读取。

这种功能使得74LS74可以在计算机存储器和寄存器等应用领域中发挥重要作用。

3.3 状态机74LS74触发器可以用于构建状态机。

状态机是一种组合逻辑电路,可以根据当前的状态和输入信号来决定下一个状态和输出信号。

74LS74触发器可以用作状态机的存储单元,帮助实现复杂的逻辑功能和控制。

3.4 触发器串联多个74LS74触发器可以串联使用,从而扩展触发器的位宽和功能。

这种串联连接方式可以实现更高位数的计数器和存储器,同时也可以实现更复杂的逻辑功能。

4. 总结74LS74触发器是一种常见的数字电路元件,具有广泛的应用场景。

本文介绍了74LS74触发器的工作原理以及常见的应用场景,包括时序电路、数据存储、状态机和触发器串联等。

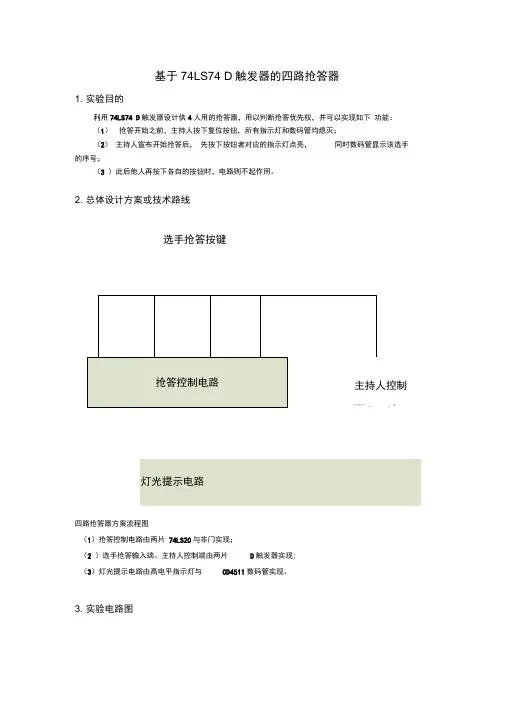

基于74LS74 D触发器的四路抢答器1. 实验目的利用74LS74 D触发器设计供4人用的抢答器,用以判断抢答优先权,并可以实现如下功能:(1)抢答开始之前,主持人按下复位按钮,所有指示灯和数码管均熄灭;(2)主持人宣布开始抢答后,先按下按钮者对应的指示灯点亮,同时数码管显示该选手的序号;(3 )此后他人再按下各自的按钮时,电路则不起作用。

2. 总体设计方案或技术路线选手抢答按键四路抢答器方案流程图(1)抢答控制电路由两片74LS20与非门实现;(2 )选手抢答输入端、主持人控制端由两片D触发器实现;(3)灯光提示电路由高电平指示灯与CD4511数码管实现。

3. 实验电路图• ■--J4 r_l^z z■ ■=[厂1J - LJW+■MM 曲D 4V■ J3 “*一兀宀_£_K舒沖:1^1’ ::… ]°二]低|怙 ....5 y * ■>•■■>>亠二0 -Jf: - 74tiCpD 4V74HC2OD 4V二:ci加廿數勒管二■:::::F1二匸UT J:UTTW:-:44—V2V2.—J5・■ ■ «—>< -fl—r -蘭=n L■U3A• -1EEtu--E器Q -T^l MJ---«sm ■-II -——WA^nri—…… i istF.酋•’ ■•■ a■ » - 8 -itr一-1CU ' 45.ICC- -M U L T I S I M 电路图4. 仪器设备名称、型号(1)直流稳压电源1台(2)EEL-6模拟、数字电子技术实验箱1台(3)74LS74 D 触发器2片(4)74LS20与非门2片(5)CD4511数码管4只(6 )导线若干5. 理论分析或仿真分析结果(1)主持人按下控制开关,将开关置于“清零”位置,D触发器置零,此时所有的指示灯和数码管均熄灭,选手按下按钮,指示灯和数码管均无任何反应;(2)主持人将开关置于“1”位置,指示灯亮,发出答题信号,此时,选手按下相应的按钮,指示灯亮,数码管显示选手的序号,并且优先作答者对应的74LS20与非门的输出将封锁其他选手的信号的输出,使其按钮不发挥作用,直到主持人再次清除信号为止;(3)主持人再次清零后,进入下一个答题周期。

74ls74分频原理74LS74是一种常用的分频器件,它可以将输入信号的频率降低为原来的一半。

它的分频原理基于触发器的工作方式和输出端的反馈连接。

本文将详细介绍74LS74的分频原理及其工作过程。

我们需要了解触发器的工作原理。

触发器是一种存储器件,可以将输入信号的状态保存下来,并根据特定条件改变其输出状态。

常见的触发器有D触发器和JK触发器,而74LS74是一种JK触发器。

JK触发器有两个输入端J和K,以及两个输出端Q和/ Q。

当J和K均为低电平时,触发器保持原来的状态;当J和K均为高电平时,触发器反转输出状态;而当J和K分别为高电平和低电平时,触发器将保持或改变原来的状态,取决于触发器的类型(正沿触发或负沿触发)。

在74LS74中,两个JK触发器被串联连接,形成一个双稳态触发器。

其中一个触发器的输出端连接到另一个触发器的时钟输入端,形成了反馈回路。

当输入信号的频率较高时,触发器将无法跟随输入信号的状态变化,而是被反馈回路所控制,使得输出信号的频率降低为一半。

具体来说,当输入信号为高电平时,触发器的输出状态会根据触发器的类型和当前状态来改变。

如果触发器是正沿触发的,并且当前状态为低电平,则输出状态将翻转为高电平;如果触发器是负沿触发的,并且当前状态为高电平,则输出状态将翻转为低电平。

反之,当输入信号为低电平时,触发器将保持原来的状态。

通过这种方式,74LS74可以将输入信号的频率降低为原来的一半。

例如,当输入信号频率为1kHz时,输出信号频率将为500Hz。

这种分频器件常用于数字电路中的时序控制和频率分割等应用。

总结一下,74LS74的分频原理是基于JK触发器的工作方式和输出端的反馈连接。

通过串联连接两个JK触发器并形成反馈回路,输入信号的频率可以被降低为一半。

这种分频器件在数字电路中具有广泛的应用,可以实现时序控制和频率分割等功能。

希望本文能够帮助读者了解74LS74的分频原理,并对其工作过程有一个清晰的认识。

54/7474双上升沿D触发器(有预置、清除端)简要说明74为带预置和清除端的两组D 型触发器,共有54/7474、54/74H74、54/74S74、54/74LS74四种线路结构形式,其主要电特性的典型值如下:型 号f max P D 5474/7474 25MHz 85mW 54H74/74H74 43 MHz 150mW 54S74/74S74 110 MHz 150mW 54LS74/74LS74 33 MHz 20mW引出端符号1CP 、2CP 时钟输入端 1D 、2D 数据输入端1Q 、2Q 、1Q _、2Q _输出端CLR1、CLR2 直接复位端(低电平有效) PR1、PR2 直接置位端(低电平有效) 逻辑图双列直插封装极限值电源电压………………………………………….7V 输入电压54/7474、54/74H74、54/74S74................5.5V 54/74LS74 (7V)ww w .t ai -ya n .c o m /bb s工作环境温度54XXX …………………………………. -55~125℃74XXX …………………………………. 0~70℃ 存储温度 ………………………………………….-65~150℃功能表推荐工作条件5474/7474 54H74/74H74 54S74/74S74 54LS74/74LS74最小 额定 最大 最小额定最大最小额定最大 最小 额定 最大单位544.5 55.5 4.5 5 5.5 4.5 5 5.5 4.5 5 5.5 电源电压Vcc74 4.75 5 5.25 4.75 5 5.25 4.75 5 5.25 4.75 5 5.25V输入高电平电压V IH2 2 2 2 V 540.8 0.8 0.8 0.7 输入低电平电V IL74 0.8 0.8 0.8 0.8 V输出高电平电流I OH -400 -1000 -1000 -400µA5416 20 20 4 输出低电平电流I OL74 16 20 20 8 mA时钟频率f CLK0 15 0 35 0 75 0 25 MHz CP(H) 30 15 6 25 CP(L) 37 13.5 7.3 脉冲宽度t WPR(L) CLR(L)30 25 7 25 ns D(H) 20* 10* 3* 20* 建立时间t SUD(L) 20* 15* 3* 20* ns 保持时间t H5* 5* 2* 5* ns *表示以CP 上升沿为参考静态特性(T A 为工作环境温度范围)‘74 ‘H74 ‘S74 ‘LS74参 数测 试 条 件【1】最小最大最小最大最小最大 最小 最大单位I ik =-8mA -1.5 I ik =-12mA -1.5 V IK 输入嵌位电压 Vcc=最小I ik =-18mA -1.2-1.5V 54 2.4 2.4 2.5 2.5 V OH 输出高电平电压 Vc =最小V IH =2V ,V IL=最大I OH =最大 74 2.4 2.4 2.7 2.7V54 0.4 0.4 0.5 0.4 V OL 输出低电平电压 Vcc=最小,V IL =最大,V IH =2V ,I OL =最大74 0.4 0.4 0.5 0.5 VI I 最大输入电压Vcc =最大D ,CP1 1 1 0.1 mA ww w .t ai -y a n .co m/bb s时输入电流V I =5.5V(‘LS74为7V) PR ,CLR1 1 1 0.2D 40 50 50 20CLR 120 150 150 40 PR 80 100 100 40 I IH 输入高电平电流Vcc =最大V IH =2.4V(‘S74和’LS74为2.7V)CP 80 100 100 20 uAD -1.6 -2 -2 -0.4CLR -3.2 -4 -6 -0.8PR -1.6 -2 -4 -0.8I IL 输入低电平电流Vcc =最大V IL =0.4V(‘S74为0.5V)CP -3.2 -4 -4 -0.4mA 54 -20 -57 -40 -100-40 -100 -20 -100I OS 输出短路电流 Vcc =最大74 -18 -57 -40 -100-40 -100 -20 -100mA 54 30 42 50 8 mAI CC 电源电流 Vcc =最大,CP 接地,Q 和Q _分别接高电平74 30 50 50 8 mA[1]: 测试条件中的“最小”和“最大”用推荐工作条件中的相应值。

74ls74中文资料74ls74中文资料74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:输入输出S D R D CP D Qn+1 Qn+10 1 ×× 1 01 0 ××0 10 0 ××φ φ1 1 ↑ 1 1 01 1 ↑0 0 11 1 ↓×Qn Qn图1 74ls74引脚图实验:用74LS74构成4位寄存器一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;(3) 先清零;(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:使数据输入端D0分别为1011,同时通过给CP 端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:使数据输入端D0分别为1011,同时通过给CP 端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

并入并出:D3D2D1D0=10111个CP脉冲Q3Q2Q1Q0=结论:并入串出D3D2D1D0=10114个CP脉冲Q3=结论串入并D3=10114个CQ3Q2Q1Q0=结论出P 脉冲串入串出D3=1011 8个C P 脉冲Q3= 结论图274ls153芯片管脚图引脚逻辑功能以及封装2007年12月17日 23:53 本站原创 作者:本站 用户评论()关键字:74ls153管脚图逻辑功能图封装:74LS163引脚功能表及管脚定义图(带时序波形图)发布:2011-08-30 | 作者: | 来源: huangjiapeng| 查看:2620次 | 用户关注:定时器由与系统秒脉冲(由时钟脉冲产生器提供)同步的计数器构成,要求计数器在状态信号ST作用下,首先清零,然后在时钟脉冲上升沿作用下,计数器从零开始进行增1计数,向控制器提供模5的定时信号TY和模25的定时信号TL。

74ls74原理74LS74原理。

74LS74是一款集成电路,属于74系列逻辑芯片,它是一种双D触发器,内部包含两个独立的D触发器。

在数字电子电路中,触发器是一种用于存储和传输数据的元件,它可以在时钟信号的作用下,按照特定的规则改变输出状态。

而74LS74作为一种常用的数字逻辑芯片,广泛应用于各种数字电路中。

首先,我们来看一下74LS74的引脚功能。

74LS74一共有14个引脚,其中包括两个D输入端(分别为1D和2D)、两个时钟输入端(分别为1CLK和2CLK)、两个清零输入端(分别为1CLR和2CLR)、两个置位输入端(分别为1PR和2PR)、两个输出端(分别为1Q和2Q)、两个输出使能端(分别为1G和2G)以及一个共用的地端和电源端。

通过这些引脚,我们可以将74LS74与其他元器件连接起来,构建出各种不同的数字逻辑电路。

接下来,我们来了解一下74LS74的工作原理。

当时钟信号到来时,根据D输入端的电平状态,74LS74会根据特定的规则改变输出状态。

具体来说,当时钟信号上升沿到来时,如果D输入端为高电平,则输出端Q会被置为高电平;如果D输入端为低电平,则输出端Q会被置为低电平。

而当时钟信号下降沿到来时,输出端Q的状态将会被保持不变。

通过这样的工作原理,我们可以利用74LS74来实现各种数字逻辑功能,比如寄存器、计数器、触发器等。

此外,74LS74还具有清零和置位的功能。

当清零端接收到低电平信号时,输出端Q会被强制置为低电平;当置位端接收到低电平信号时,输出端Q会被强制置为高电平。

这两个功能可以使我们在特定情况下对74LS74进行初始化操作,确保其处于我们需要的状态。

总的来说,74LS74作为一种双D触发器,具有简单的引脚功能和清晰的工作原理,可以方便地用于各种数字逻辑电路中。

它的性能稳定可靠,被广泛应用于计算机、通信、工业控制等领域。

通过对74LS74的深入了解,我们可以更好地利用它来设计和实现各种数字电路,从而满足不同应用场景的需求。

74LS74 内部结构引脚图管脚逻辑图(双 D 触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74 ,74ls74 内部结构,74ls74 引脚图,74ls74 管脚图,74ls74 逻辑图。

在TTL 电路中,比较典型的 d 触发器电路有74ls74 。

74ls74 是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发 d 触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)原理图和真值表以及波形图分析边沿 D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿 D 触发器也称为维持- 阻塞边沿 D 触发器。

电路结构: 该触发器由 6 个与非门组成,其中G1 和G2 构成基本RS 触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD =0 且RD=1 时,不论输入端 D 为何种状态,都会使Q=1 ,Q=0 ,即触发器置 1 ;当SD=1 且RD=0 时,触发器的状态为0,SD 和RD 通常又称为直接置 1 和置0 端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1. CP=0 时,与非门G3 和G4 封锁,其输出Q3=Q4=1 ,触发器的状态不变。

同时,由于Q3 至Q5 和Q4 至Q6 的反馈信号将这两个门打开,因此可接收输入信号 D ,Q5=D ,Q6=Q5=D 。

2. 当CP由0变1时触发器翻转。

这时G3 和G4 打开,它们的输入Q3 和Q4 的状态由G5 和G6 的输出状态决定。

Q3=Q5=D ,Q4=Q6=D 。

由基本RS 触发器的逻辑功能可知,Q =D 。

3. 触发器翻转后,在CP=1 时输入信号被封锁。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD =0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6 =Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q =D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q 3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

74LS74触发器

一、实验目的:

1. 测试触发器的工作原理。

2. 掌握触发器相关电路设计方法。

二、实验原理:

触发器是构成时序逻辑电路的基本单元。

它是一种具有记忆功能,能储存1位二进制信息的逻辑电路。

触发器特点:

具有两个稳定的状态,用来表示电路的两个逻辑状态;

②在输入信号作用下,可以被置成“0”态或“1”状态;

③当输入信号撤消后,所置成的状态能够保持不变。

三、实验内容:

1、测试74LS74D触发器的逻辑功能。

电路图如图所示:

字发生器内参:

逻辑分析仪分析图:

2、测试74LS76JK触发器的逻辑功能,并将其填入下表。

电路图如图所示:

字发生器内参:

逻辑分析仪分析图:

3、思考题:

试设计一个3人抢答器,要求如下:

每位参赛者有一个按钮;主持人有一个复位按钮,能够完成电路的复位;当其中一位参赛者按动按钮对应的数码管亮之后,其他参赛者再按动按钮无效。

设计说明:当其中一个触发器工作时,~1Q端输出低电平,与该端相连的LED发光,数码管显示相应的数字(1、2、3)。

这时该低电平将与非门锁住,使时钟脉冲无法到达各触发器,其他触发器便不能工作。

当给清零信号时,~1Q端输出高电平,与该端相连的LED 熄灭,数码管显示0,与非门重新打开,时钟脉冲进入各触发器。

如此循环,就达到了设计要求。

电路设计图如下:

四、实验分析:

1、通过实验,进一步熟悉了触发器的原理。

2、能利用触发器进行简单的电路设计,如抢答器。

3、在进行实验设计时,查阅相关资料很重要。

在对所得资料进行自己的改进,就得到了自己的设计电路。

在设计抢答器时,我在资料上找到了用LED显示的设计电路,经过思考,我加进了数码管显示器,这样就使的显示结果更直观,更具有实用性。