AD中关于差分线的设置和走线的方法

- 格式:pdf

- 大小:542.59 KB

- 文档页数:7

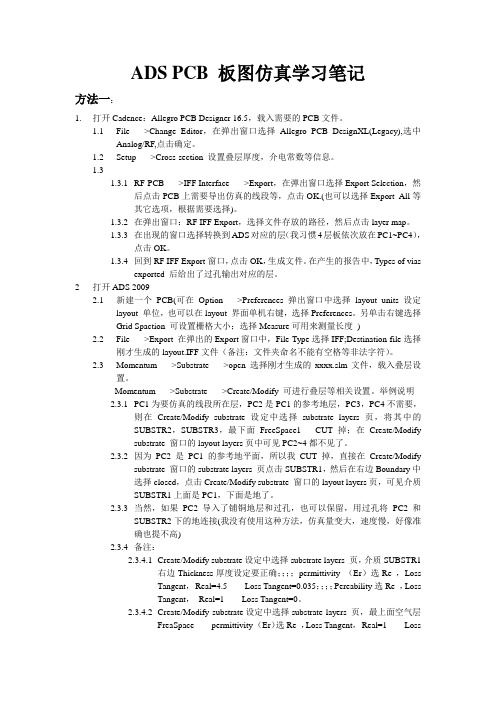

ADS PCB 板图仿真学习笔记方法一:1.打开Cadence:Allegro PCB Designer 16.5,载入需要的PCB文件。

1.1File----->Change Editor,在弹出窗口选择Allegro PCB DesignXL(Legacy),选中Analog/RF,点击确定。

1.2Setup----->Cross-section 设置叠层厚度,介电常数等信息。

1.31.3.1RF-PCB----->IFF Interface----->Export,在弹出窗口选择Export Selection,然后点击PCB上需要导出仿真的线段等,点击OK.(也可以选择Export All等其它选项,根据需要选择)。

1.3.2在弹出窗口:RF IFF Export,选择文件存放的路径,然后点击layer map。

1.3.3在出现的窗口选择转换到ADS对应的层(我习惯4层板依次放在PC1~PC4),点击OK。

1.3.4回到RF IFF Export窗口,点击OK,生成文件。

在产生的报告中,Types of viasexported 后给出了过孔输出对应的层。

2打开ADS 20092.1新建一个PCB(可在Option----->Preferences 弹出窗口中选择layout units 设定layout 单位,也可以在layout 界面单机右键,选择Preferences。

另单击右键选择Grid Spaction 可设置栅格大小;选择Measure可用来测量长度)2.2File----->Export 在弹出的Export窗口中,File Type选择IFF;Destination file选择刚才生成的layout.IFF文件(备注:文件夹命名不能有空格等非法字符)。

2.3Momentum----->Substrate----->open 选择刚才生成的xxxx.slm文件,载入叠层设置。

![[AD经验] PCB LAYOUT 中的直角走线、差分走线和蛇形线](https://img.taocdn.com/s1/m/25741fd2aa00b52acfc7cad4.png)

布线(Layout)是PCB设计工程师最基本的工作技能之一。

走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout 得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

主要从直角走线,差分走线,蛇形线等三个方面来阐述。

1.直角走线直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。

其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。

直角走线的对信号的影响就是主要体现在三个方面:∙一是拐角可以等效为传输线上的容性负载,减缓上升时间;∙二是阻抗不连续会造成信号的反射;∙三是直角尖端产生的EMI。

传输线的直角带来的寄生电容可以由下面这个经验公式来计算:C=61W(Er)1/2/Z0在上式中,C 就是指拐角的等效电容(单位:pF),W指走线的宽度(单位:inch),εr 指介质的介电常数,Z0就是传输线的特征阻抗。

举个例子,对于一个4Mils的50欧姆传输线(εr为4.3)来说,一个直角带来的电容量大概为0.0101pF,进而可以估算由此引起的上升时间变化量:T10-90%=2.2*C*Z0/2 = 2.2*0.0101*50/2 = 0.556ps通过计算可以看出,直角走线带来的电容效应是极其微小的。

由于直角走线的线宽增加,该处的阻抗将减小,于是会产生一定的信号反射现象,我们可以根据传输线章节中提到的阻抗计算公式来算出线宽增加后的等效阻抗,然后根据经验公式计算反射系数:ρ=(Zs-Z0)/(Zs+Z0)一般直角走线导致的阻抗变化在7%-20%之间,因而反射系数最大为0.1左右。

而且,从下图可以看到,在W/2线长的时间内传输线阻抗变化到最小,再经过W/2时间又恢复到正常的阻抗,整个发生阻抗变化的时间极短,往往在10ps 之内,这样快而且微小的变化对一般的信号传输来说几乎是可以忽略的。

1.常规布线:不详细说了,是个人就知道怎么弄。

需要说明的是在布线过程中,可按小键盘的*键或大键盘的数字2键添加一个过孔;按L键可以切换布线层;按数字3可设定最小线宽、典型线宽、最大线宽的值进行切换。

2. 总线式布线:通俗的讲就是多条网络同事布线的问题。

具体方法是,按住SHIFT,然后依次用光标移到要布线的网络,点击鼠标左键即可选中一条网络,选中所需的所有网络以后,单击工具栏汇的总线布线图标,在被选网络中任意单击即可开始多条网络同时布线。

布线过程中可以按键盘上左右尖括号<>调节线间距。

3.差分对布线:差分网络是两条存在耦合的传输线,一条携带信号,另一条则携带它的互补信号。

使用差分对布线前要对设定差分对网络进行设置。

设置可以在原理图中设置,也可以在PCB中进行设置。

a 原理图中添加差分对规则:在命名差分对网络时,必须保证网络名的前缀是一样的,后缀中用下划线带一个N和一个P字母即可。

命名好之后点击菜单Place-Directives-DifferntialPair命令,在差分对上放置两个差分对图标。

单击菜单Design-Update PCB Document ****在打开的对话框中重新传差一次修改规则即可在PCB中进行差分对布线。

b.在PCB中添加差分对布线规则:快捷菜单PCB打开PCB面板,从面板第一栏中选择Differential Pairs Editor,单击add,在打开的差分对设置对话框中选定要定义成差分对的网络,然后在Name栏内输入一个差分对名称单击OK退出设置,之后就可以进行差分布线了。

单击工具栏中的差分对布线图标,软件自动将网络高亮显示,在差分对网络上单击开始布线,布线过程中可以添加过孔、换层等操作。

4.蛇形走线:单击工具栏中的交互式布线图标进入交互布线,在布线过程中按键盘SHIFT+A即可切换到蛇形布线模式,按数字1、2键可调整蛇形线倒角,按3、4键可调节间距,按<>键可调节蛇形线幅度。

(7条消息)AltiumDesigner20及21的焊盘走线引出方式设置微信公众号原文链接:Altium Designer 20及21的焊盘走线引出方式设置最近几个月工程任务紧,博主都在忙于研制特殊功能的FPGA板卡,设计工具采用的是大家都熟知的Altium Designer 的20版本。

按道理来讲,该软件的新版本用起来应该更智能化,更高效、流畅。

但是博主在使用过程中却遇到了一个很糟心的麻烦:默认的AD20系统设置会导致从焊盘引出的走线畸形,严重影响心情,进而耽误研发进度。

如下图所示为本应正常差分线的焊盘引出走线显示:图1:正常差分线的焊盘引出走线可是在Altium Designer 最新的20版本中,差分线的焊盘引出走线全部为下图2所示的莫名形状,对于博主这种强迫症患者来说,简直是无法容忍:图2:AD20默认的差分线焊盘引出走线如下图3所示为本应正常单端的焊盘引出走线显示:图3:正常单端线的焊盘引出走线如下图4所示为AD20默认的焊盘引出走线显示,实在是忍无可忍:图4:AD20默认的单端线焊盘引出走线博主查阅了大量的资料后,才找到原因所在,这里分享给大家:1,打开AD20的系统设置选项,注意右下角的Advanced图标,如下图5所示:图5:system-General-Advanced2,点击"Advanced",进入系统高级设置页面,如下图6所示:在Legacy.PCBInternalGloss选项里,一定要勾上前面的选项!一定要勾上前面的选项!一定要勾上前面的选项!(说三遍!)。

系统默认该选项不勾选的,因此会出现焊盘引出走线畸形。

图6:Advanced设置我们设置好该项后,所有的走线视觉效果就都正常了!版本21也同样适用噢~。

差分线和等长线(蛇形)AD9中差分走线和等长走线(蛇形)一、差分走线:1.在原理图中对差分信号网络标号重命名。

(如下图1)图12.添加差分对标号(图1中红颜色的标志):3.从原理图导入PCB;4.差分走线快捷键为P, I(注意区分:一般走线时候的快捷键是P,T)二、等长走线:1.菜单项选择Design——Classes2.(如图2)对话框Object Class Explorer中选择Object Classes,在展开的树文件中选择Net Classes。

右键弹出的快捷菜单中选择Add Class。

再右键单击Add Class选择Rename Class 进行重命名。

图23.(如图3)单击打开重命名的Class,在Non-Members中选择欲走的等长走线网络标号(例如:DIN+,DIN-,DOUT+,DOUT-,A,B),通过按钮移动到Members。

单击Close完成欲走的等长的走线网络。

4.(如图4)走等长线之前,对欲走等长走线的网络先进行手工布线。

图45.(如图5)快捷键T , R后,鼠标左键点住网络A的布线同时按下TAB键,弹出的对话框:在选项Target length中选择From Net选项;在右边方框中选择欲走等长线的网络标号(例如:B,注意:等长走线时应该选择手工布线长度较大的一个网络标号为基准,欲等长走线的所有网络都会按照基准的长度进行蛇形走线。

)图56.(如图5)蛇形设置:在Style中可以更改蛇形的样式。

单击OK 完成设置。

图67.(如图7)鼠标在之前的手工布线上移动就可以形成蛇形线了。

在蛇形走线时,分别用“1”“2”“3”“4”“,”“。

”控制蛇形线的形状。

快捷键:1与2改变蛇形线的拐角和弧度快捷键:3与4改变蛇形线的宽度快捷键:,与。

改变蛇形线的幅度图78.(如图7)检查蛇形线的长度是否等长。

快捷键:R, L。

在Net Status Report中查看欲走等长走线的网络。

AD中关于差分线的设置和走线的方法差分线是一种用于传输高速信号的电路设计技术。

在高速信号传输中,信号会受到电磁干扰和信号损耗的影响,差分线技术能够有效地减小这些干扰和损耗,并提高信号传输的可靠性。

下面,我将详细介绍AD中关于差分线的设置和走线的方法。

一、差分线的设置:1.差分线的长度匹配:差分信号的传输速率越高,其对线路长度匹配的要求就越高。

在AD 中,可以通过Signal Integrity模块来进行差分线的长度匹配。

首先,在PCB设计阶段,可以根据差分线的长度和传输速率进行合理的走线规划,以确保差分信号在传输过程中能够同步到达。

其次,可以通过Signal Integrity模块中的差分线长度匹配功能,自动调整差分线的长度,以满足设计的要求。

2.差分阻抗的控制:差分线的阻抗匹配对于有效地传输差分信号至关重要。

在AD中,可以通过布局阶段中的差分线约束规则来设置差分线的阻抗。

首先,在布局阶段,可以通过选择合适的宽度和间距来控制差分线的阻抗值。

然后,在走线阶段,可以使用差分线走线规则来确保差分线的宽度和间距满足设计要求。

二、差分线的走线方法:1.差分线的走向选择:在AD中,可以通过走线规则和信号完整性分析来选择差分线的走向。

首先,在布局阶段,可以根据芯片引脚的布置情况和信号传输路径来确定差分线的走线方向。

其次,在走线阶段,可以使用规则驱动的走线方法,根据差分线的长度和布局情况来选择最佳的走线路径。

2.保持差分线的对称性:在设计中,差分线的对称性对于减小信号的不对称失配和减小共模噪声的影响非常重要。

因此,在走线过程中,应尽量保持差分线的对称性,包括差分线的宽度、间距和走线路径的相对位置等方面。

可以通过AD中的规则驱动走线功能和信号完整性分析,自动调整差分线的走线路径,以达到最佳的对称性。

3.避免与其他信号线的干扰:差分线的走线过程中,还应避免与其他信号线的干扰。

干扰可能包括电磁辐射、互电感和互电容等因素。

[AD经验]PCBLAYOUT中的直⾓⾛线、差分⾛线和蛇形线布线(Layout)是PCB设计⼯程师最基本的⼯作技能之⼀。

⾛线的好坏将直接影响到整个系统的性能,⼤多数⾼速的设计理论也要最终经过Layout 得以实现并验证,由此可见,布线在⾼速PCB设计中是⾄关重要的。

下⾯将针对实际布线中可能遇到的⼀些情况,分析其合理性,并给出⼀些⽐较优化的⾛线策略。

主要从直⾓⾛线,差分⾛线,蛇形线等三个⽅⾯来阐述。

1.直⾓⾛线直⾓⾛线⼀般是PCB布线中要求尽量避免的情况,也⼏乎成为衡量布线好坏的标准之⼀,那么直⾓⾛线究竟会对信号传输产⽣多⼤的影响呢?从原理上说,直⾓⾛线会使传输线的线宽发⽣变化,造成阻抗的不连续。

其实不光是直⾓⾛线,顿⾓,锐⾓⾛线都可能会造成阻抗变化的情况。

直⾓⾛线的对信号的影响就是主要体现在三个⽅⾯:⼀是拐⾓可以等效为传输线上的容性负载,减缓上升时间;⼆是阻抗不连续会造成信号的反射;三是直⾓尖端产⽣的EMI。

传输线的直⾓带来的寄⽣电容可以由下⾯这个经验公式来计算:C=61W(Er)1/2/Z0在上式中,C 就是指拐⾓的等效电容(单位:pF),W指⾛线的宽度(单位:inch),εr 指介质的介电常数,Z0就是传输线的特征阻抗。

举个例⼦,对于⼀个4Mils的50欧姆传输线(εr为4.3)来说,⼀个直⾓带来的电容量⼤概为0.0101pF,进⽽可以估算由此引起的上升时间变化量:T10-90%=2.2*C*Z0/2 = 2.2*0.0101*50/2 = 0.556ps通过计算可以看出,直⾓⾛线带来的电容效应是极其微⼩的。

由于直⾓⾛线的线宽增加,该处的阻抗将减⼩,于是会产⽣⼀定的信号反射现象,我们可以根据传输线章节中提到的阻抗计算公式来算出线宽增加后的等效阻抗,然后根据经验公式计算反射系数:ρ=(Zs-Z0)/(Zs+Z0)⼀般直⾓⾛线导致的阻抗变化在7%-20%之间,因⽽反射系数最⼤为0.1左右。

⽽且,从下图可以看到,在W/2线长的时间内传输线阻抗变化到最⼩,再经过W/2时间⼜恢复到正常的阻抗,整个发⽣阻抗变化的时间极短,往往在10ps 之内,这样快⽽且微⼩的变化对⼀般的信号传输来说⼏乎是可以忽略的。

AD中关于PCB规则的设置在AD软件中,PCB规则设置对于电路设计和布局来说非常重要。

通过正确设置PCB规则,可以确保电路板的可靠性、稳定性和性能,并减少电磁干扰和信号完整性问题。

首先,PCB规则设置包括以下几个方面:1.尺寸和布局规则:设置电路板的尺寸、层堆叠、引线宽度、间距等尺寸规则。

这些规则确保布局的有效性和一致性,并确保避免尺寸和布局冲突。

2.电气规则:设置信号传输线的布线规则,如最小/最大信号间距、最小/最大引线宽度、差分线规则等。

这些规则保证了电流和电信号的准确传输以及可靠性。

3.电源规则:设置电源供应的规则,包括电源引线宽度、电源平面和电源区域的设置。

这些规则可以确保电源的稳定性和可靠性,并减少电源噪声和电磁干扰。

4.信号完整性规则:设置信号的阻抗匹配、终端电阻、阻抗控制、克服信号反射等规则。

这些规则可以提高信号传输的质量和稳定性,并减少信号丢失和干扰。

5.堆栈规则:设置电路板的层堆叠结构,包括层分布、内部电源引线和平面设置等。

这些规则能够优化电路板的阻抗匹配、冷却效果和EMI性能。

6.安全规则:设置电路板的安全规则,如最小间距、引线尺寸、焊盘尺寸等。

这些规则确保电路板的安全性和可靠性,以防止短路、电弧和其他意外情况。

7.设备规则:设置连接器、器件封装、机械孔和固定件的规格和布局。

这些规则确保了设备的可靠性和适配性,同时简化了组装和制造过程。

如何设置这些规则取决于具体的电路板设计要求和约束。

一般来说,可以通过以下步骤来设置PCB规则:1.根据设计要求和制造能力,确定合适的规则和约束。

4.按照设计要求和制造能力,检查并修改设置的规则,确保规则的合理性和一致性。

5.保存并应用规则设置,以确保在后续的布局和布线过程中遵循这些规则。

需要注意的是,PCB规则设置是一个动态的过程,可能需要在设计过程中进行多次调整和修改。

同时,为了确保电路板的可靠性和稳定性,还需要结合其他设计和验证工具,如电路模拟仿真、布局验证和信号完整性分析等。