L波段频率源设计

- 格式:docx

- 大小:12.49 KB

- 文档页数:2

40 | 电子制作 2018年1月取样锁相环最主要的特点就是将数字鉴相器表换成了取样鉴相器,其主要原理如图1所示,其中各项原理过程都一目了然。

■1.2 倍频锁相环分频器的使用使倍频锁相环成为了一种设计方案,在民用的各个方面,其使用相对来说是最为广泛的。

当输入端的信号与经过分频后产生的信号进行比较时,如果两个信号的频差刚好是零,那就说明有一个很稳定的误差电压,并且该环路的状态较为稳定[1]。

■1.3 混频锁相环混频锁相环的原理原理更多是为混频变频,通过环路的调节,当环路处于稳定状态的情况,便成功地完成整个混频要求。

混频锁相环在技术方面要求不高,可以很好地进行设计,但因为其整个过程太过于繁琐,而且加入了许多不同的调频器,导致最后得出的结果不够准确,有较多的杂乱信息,并且因为线路过长的问题,会导致整个电路的稳定性不强,很容易会产生故障,影响整个设计的进行。

2 方案的确定及可行性论证■2.1 Ku 波段频率源板技术指标和方案的确定基于PLL 的Ku 波段的技术指标如表1所示。

个较好的实现,在基于高频段且低成本的条件下,还能拥有低杂散等有点,最终可应用在各个设施上,而图2则是基于PLL 的Ku 波段的原理框图。

■2.2 方案的可行性论证在频率合成技术越来越成熟的今天,锁项式频率合成已成为了许多人较为熟知且运用熟练的技术,而经过大量的资料查找,可以发现,基于PLL 的Ku 波段也是可以通过该种方法去实现的。

对于该方案有下面几点可行性论证:图2 Ku 波段频率源的原理框图(1)想要达到低杂散,就要从形成原因入手,主要是因为外部串扰和参考信号等缘故,想要杜绝或者减少这种情况的产生,可以选择一个>-65dBc 的晶体振荡器,如果相比来说仍然达不到要求,可以再加一个滤波器,通过以上的布置,可以很好地做到低杂散,并且完全符合要求[2]。

(2)可以发现,基于PLL 的Ku 波段的各项要求并不高,只是需要一个较为全面的设计形式,让各个方面都能有一个很好的表现,在现有的技术上可以通过不同的组合与调试将这个目标实现。

L波段宽带上变频器的设计与实现张洪涛;张伟;杜欣【摘要】介绍了一种L波段宽带上变频器的设计方案与电路实现,该方案可有效降低杂散抑制难度.首先介绍了该方案的电路结构和仿真分析,并给出了关键电路本振和频综的实现方法,最后给出了模块的实测结果.仿真和实测结果表明该模块实现了预期指标需求.%In this paper, a design scheme of wide-band up-converter in L band and the designing method of the circuit are presented, which reduce the difficulty of spurious suppression effectively. Firstly, the paper presents the circuit structure and the circuit simulation analysis, and gives the designing method of the significant circuit that can produce the local oscillation and frequency synthesis. Finally, the actual measurement results of the module is presented. The simulation and measurement results indicate that the module meets the needs of the anticipated specifications.【期刊名称】《现代电子技术》【年(卷),期】2012(035)015【总页数】3页(P90-92)【关键词】频率合成器;杂散抑制;本振泄露;超外差【作者】张洪涛;张伟;杜欣【作者单位】北京天航信民航通信网络发展有限公司,北京100193;北京天航信民航通信网络发展有限公司,北京100193;北京天航信民航通信网络发展有限公司,北京100193【正文语种】中文【中图分类】TN773-340 引言IF/L波段上变频模块是卫星通信中的重要模块,因其频带较宽,需采用二次变频的架构实现;为防止系统杂散对其他无线信号的干扰,对杂散抑制度指标要求较高,宽带滤波器的设计往往是设计中的难点。

L波段频率合成器的设计【摘要】频率合成器是电子系统中非常重要的部件,常常被称作电子系统的心脏,目前正广泛地应用于电子对抗、遥控遥测通信、仪器仪表、雷达、导航以及广播电视等各个领域。

本文利用锁相环技术产生1200 MHz信号源,分析了电路的主要组成单元,对重要的技术和电路单元作了比较详细的说明。

涉及关键器件的选择,搭建外部硬件电路与内部的控制程序等内容。

本文的结尾作了分析总结。

【关键词】PLL;环路滤波器;频率合成器L-band Frequency Synthesizer DesignHU Hong LU Jing(Chengdu College of University of Electronic Science and Technology of China,Chengdu Sichuan 611731,China)【Abstract】The signal source is very important electronic components in the system,often called the heart of the electronic system in various fields,it is being widely used in electronic warfare,remote communication,instrumentation,radar,navigation and radio and television. The phase-locked loop technology produces a 1200 MHz signal source,the main components of the circuit unit,the important technical and circuit unit are made a more detailed explanation. Involving key device selection,building external hardware circuitry and internal control procedures and so on. In the last analysis summary.【Key words】PLL;Loop filter;The frequency synthesizer0 引言在仪器仪表测量,雷达系统,电子对抗,微波通信,生物医学以及制导等领域中都有广泛的应用。

L波段的低相噪锁相频率源的研制的开题报告一、选题背景随着无线通信和卫星导航等领域的飞速发展,对宽带、高精度、低相噪的锁相频率源的需求日益增加。

L波段频率范围是1-2 GHz,是卫星导航和军事通信等领域的重要频段。

然而,目前市场上大部分L波段锁相频率源还存在着体积大、功耗高、相噪高等缺点。

因此,研制一种低相噪、小型化、低功耗的L波段锁相频率源具有重要的研究意义和现实意义。

二、研究目的本研究旨在设计并研制一种低相噪的L波段锁相频率源,满足小型化、低功耗、高精度的要求,提高在卫星导航和军事通信等领域的应用价值。

三、研究内容1. L波段锁相频率源技术研究通过文献资料收集、分析和总结,了解L波段锁相频率源的最新技术发展和研究进展,为设计和研制提供理论依据。

2. L波段锁相频率源系统设计在分析和总结现有L波段锁相频率源技术的基础上,结合应用需求,设计一种低相噪、小型化、低功耗的L波段锁相频率源。

具体包括:采用合适的电路模型对系统进行建模;选择合适的器件和元器件,进行系统设计和布局;进行仿真和调试,调整各个模块之间的参数,并达到满足设计要求的效果。

3. L波段锁相频率源实验验证通过实验平台,搭建L波段锁相频率源实验验证平台,将设计好的系统进行实际测试,测试其精度、稳定性、相噪等参数,验证设计方案的正确性和可行性。

四、研究方法本研究采用文献资料收集、系统设计、仿真软件模拟、实验测试等综合方法,以完整的技术路线进行研究。

五、研究计划1. 第一阶段(1个月):完成文献资料收集、分析和总结。

2. 第二阶段(2个月):进行L波段锁相频率源系统设计,包括建模、器件选择、系统设计和布局。

3. 第三阶段(2个月):进行仿真和调试,调整各个模块之间的参数,并达到满足设计要求的效果。

4. 第四阶段(3个月):搭建实验平台,进行L波段锁相频率源实验验证。

5. 第五阶段(1个月):撰写论文和毕业论文的答辩。

六、研究意义本研究可以为L波段锁相频率源的设计和研制提供参考,对提高L波段锁相频率源的精度和稳定性具有实际意义,同时也具有推广应用价值。

L波段频率源设计

0 引言频率合成器是以一个高精确度和高稳定的石英晶体振荡器为基准参考频率,通过加、减、乘、除四则运算,获得与石英晶体振荡器同样精确度

和稳定度的频率源。

本文利用频率合成技术实现频率倍频,输出L 波段点频源。

利用非线性电路产生高次谐波或者利用频率控制电路都可以构成倍频器。

也

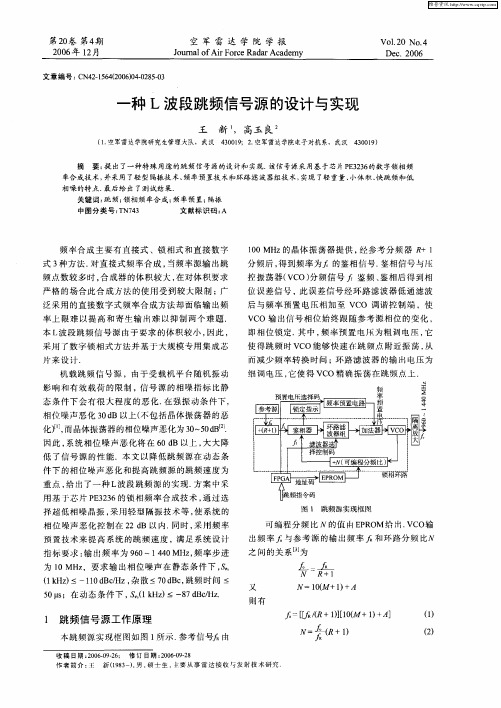

可以由锁相倍频电路实现,该电路是一个闭环频率反馈系统,它主要由鉴相器、环路滤波器、压控振荡器和累加计数器构成,本设计采用这种方案。

目前出现了众多单片集成频率合成芯片,如美国QualComm 公司的Q3236 等,这种带有前置分频器和多个计数器的芯片,给锁相环电路的设计带来了极大的方便,

为实现电路的小型化提供了可能。

下面对总体方案设计,Q3236 芯片的功能,电路和环路滤波器设计逐一讨论。

1 方案设计本设计采用对晶体振荡器输出的参考信号,直接锁相倍频获得高频信号,再将高频信号放大到设计要求的方案。

利用的是锁相频率合成技术,属于间接频率合成。

整个倍频源基本由锁相

倍频电路、放大和滤波电路组成,最重要的是锁相倍频电路。

锁相倍频电路利用锁相技术实现频率合成,锁相环(PLL)是其中的重要组成部分,实质上是

一个相位负反馈自动控制系统。

基本由鉴相器(PD)、环路滤波器(LF)、压控振

荡器(VCO)三部分组成。

鉴相器用于比较两个输入信号相位,产生对应于两个

信号瞬时相差的误差电压;环路滤波器具有低通作用,把鉴相器输出的误差电

压滤波,滤除高频成分和噪声,以保证环路所要求的性能,提高系统稳定性;

压控振荡器受误差电压控制,使得VCO 的输出频率向参考频率靠近,直到消

除频差而锁定。

倍频源框图如图1 所示。

设计采用QualComm 公司的高性能数字锁相环芯片Q3236,其内部集成有。