EDA实现电子琴的程序文件

- 格式:doc

- 大小:60.50 KB

- 文档页数:7

EDA与数字系统课程设计报告院、系:信息工程学院专业:电子信息科学与技术学号:200912411姓名:张海超同组人:孙国锐花卫东指导教师:段美霞郑辉二00一一年十二月三十日目录(空两行) 1………………………………………………………………页码2………………………………………………………………页码(要求:给出一级目录,宋体加粗,四号字,1.5倍行距。

)(报告正文部分):(要求:正文部分一律用小四号字,宋体,1.5倍行距。

一级大标题靠左,加粗。

二级大标题靠左,不加粗。

)课程设计的内容如下:1.课程设计目的(1)熟悉Quartus 2软件的使用。

(2)熟悉EDA实验箱的基本使用。

(3)学习HDL基本单元电路的设计应用。

进一步掌握EDA的多层次设计方法。

(4)熟悉频率发生器的的原理。

2.课程设计题目描述和要求设计一个简易的的电子琴,有1,2,3,4,5,6,7这几个音阶,当按对应的按键时,发出声音的同时显示所按的音符。

还有自动演奏的功能,当自动演奏的同时显示对应的高中低音符;3.课程设计报告内容3.1本设计由分频器,手动/自动演奏模块、频率发生器、乐谱3个模块组成。

分频器是产生4Hz频率的;手动/自动演奏模块的作用是实现手动和自动演奏音乐的控制;频率发生器是产生各种音阶对应频率的,得到与1,2,3,4,5,6,7,音符(包含高中低三种)对应的频率。

流程:1 产生4Hz的频率;2 由song产生控制信号song_on,当song改变时song_on取反并一直保持,直到song再次改变,也只有这样song_on才能控制手动和自动;3 如果song_on为低电平时,手动演奏,反之则自动演奏;4 手动演奏时,按照输入的按键in[n](对应1234567)产生对应频率speaker。

并在当时的状态(1234567)赋给high0让输出LED显示;5 自动演奏时,按照乐谱高中低产生对应的频率out,并把out赋值给speaker。

数字电子EDA课程设计八音电子琴第一篇:数字电子EDA课程设计八音电子琴燕山大学EDA课程设计实验报告院系:信息科学与工程学院姓名:班级:学号:日期:[实验名称] 八音电子琴[实验要求] 1.能发出1.2.3.4.5.6.7.i八个音2.用按键作为键盘3.C调至B调对应频率如下表音调 C(高音)B A G F E D C频率(Hz)261.63x2 493.88 440.00 392.00 349.23 329.63 293.66 261.63 [实验电路设计] 1.命题分析根据命题的要求,要使扬声器发音,需要在其输入信号端连接一个对应频率的方波信号.实验使用的信号源可以提供从几Hz到几兆Hz不等的信号频率,自然可以想到本实验命题的关键是一个具有相应分频比的分频器.考虑到硬件(按钮)在实际工作过程中会因元件的接触产生一些不可避免的抖动脉冲电平,会对实验造成影响,因此需要在按键接入线路中安装防抖动电路.2.设计过程1>分频器为了取得合适的电路复杂度和可接受的误差范围,分频器的时钟信号选取为器件所提供的JPCK—1(3MHz音频信号).然后通过计算,用时钟信号频率除以各发音频率,得到的分频比如下表:分频比(16进制)5DEE 6384 6F84 7D62 8ADE 951C A760 BBDE频率(Hz)高C:261.63x2 B:493.88 A:440.00 G:392.00 F:349.23 E:329.63 D:293.66 C:261.63 利用四片十六进制计数器74LS161就可以连接成适用的分频器.分频器连接完成后会产生一个预定频率的周期脉冲.但是实验要求的方波其占空比应该为1:1,因此在输出脉冲端加装一个T触发器,每次脉冲到达触发器的时候输出便会跳变电平,这就达到了驱动扬声器的条件.但是在应用了T触发器后输出方波的周期比预定的扩大了一倍,也就是说频率减至原来的二分之一.此时应重新选择时钟信号,令其为原来2倍即可.根据实验指导书,最终确定选择的时钟信号为6MHz.2>防抖动电路利用D触发器的电压跟随特性可以用一个频率较低的时钟信号驱动,达到防止按键抖动的目的.电路较简单,见图3.图1.时钟分频电路(downway)图2.CP为375K时上图的B4输出波形由于设计的原因,本电路只能支持单音节输入.当同时键入两个以上的音阶时,分频比较小的(比较高的音阶)优先发声.图3.按键输入防抖动电路3>电路组合组合后的电路模块如图4.共有11个输入端和1个输出端.其中,CP_6M为整个电路的主频,使用电路板上的6MHz信号输出端;CP_1US为防抖动电路中触发器所使用的时钟,要求频率不高,选择电路板提供的CLK3-3(12Hz);KEYCa-B是电子琴的输入按键接口,依次是从低音到高音.Speaker是电路的输出端,接入扬声器,为其产生相应音阶的频率.实际电路如图4.连接完成后,对该电路进行仿真测试,如图5,令其CP_6M为6MHz,CP_1US为一个较低频率脉冲,设臵KEYB(音节B)为有效电平,在speaker上得到的输出频率为493,与实际音节的频率相同.图4.八音电子琴图5.电子琴完成品的仿真波形T触发器2分频电路[硬件测试] [实习心得] 第一感觉,数字电子技术EDA实习很有意思.我们可以有充分的时间去思考怎么做出一个东西,这个东西的用处也许不大甚至几乎没有,但重要的是思考的过程:从它的用途总结出它的特性,从它的特性构思出它的原理,从原理到构建模型,再到模型的实现,利用已有的知识,可用的元件,最终组合出一个具有高度逻辑性的组合电路,这和我们小时候玩搭积木差不多.把积木一块块的搭成一座城堡,中间缺少任何一层甚至任何一块,城堡都可能会倒塌.同理,在我们构建命题所给的元器件时任何一个逻辑错误都可能是致命的,导致最后无法出现正确结果或者干脆不能用.因此,实习,有意思的同时还不能大意.这是一个锻炼逻辑思维和思维严谨性的极好的机会,我和我的同学们在这次工作中受益非浅.大家都积极思思考,查找资料,集思广益来解决现有的问题。

音乐发生器及简单电子琴的eda设计摘要本系统是采用EDA技术设计的一个简易的八音符电子琴和音乐发生器,该系统基于计算机中时钟分频器的原理,采用自顶向下的设计方法来实现,它可以通过按键输入来控制音响。

系统由乐曲自动演奏模块、乐器演示模块琴/乐功能选择模块、音调发生模块和数控分频模块五个部分组成。

系统实现是用硬件描述语言VHDL按模块化方式进行设计,然后进行编程、时序仿真、整合。

本系统功能比较齐全,有一定的使用价值。

关键字电子琴;EDA;VHDL;音调发生;QuartusII;1 引言:1.1设计目的1)利用数控分频器设计一个电子琴硬件电路和音乐发生器2)演奏时可以选择是手演奏(键盘输入)或自动演奏已存入的乐曲,并且能自动重复演奏1.2设计的基本内容运用VHDL语言对简易电子琴的各个模块进行设计,并使用EDA 工具对各模块进行仿真验证。

本设计包含如下三个模块:乐曲自动演奏模块,音调发生模块,数控分频模块,最后把各个模块整合后,通过电路的输入输出对应关系连接起来2.1 EDA技术EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

2.2 硬件描述语言——VHDL2.2.1 VHDL的简介VHDL的英文全名是Very-High-Speed Integrated Circuit HardwareDescription Language,诞生于1982年。

EDA实验报告课程名称:EDA技术实验名称:硬件电子琴电路设计班级:姓名:指导老师:签名:一、实验目的学习利用数控分频器设计硬件电子琴实验。

二、实验仪器计算机一台;Quartus Ⅱ软件;U盘。

三、实验内容与步骤在Quartus Ⅱ完成音阶发生器模块TONE和数控分频器模块Speaker的设计,然后完成硬件电子琴顶层文件的设计,最后检查设计是否正确。

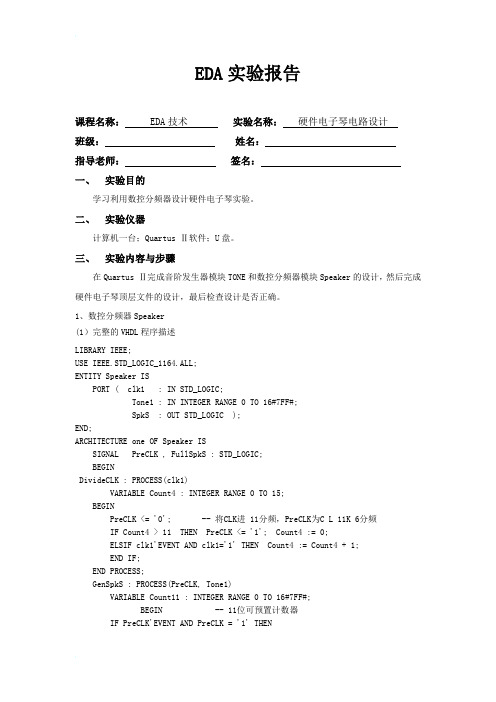

1、数控分频器Speaker(1)完整的VHDL程序描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY Speaker ISPORT ( clk1 : IN STD_LOGIC;Tone1 : IN INTEGER RANGE 0 TO 16#7FF#;SpkS : OUT STD_LOGIC );END;ARCHITECTURE one OF Speaker ISSIGNAL PreCLK , FullSpkS : STD_LOGIC;BEGINDivideCLK : PROCESS(clk1)VARIABLE Count4 : INTEGER RANGE 0 TO 15;BEGINPreCLK <= '0'; -- 将CLK进 11分频,PreCLK为C L 11K 6分频IF Count4 > 11 THEN PreCLK <= '1'; Count4 := 0;ELSIF clk1'EVENT AND clk1='1' THEN Count4 := Count4 + 1; END IF;END PROCESS;GenSpkS : PROCESS(PreCLK, Tone1)VARIABLE Count11 : INTEGER RANGE 0 TO 16#7FF#;BEGIN -- 11位可预置计数器IF PreCLK'EVENT AND PreCLK = '1' THENIF Count11=16#7FF# THEN Count11 := Tone1; FullSpkS <= '1'; ELSE Count11:=Count11 + 1; FullSpkS <= '0'; END IF; END IF; END PROCESS;DelaySpkS : PROCESS(FullSpkS) VARIABLE Count2 : STD_LOGIC; BEGINIF FullSpkS'EVENT AND FullSpkS = '1' THEN Count2 := NOT Count2; IF Count2 = '1' THEN SpkS <= '1'; ELSE SpkS <= '0'; END IF; END IF; END PROCESS; END;(2)模块图形符号及逻辑功能描述图1 数控分频器Speaker 模块DENAQPRE CLRA[3..0]B[3..0]OUT[3..0]ADDERA[10..0]B[10..0]OUT[10..0]ADDERA[10..0]B[10..0]OUTEQUALDENAQPRE CLRA[3..0]B[3..0]OUTLESS_THAND ENA QPRE CLRDQPRE ENA CLRDQ PRE ENA CLRSELDATAA DATABOUT0MUX21\DelaySpkS:Count2Add111' h001 --FullSpkSSpkS~reg0\GenSpkS:Count11[10..0]Count11~[10..0]clk1SpkSTone1[10..0]Add04' h1 --Equal011' h7FF --LessThan04' hB --\DivideCLK:Count4[3..0]图2 数控分频器Speaker 硬件电路2、端口TONE 的设计(1)完整的VHDL 程序描述 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY Tone ISPORT ( Index : IN STD_LOGIC_VECTOR(7 DOWNTO 0); CODE : OUT INTEGER RANGE 0 TO 15; HIGH : OUT STD_LOGIC;Tone : OUT INTEGER RANGE 0 TO 16#7FF# );END;ARCHITECTURE one OF Tone ISBEGINSearch : PROCESS(Index)BEGINCASE Index IS -- 译码电路,查表方式,控制音调的预置数 WHEN "" => Tone <= 773; CODE <= 1; HIGH <= '0';WHEN "" => Tone <= 912; CODE <= 2; HIGH <= '0';WHEN "" => Tone <= 1036; CODE <= 3; HIGH <= '0';WHEN "" => Tone <= 1116; CODE <= 4; HIGH <= '0';WHEN "" => Tone <= 1197; CODE <= 5; HIGH <= '0';WHEN "" => Tone <= 1290; CODE <= 6; HIGH <= '0';WHEN "" => Tone <= 1372; CODE <= 7; HIGH <= '0';WHEN "" => Tone <= 1410; CODE <= 1; HIGH <= '1';WHEN OTHERS => Tone <= 2047; CODE <= 0; HIGH <= '0'; END CASE;END PROCESS;END;(2)模块图形符号及逻辑功能描述图3 tone模块图4 tone硬件电路3.顶层文件的设计将音阶发生器模块TONE和数控分频器模块Speaker打包之后,接下来进行顶层文件的设计。

实验十五电子琴设计一、音名与频率的关系:音乐上的十二平均律规定:每两个八度音之间的频率相差一倍。

在这两个八度音之间,分成十二个半音,每两个相邻伴音的频率比为12 2。

另外还规定,音名A的频率为440Hz。

音名B到C、E到F之间为半音,其余为全音。

这样,可计算得从A(简谱的低音6)到a1(简谱的高音6)之间每个音名的频率为:A(6):440Hz a(6):880Hz a1(6):1760HzB(7):493.88Hz b(7):987.76Hzc(1):523.25Hz c1(1):1046.50Hzd(2):587.33Hz d1(2):1174.66Hze(3):659.25Hz e1(3):1318.51Hzf(4):698.46Hz f1(4):1396.92Hzg(5):783.99Hz g1(5):1567.98Hz二、设计要求:设计一个电子琴,要求能演奏音名A到a1之间的全部音阶。

按下一个键,则演奏该音名,并用数码管显示音名,用发光二极管指示高、中、低音。

三、设计提示:本实验由键盘编码,音频输出译码器、分频器组成。

取10MHz信号作为基准。

以基准频率除以上述频率,可得各音名频率的分频系数。

注意,为了减少输出的偶次谐波成分,最后输出应为对称方波。

音频输出译码器实质上是一个多路选择器,根据键盘编码的输出,选择音阶发生器的不同的预置数,分频后输出音频。

分频器可以为加法计数器,以可以为减法计数器,计算预置数时稍有不同,应加以注意。

另外,应根据基准频率和输出频率,来确定计数器的位数。

设计框图如下图所示:电子琴框图四、实验步骤1、启动ISE集成开发环境,创建工程并输入设计源文件。

2、对设计进行时序仿真,分析设计的正确性。

3、锁定引脚,完成设计实现过程。

并在实验箱上连线,利用iMPACT进行程序下载。

4、在实验箱上验证电子琴的功能,观察并记录实验结果.五、实验报告1.music的VHDL 源程序:library ieee;use ieee.std_logic_1164.all;entity music isport(kin: std_logic_vector(0 to 15);spk_out: out std_logic;led_out: out std_logic_vector(6 downto 0);index: out std_logic_vector(2 downto 0);clk: in std_logic);end music;architecture stru of music iscomponent tonetabport(index : in INTEGER range 0 to 15;tone : out INTEGER range 0 to 16#3fff#;code : out INTEGER range 0 to 15;high : out STD_LOGIC_VECTOR(2 DOWNTO 0));end component;component tonegenport(clk : in STD_LOGIC;tone : in integer range 0 to 16#3fff#;spks : out STD_LOGIC);end component;component hex2ledport(hex : in integer range 0 to 15;led : out STD_LOGIC_VECTOR(6 downto 0));end component;component keybordport(kin : in STD_LOGIC_VECTOR(0 to 15);kout : out INTEGER range 0 to 15);end component;signal kout: integer range 0 to 15;signal tone: INTEGER range 0 to 16#3fff#;signal digit: integer range 0 to 15;beginu1: keybord port map (kin=>kin,kout=>kout);u2: tonetab port map (index=>kout,tone=>tone,code=>digit,high=>index); u3: tonegen port map (clk=>clk,tone=>tone,spks=>spk_out);u4: hex2led port map (hex=>digit,led=>led_out);end stru;2. hex2led的VHDL 源程序library IEEE;use IEEE.STD_LOGIC_1164.all;entity hex2led isport(hex : in integer range 0 to 15;led : out STD_LOGIC_VECTOR(6 downto 0));end hex2led;architecture rtl of hex2led issignal data : std_logic_vector(6 downto 0);beginled<=not data;with hex selectdata<= "1111001" when 1, --1"0100100" when 2, --2"0110000" when 3, --3"0011001" when 4, --4"0010010" when 5, --5"0000010" when 6, --6"1111000" when 7, --7"0000000" when 8, --8"0010000" when 9, --9"0001000" when 10, --A"0000011" when 11, --b"1000110" when 12, --C"0100001" when 13, --d"0000110" when 14, --E"0001110" when 15, --F"1000000" when others; --0end rtl;3. keybord 的VHDL 源程序library IEEE;use IEEE.STD_LOGIC_1164.all;entity keybord isport(kin : in STD_LOGIC_VECTOR(0 to 15);kout : out INTEGER range 0 to 15 );end keybord;architecture rtl of keybord issignal data:std_logic_vector(0 to 15); begindata<=kin;process(data)beginif data(0)='0' then kout<=0;elsif data(1)='0' then kout<=1;elsif data(2)='0' then kout<=2;elsif data(3)='0' then kout<=3;elsif data(4)='0' then kout<=4;elsif data(5)='0' then kout<=5;elsif data(6)='0' then kout<=6;elsif data(7)='0' then kout<=7;elsif data(8)='0' then kout<=8;elsif data(9)='0' then kout<=9;elsif data(10)='0' then kout<=10;elsif data(11)='0' then kout<=11;elsif data(12)='0' then kout<=12;elsif data(13)='0' then kout<=13;elsif data(14)='0' then kout<=14;elsif data(15)='0' then kout<=15;else NULL;end if;end process;end rtl;4. tonegen的VHDL源程序library IEEE;use IEEE.STD_LOGIC_1164.all;entity tonegen isport(clk : in STD_LOGIC;tone : in integer range 0 to 16#3fff#;spks : out STD_LOGIC);end tonegen;architecture rtl of tonegen issignal fullspks:std_logic;begingenspks:process(clk,tone)variable count14: integer range 0 to 16#3fff#;--std_logic_vector(0 to 13);beginif clk'event and clk='1' thenif count14=16#3fff# then --"1111" thencount14:=tone;fullspks<='1';elsecount14:=count14+1;fullspks<='0';end if;end if;end process;delayspks:process(fullspks)variable count2:std_logic;beginif fullspks'event and fullspks='1' thencount2:=not count2;end if;spks<=count2;end process;end rtl;5. tonetab 的VHDL源程序library IEEE;use IEEE.STD_LOGIC_1164.all;entity tonetab isport(index : in INTEGER range 0 to 15;tone : out INTEGER range 0 to 16#3fff#;code : out INTEGER range 0 to 15;high : out STD_LOGIC_VECTOR(2 DOWNTO 0) );end tonetab;architecture rtl of tonetab isbeginprocess(index)begincase index iswhen 0 =>tone<=5021;code<=6;high<="100";when 1 =>tone<=6262;code<=7;high<="100";when 2 =>tone<=6829;code<=1;high<="010";when 3 =>tone<=7872;code<=2;high<="010";when 4 =>tone<=8801;code<=3;high<="010";when 5 =>tone<=9226;code<=4;high<="010";when 6 =>tone<=10007;code<=5;high<="010";when 7 =>tone<=10703;code<=6;high<="010";when 8 =>tone<=11323;code<=7;high<="010";when 9 =>tone<=11607;code<=1;high<="001";when 10 =>tone<=12129;code<=2;high<="001";when 11 =>tone<=12593;code<=3;high<="001";when 12 =>tone<=12805;code<=4;high<="001";when 13 =>tone<=13196;code<=5;high<="001";when 14 =>tone<=13544;code<=6;high<="001";when 15 =>tone<=16383;code<=0;high<="001";when OTHERS=>NULL;end case;end process;end rtl;实验记录:1、设计记录表,记录引脚锁定与连线情况。

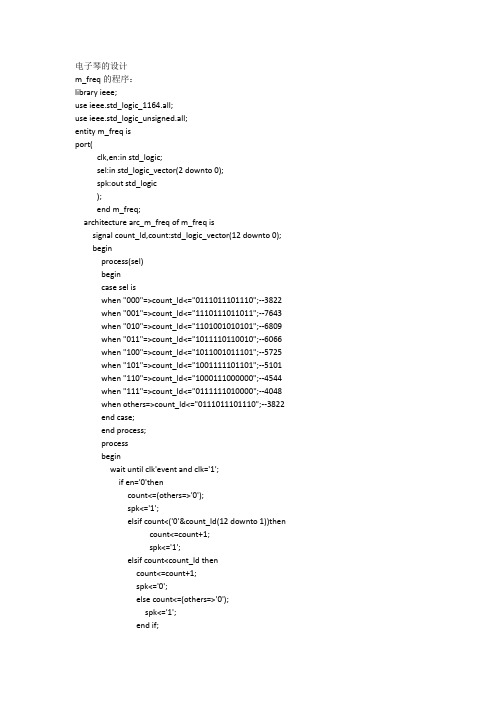

电子琴的设计m_freq的程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity m_freq isport(clk,en:in std_logic;sel:in std_logic_vector(2 downto 0);spk:out std_logic);end m_freq;architecture arc_m_freq of m_freq issignal count_ld,count:std_logic_vector(12 downto 0);beginprocess(sel)begincase sel iswhen "000"=>count_ld<="0111011101110";--3822when "001"=>count_ld<="1110111011011";--7643when "010"=>count_ld<="1101001010101";--6809when "011"=>count_ld<="1011110110010";--6066when "100"=>count_ld<="1011001011101";--5725when "101"=>count_ld<="1001111101101";--5101when "110"=>count_ld<="1000111000000";--4544when "111"=>count_ld<="0111111010000";--4048when others=>count_ld<="0111011101110";--3822end case;end process;processbeginwait until clk'event and clk='1';if en='0'thencount<=(others=>'0');spk<='1';elsif count<('0'&count_ld(12 downto 1))thencount<=count+1;spk<='1';elsif count<count_ld thencount<=count+1;spk<='0';else count<=(others=>'0');spk<='1';end if;end process;end arc_m_freq;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity keyboard isport(k:in std_logic_vector(7 downto 0);sel:out std_logic_vector(2 downto 0);en:out std_logic);end keyboard;architecture arc_keyboard of keyboary isbeginprocess(k);begincase k iswhen "01111111"=>sel<="001";en<='1';when "10111111"=>sel<="010";en<='1';when "11011111"=>sel<="011";en<='1';when "11101111"=>sel<="100";en<='1';when "11110111"=>sel<="101";en<='1';when "11111011"=>sel<="110";en<='1';when "11111101"=>sel<="111";en<='1';when "11111110"=>sel<="000";en<='1';when others=>sel<="000";en<='0';end case;end process;end arc_keyboard;。

《EDA技术实用教程》课程设计课程设计报告课题: EDA电子琴课程名称: EDA技术实用教程学院名称:物理电气信息学院班级: 2011级通信工程(1)班学生姓名:安昱学号: 12011243986 指导教师:杨泽林2013年12月26日EDA技术实用教程课程设计EDA电子琴摘要:本课程设计主要采用EDA技术设计一个简易的八音符电子琴,它可通过按键输入来控制音响从而演奏出已存入的乐曲。

在课程设计中,系统开发平台为Windows XP,程序设计采用VHDL语言,程序运行平台为Quartus II。

然后编写程序实现电子琴的各项功能,使不同的音阶对应不同频率的正弦波,按下不同的键时发出对应频率的声音。

程序通过调试运行,时序仿真,电路功能验证,顺利地实现了设计目标。

关键词:电子琴;EDA;VHDL;音阶;频率1、引言随着信息科学的进步,现代电子产品的性能越来越高,复杂度越来越大,更新步伐也越来越快,电子技术的发展进入了划时代的阶段。

其中电子技术的核心便是电子设计自动化EDA(Electronic Design Automatic)技术。

EDA是指以计算机为工作平台,融合了应用电子技术、计算机技术、智能化技术的最新成果而开发出的电子CAD 通用软件包,它根据硬件描述语言VHDL完成的设计文件,自动完成逻辑编译、化简、分割、综合、优化、布局布线及仿真,直至完成对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

本课程设计就是采用EDA技术描述语言VHDL编程实现简易电子琴的各项功能,是EDA技术应用于实际的一个很好的例子。

1.1 课程设计目的本课程设计主要是基于VHDL文本输入法设计乐曲演奏电路,该系统基于计算机中时钟分频器的原理,采用自顶向下的设计方法来实现,通过按键输入来控制音响或者自动演奏已存入的歌曲。

系统由乐曲自动演奏模块、音调发生模块和数控分频模块三个部分组成。

系统实现是用硬件描述语言VHDL按模块化方式进行设计,然后进行编程、时序仿真、电路功能验证,奏出美妙的乐曲。

数电EDA简易电子琴Verilog设计数字电子技术课程设计--简易电子琴设计专业班级:电子姓名:学号:一、日期:设计任务用Verilog HDL语言设计简易电子琴。

(1)单独从左至右按下S1-S7每个按键后能够各自对应发出“哆来咪发唆啦西”的音乐声;(2)按下最右边按键(S8),同时再配合按下S1-S7键后,发高八度的对应音;(3)按键需要进行“消抖”处理;(4)外部输入脉冲信号频率为1mhz;(5)扩展要求:自主设计(增加低8度功能)。

二、实验目的1、学习verilogHDL语言的基本运用,能够利用其进行简单编程;2、学习使用QuartusⅡ的基本操作,能够利用其进行简单的设计;3、结合实践加深对理论知识的理解。

三、设计原理1)喇叭的振动频率不同,导致产生不同的声音;振动频率越低,声音越低沉,振动频率越高,声音越尖锐。

题目中音乐基本音的“哆”对应频率为523Hz 、“来”对应频率为587Hz 、“咪”对应频率为659Hz 、“发”对应频率为698Hz 、“唆”对应频率为784Hz 、“啦”对应频率为880Hz 、“西”对应频率为998Hz。

低8度音:基本音频率/2,例如低音1的频率为523/2=。

高8度音:基本音频率×2,例如高音1的频率为523×2=1046Hz.。

不同的频率产生利用给定的时钟脉冲来进行分频实现。

(2)消抖的原理:按键默认输入逻辑‘1’,当有按键按下时对应的输入为逻辑‘0’(但会存在抖动),当FPGA开始检测到该引脚从‘1’变为‘0’后开始定时(按键抖动时间大约10ms),定时时间结束后若该引脚仍然为‘0’则表示确实发生按键按下,否则视为抖动而不予以理会;按键松开过程的消抖处理和按下时原理一样。

(3)原理框图四、程序设计消抖模块module xiaodou(key_in,key_out,clk);input key_in;input clk;output key_out;reg key_out;reg [2:0]presta;integer q;parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100,s5=3'b101,s6=3'b110,s7=3'b111;always@(posedge clk)begincase(presta)s0:beginkey_out<=0;q<=0;if(key_in==1)presta<=s0; elsepresta<=s1; ends1:beginkey_out<=0; if(q>9999) presta<=s2; elseq<=q+1; ends2:beginkey_out<=0; q<=0;if(key_in==1) presta<=s0; elsepresta<=s3; ends3:beginkey_out<=1; q<=0;if(key_in==0) presta<=s3; elsepresta<=s4; ends4:beginkey_out<=1;if(q>44444)presta<=s5;elseq<=q+1;ends5:beginq<=0;if(key_in==1)presta<=s0;elsepresta<=s3;ends6:beginpresta<=s0;ends7:beginpresta<=s0;endendcaseendend module按键模块module anjian(a,b,c,d,e,f,g,h,i,qout); input a,b,c,d,e,f,g,h,i;output [10:0] qout;reg [8:0] q;reg [10:0] qout;always@(a or b or c or d or e or f or g or h or i) begin q[0]=i;q[1]=h;q[2]=g;q[3]=f;q[4]=e;q[5]=d;q[6]=c;q[7]=b;q[8]=a;endalways@(q)begincase(q)9'b000000011:qout<=11'b00000000000;9'b000000001:qout<=11'b00000000000;9'b000000000:qout<=11'b00000000000;9'b000000010:qout<=11'b00000000000;default:qout<=qout;endcaseendendmodule分频模块module fenpin(clk_1M,yuzhi,pl_out);input clk_1M;input [10:0]yuzhi;reg [10:0]q;output pl_out;reg pl_out;always@(posedge clk_1M)beginif(yuzhi>0)beginif(q<yuzhi)< p="">beginq<=q+1;pl_out<=0;endelsebeginq<=11'b00000000000;pl_out<=1;endendelsebeginq<=11'b00000000000;pl_out<=1;endendendmodule五、原理图及仿真波形图六、心得体会由于之前对本次设计所需知识了解较少,所以在实验过程中遇到了很多的困难,真的很难,但是同样在解决各种困难的过程中也有所收获。

EDA课程设计报告书--八音电子琴燕山大学EDA课程设计报告书题目:八音电子琴姓名:张永义班级:11级电子卓越〔试点〕学号:学院:信息科学与工程学院日期:2013-11-12指导教师:常丹华成绩:一、设计题目及要求1.设计题目八音电子琴2.设计要求〔1〕能发出1,2,3,4,5,6,7,1八个音。

〔2〕用按键作为键盘。

〔3〕C调到B调对应频率为。

调频率〔Hz〕Ċ〔高音〕261.63*2BAGFEDC二、设计过程及内容〔包括○1总体设计的文字描述,即由哪几个局部构成的,各个局部的功能及如何实现方法;○2主要模块比拟详尽的文字描述,并配以必要的图片加以说明,但图片数量无需太多〕根据命题的要求,要使扬声器发音,需要在其输入信号端连接一个对应频率的方波信号.实验使用的信号源可以提供从几Hz到几MHz 不等的信号频率,自然可以想到本实验命题的关键是一个具有相应分频比的分频器。

考虑到硬件(按钮)在实际工作过程中会因元件的接触产生一些不可防止的抖动脉冲电平,会对实验造成影响,因此需要在按键接入线路中安装防抖动电路。

分频器连接完成后会产生一个预定频率的周期脉冲.但是实验要求的方波其占空比应该为1:1,因此在输出脉冲端加装一个T触发器,每次脉冲到达触发器的时候输出便会跳变电平,这就到达了驱动扬声器的条件。

〔1〕模块一:防抖电路模块。

作用:用来消除在按键接入线路时不可防止抖动脉冲电平对试验造成的影响。

〔2〕模块二:分频器模块。

作用:将高频时钟信号转化为试验所需要的低频时钟信号。

〔3〕模块三:利用T触发器实现占空比的改变,使输出方波占空比为1:1。

总的电路图如图1所示:图1八音电子琴总图实验箱上的按钮是常态输出为高电平,按下输出为低电平,所以在八个按钮接口的后面分别接入非门,实现常态输出为低电平,按下输出为高电平。

在其后接入或门,使满足至少一个按钮输入高电平时,就能控制扬声器发音,再T触发器的输出端和或门的输出端接与门,以此来实现相应的按钮来控制相应频率的音阶通过扬声器发音。

数电EDA简易电子琴Verilog- 设计.数字电子技术课程设计--简易电子琴设计专业班级:电子姓名:学号:日期: 2015.6.5一、设计任务用Verilog HDL语言设计简易电子琴。

(1)单独从左至右按下S1-S7每个按键后能够各自对应发出“哆来咪发唆啦西”的音乐声;(2)按下最右边按键(S8),同时再配合按下S1-S7键后,发高八度的对应音;(3)按键需要进行“消抖”处理;(4)外部输入脉冲信号频率为1mhz;(5)扩展要求:自主设计(增加低8度功能)。

二、实验目的1、学习verilogHDL语言的基本运用,能够利用其进行简单编程;2、学习使用QuartusⅡ7.0的基本操作,能够利用其进行简单的设计;3、结合实践加深对理论知识的理解。

三、设计原理1)喇叭的振动频率不同,导致产生不同的声音;振动频率越低,声音越低沉,振动频率越高,声音越尖锐。

题目中音乐基本音的“哆”对应频率为523Hz 、“来”对应频率为587Hz 、“咪”对应频率为659Hz 、“发”对应频率为698Hz 、“唆”对应频率为784Hz 、“啦”对应频率为880Hz 、“西”对应频率为998Hz。

低8度音:基本音频率/2,例如低音1的频率为523/2=261.5Hz。

高8度音:基本音频率×2,例如高音1的频率为523×2=1046Hz.。

不同的频率产生利用给定的时钟脉冲来进行分频实现。

(2)消抖的原理:按键默认输入逻辑‘1',当有按键按下时对应的输入为逻辑‘0'(但会存在抖动),当FPGA开始检测到该引脚从‘1'变为‘0'后开始定时(按键抖动时间大约10ms),定时时间结束后若该引脚仍然为‘0'则表示确实发生按键按下,否则视为抖动而不予以理会;按键松开过程的消抖处理和按下时原理一样。

)原理框图3(.四、程序设计消抖模块module xiaodou(key_in,key_out,clk); input key_in;input clk;output key_out;reg key_out;reg [2:0]presta;integer q;parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100,s5=3'b101,s6=3'b110,s7=3'b111;always@(posedge clk)begincase(presta)s0:beginkey_out<=0;q<=0;if(key_in==1)presta<=s0;elsepresta<=s1;ends1: beginkey_out<=0;if(q>9999)presta<=s2;elseq<=q+1;ends2:beginkey_out<=0;q<=0;if(key_in==1)presta<=s0;elsepresta<=s3;ends3:beginkey_out<=1;q<=0;if(key_in==0)presta<=s3;elsepresta<=s4;ends4:beginkey_out<=1;if(q>44444)presta<=s5;elseq<=q+1;ends5:beginq<=0;if(key_in==1)presta<=s0;elsepresta<=s3;ends6:beginpresta<=s0;ends7:beginpresta<=s0;endendcaseendend module按键模块module anjian(a,b,c,d,e,f,g,h,i,qout); input a,b,c,d,e,f,g,h,i;output [10:0] qout;reg [8:0] q;reg [10:0] qout;always@(a or b or c or d or e or f or g or h or i) beginq[0]=i;q[1]=h;q[2]=g;q[3]=f;q[4]=e;q[5]=d;q[6]=c;q[7]=b;q[8]=a;endalways@(q)begincase(q)9'b100000000:qout<=11'b01110111100;9'b010000000:qout<=11'b01101010011;9'b001000000:qout<=11'b010********;9'b000100000:qout<=11'b010********;9'b000010000:qout<=11'b010********;9'b000001000:qout<=11'b010********;9'b000000100:qout<=11'b00111110101;9'b100000010:qout<=11'b00111011110;9'b010000010:qout<=11'b00110101010;9'b001000010:qout<=11'b00101111011;9'b000100010:qout<=11'b00101100110; 9'b000010010:qout<=11'b00100111111; 9'b000001010:qout<=11'b00100011100; 9'b000000110:qout<=11'b00011111011;9'b100000001:qout<=11'b11101111000; 9'b010000001:qout<=11'b11010100110; 9'b001000001:qout<=11'b10111101110; 9'b000100001:qout<=11'b10110011000; 9'b000010001:qout<=11'b10011111100; 9'b000001001:qout<=11'b10001110000; 9'b000000101:qout<=11'b01111101010;9'b000000011:qout<=11'b00000000000; 9'b000000001:qout<=11'b00000000000; 9'b000000000:qout<=11'b00000000000; 9'b000000010:qout<=11'b00000000000; default:qout<=qout;endcaseendendmodule分频模块module fenpin(clk_1M,yuzhi,pl_out); input clk_1M;input [10:0]yuzhi;reg [10:0]q;output pl_out;reg pl_out;always@(posedge clk_1M)beginif(yuzhi>0)beginif(q<yuzhi)beginq<=q+1;pl_out<=0;endelsebeginq<=11'b00000000000;pl_out<=1;endendelsebeginq<=11'b00000000000; pl_out<=1;endendendmodule五、原理图及仿真波形图六、心得体会由于之前对本次设计所需知识了解较少,所以在实验过程中遇到了很多的困难,真的很难,但是同样在解决各种困难的过程中也有所收获。

实验十五电子琴设计一、音名与频率的关系:音乐上的十二平均律规定:每两个八度音之间的频率相差一倍。

在这两个八度音之间,分成十二个半音,每两个相邻伴音的频率比为12 2。

另外还规定,音名A的频率为440Hz。

音名B到C、E到F之间为半音,其余为全音。

这样,可计算得从A(简谱的低音6)到a1(简谱的高音6)之间每个音名的频率为:A(6):440Hz a(6):880Hz a1(6):1760HzB(7):493.88Hz b(7):987.76Hzc(1):523.25Hz c1(1):1046.50Hzd(2):587.33Hz d1(2):1174.66Hze(3):659.25Hz e1(3):1318.51Hzf(4):698.46Hz f1(4):1396.92Hzg(5):783.99Hz g1(5):1567.98Hz二、设计要求:设计一个电子琴,要求能演奏音名A到a1之间的全部音阶。

按下一个键,则演奏该音名,并用数码管显示音名,用发光二极管指示高、中、低音。

三、设计提示:本实验由键盘编码,音频输出译码器、分频器组成。

取10MHz信号作为基准。

以基准频率除以上述频率,可得各音名频率的分频系数。

注意,为了减少输出的偶次谐波成分,最后输出应为对称方波。

音频输出译码器实质上是一个多路选择器,根据键盘编码的输出,选择音阶发生器的不同的预置数,分频后输出音频。

分频器可以为加法计数器,以可以为减法计数器,计算预置数时稍有不同,应加以注意。

另外,应根据基准频率和输出频率,来确定计数器的位数。

设计框图如下图所示:电子琴框图四、实验步骤1、启动ISE集成开发环境,创建工程并输入设计源文件。

2、对设计进行时序仿真,分析设计的正确性。

3、锁定引脚,完成设计实现过程。

并在实验箱上连线,利用iMPACT进行程序下载。

4、在实验箱上验证电子琴的功能,观察并记录实验结果.五、实验报告1.music的VHDL 源程序:library ieee;use ieee.std_logic_1164.all;entity music isport(kin: std_logic_vector(0 to 15);spk_out: out std_logic;led_out: out std_logic_vector(6 downto 0);index: out std_logic_vector(2 downto 0);clk: in std_logic);end music;architecture stru of music iscomponent tonetabport(index : in INTEGER range 0 to 15;tone : out INTEGER range 0 to 16#3fff#;code : out INTEGER range 0 to 15;high : out STD_LOGIC_VECTOR(2 DOWNTO 0));end component;component tonegenport(clk : in STD_LOGIC;tone : in integer range 0 to 16#3fff#;spks : out STD_LOGIC);end component;component hex2ledport(hex : in integer range 0 to 15;led : out STD_LOGIC_VECTOR(6 downto 0));end component;component keybordport(kin : in STD_LOGIC_VECTOR(0 to 15);kout : out INTEGER range 0 to 15);end component;signal kout: integer range 0 to 15;signal tone: INTEGER range 0 to 16#3fff#;signal digit: integer range 0 to 15;beginu1: keybord port map (kin=>kin,kout=>kout);u2: tonetab port map (index=>kout,tone=>tone,code=>digit,high=>index); u3: tonegen port map (clk=>clk,tone=>tone,spks=>spk_out);u4: hex2led port map (hex=>digit,led=>led_out);end stru;2. hex2led的VHDL 源程序library IEEE;use IEEE.STD_LOGIC_1164.all;entity hex2led isport(hex : in integer range 0 to 15;led : out STD_LOGIC_VECTOR(6 downto 0));end hex2led;architecture rtl of hex2led issignal data : std_logic_vector(6 downto 0);beginled<=not data;with hex selectdata<= "1111001" when 1, --1"0100100" when 2, --2"0110000" when 3, --3"0011001" when 4, --4"0010010" when 5, --5"0000010" when 6, --6"1111000" when 7, --7"0000000" when 8, --8"0010000" when 9, --9"0001000" when 10, --A"0000011" when 11, --b"1000110" when 12, --C"0100001" when 13, --d"0000110" when 14, --E"0001110" when 15, --F"1000000" when others; --0end rtl;3. keybord 的VHDL 源程序library IEEE;use IEEE.STD_LOGIC_1164.all;entity keybord isport(kin : in STD_LOGIC_VECTOR(0 to 15);kout : out INTEGER range 0 to 15 );end keybord;architecture rtl of keybord issignal data:std_logic_vector(0 to 15); begindata<=kin;process(data)beginif data(0)='0' then kout<=0;elsif data(1)='0' then kout<=1;elsif data(2)='0' then kout<=2;elsif data(3)='0' then kout<=3;elsif data(4)='0' then kout<=4;elsif data(5)='0' then kout<=5;elsif data(6)='0' then kout<=6;elsif data(7)='0' then kout<=7;elsif data(8)='0' then kout<=8;elsif data(9)='0' then kout<=9;elsif data(10)='0' then kout<=10;elsif data(11)='0' then kout<=11;elsif data(12)='0' then kout<=12;elsif data(13)='0' then kout<=13;elsif data(14)='0' then kout<=14;elsif data(15)='0' then kout<=15;else NULL;end if;end process;end rtl;4. tonegen的VHDL源程序library IEEE;use IEEE.STD_LOGIC_1164.all;entity tonegen isport(clk : in STD_LOGIC;tone : in integer range 0 to 16#3fff#;spks : out STD_LOGIC);end tonegen;architecture rtl of tonegen issignal fullspks:std_logic;begingenspks:process(clk,tone)variable count14: integer range 0 to 16#3fff#;--std_logic_vector(0 to 13);beginif clk'event and clk='1' thenif count14=16#3fff# then --"1111" thencount14:=tone;fullspks<='1';elsecount14:=count14+1;fullspks<='0';end if;end if;end process;delayspks:process(fullspks)variable count2:std_logic;beginif fullspks'event and fullspks='1' thencount2:=not count2;end if;spks<=count2;end process;end rtl;5. tonetab 的VHDL源程序library IEEE;use IEEE.STD_LOGIC_1164.all;entity tonetab isport(index : in INTEGER range 0 to 15;tone : out INTEGER range 0 to 16#3fff#;code : out INTEGER range 0 to 15;high : out STD_LOGIC_VECTOR(2 DOWNTO 0) );end tonetab;architecture rtl of tonetab isbeginprocess(index)begincase index iswhen 0 =>tone<=5021;code<=6;high<="100";when 1 =>tone<=6262;code<=7;high<="100";when 2 =>tone<=6829;code<=1;high<="010";when 3 =>tone<=7872;code<=2;high<="010";when 4 =>tone<=8801;code<=3;high<="010";when 5 =>tone<=9226;code<=4;high<="010";when 6 =>tone<=10007;code<=5;high<="010";when 7 =>tone<=10703;code<=6;high<="010";when 8 =>tone<=11323;code<=7;high<="010";when 9 =>tone<=11607;code<=1;high<="001";when 10 =>tone<=12129;code<=2;high<="001";when 11 =>tone<=12593;code<=3;high<="001";when 12 =>tone<=12805;code<=4;high<="001";when 13 =>tone<=13196;code<=5;high<="001";when 14 =>tone<=13544;code<=6;high<="001";when 15 =>tone<=16383;code<=0;high<="001";when OTHERS=>NULL;end case;end process;end rtl;实验记录:1、设计记录表,记录引脚锁定与连线情况。