基于TSMC55工艺的ELC流程制盐工艺流程图

- 格式:doc

- 大小:19.67 KB

- 文档页数:11

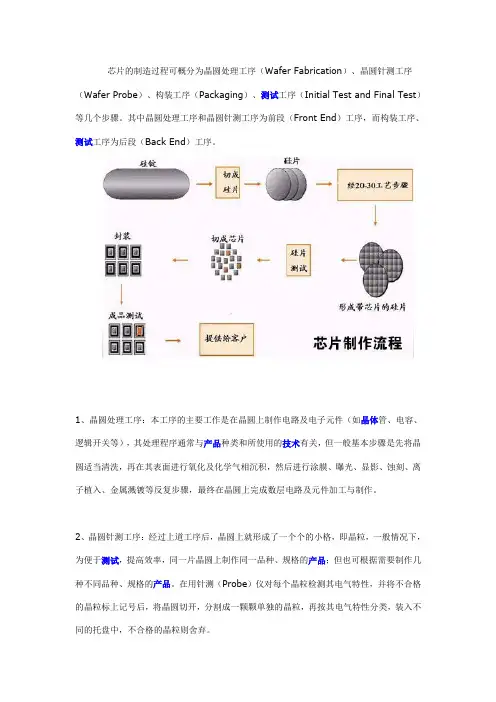

芯片的制造过程可概分为晶圆处理工序(Wafer Fabrication)、晶圆针测工序(Wafer Probe)、构装工序(Packaging)、测试工序(Initial Test and Final Test)等几个步骤。

其中晶圆处理工序和晶圆针测工序为前段(Front End)工序,而构装工序、测试工序为后段(Back End)工序。

1、晶圆处理工序:本工序的主要工作是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。

2、晶圆针测工序:经过上道工序后,晶圆上就形成了一个个的小格,即晶粒,一般情况下,为便于测试,提高效率,同一片晶圆上制作同一品种、规格的产品;但也可根据需要制作几种不同品种、规格的产品。

在用针测(Probe)仪对每个晶粒检测其电气特性,并将不合格的晶粒标上记号后,将晶圆切开,分割成一颗颗单独的晶粒,再按其电气特性分类,装入不同的托盘中,不合格的晶粒则舍弃。

3、构装工序:就是将单个的晶粒固定在塑胶或陶瓷制的芯片基座上,并把晶粒上蚀刻出的一些引接线端与基座底部伸出的插脚连接,以作为与外界电路板连接之用,最后盖上塑胶盖板,用胶水封死。

其目的是用以保护晶粒避免受到机械刮伤或高温破坏。

到此才算制成了一块集成电路芯片(即我们在电脑里可以看到的那些黑色或褐色,两边或四边带有许多插脚或引线的矩形小块)。

4、测试工序:芯片制造的最后一道工序为测试,其又可分为一般测试和特殊测试,前者是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。

经测试后的芯片,依其电气特性划分为不同等级。

而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。

基于TSMC55工艺的ELC流程

孟少鹏;马强

【期刊名称】《中国集成电路》

【年(卷),期】2010(19)6

【摘要】相对于TSMC65纳米工艺,TSMC55纳米工艺提供了更小的面积、更快的速度.ELC不仅可以检查厂商提供的65纳米标准单元库,还可以产生相应的55纳米标准单元库.本文首先介绍了ELC特征化技术原理,在没有相应ARM55标准单元库的情况下,通过对ARM65标准单元库进行ELC特征化流程,得到速度更快的ARM 55标准单元库.并将其应用在实际的设计中进行综合,综合结果与厂商提供的经验值一致.

【总页数】4页(P44-47)

【作者】孟少鹏;马强

【作者单位】华东电子工程研究所,合肥,230031;华东电子工程研究所,合

肥,230031

【正文语种】中文

【相关文献】

1.吸收稳定系统工艺流程现状和新流程开发(I)--工艺流程现状 [J], 陆恩锡;张慧娟;朱霞林

2.吸收稳定系统工艺流程现状和新流程开发(Ⅱ)--新的节能工艺流程开发 [J], 陆恩锡;张慧娟;朱霞林

3.珠海全志科技采用TSMC55纳米工艺成功推出A10芯片平台 [J],

4.珠海全志采用TSMC55纳米工艺成功推出A10芯片平台 [J],

5.具有极高γ值的ELC—BH钢板的新工艺 [J], 关小军;胡小军

因版权原因,仅展示原文概要,查看原文内容请购买。

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (4)2、然后桌面右键重新打开Terminal (6)双反相器的后端设计流程 (7)一、schematic电路图绘制 (7)二、版图设计 (21)画版图一些技巧: (29)三、后端验证和提取 (30)第三节后端仿真 (37)其它知识 (40)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在windowXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top 处单击这些节点即可查看波形如果有多个子电路请单击此处的Top 查看如果要查看测量语句的输出结果请查看 .MTO 文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence 软件)一、开启linux 系统双击桌面虚拟机的图标选择Power on this virtual machine开启linux之后在桌面右键选择Open Terminal输入xhost local:命令按回车之后输入su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

集成电路ic工艺流程

集成电路(IC)的制作过程,就像精心烹制一道高科技大餐,一步步来解析:

画蓝图:

首先,工程师们坐下来想:“我们要这个芯片干啥?”确定好它需要完成的任务。

接着,他们像搭积木一样,在电脑上设计出由各种小开关(逻辑门)组成的电路图。

然后,设计师得把这些电路“摆放”到一个虚拟的芯片板子上,规划好每个部分的位置,这就叫版图设计。

最后,用电脑模拟一下,看看设计出来的芯片能不能正常工作,这一步相当于在厨房里试菜。

硅片烹饪:

拿一块超级纯净的硅,做成又圆又平的晶圆,就像准备一张完美的烤盘。

在硅片上做“化学魔法”,加上一层薄薄的绝缘外套(氧化层),再巧妙地加入杂质,让它有的地方能导电,有的不能,这就形成了电路的基本元素。

开始“光影魔术手”——光刻,用光照和特殊胶水在硅片上印上电路图案,就像在蛋糕上做精细的糖霜装饰。

反复用化学方法“雕刻”和“堆积”,加层减层,做出多层的复杂电路,就像一层层叠加不同的食材。

打包出厂:

把晶圆切成一块块小芯片,每块都得先简单测验下,看看是不是都能“跑起来”。

给这些小芯片穿上“保护服”,用金属线连上外面的世界,就像给美食打包,方便食用。

再来一次全面体检,确认每个芯片都是健康强壮的,能胜任任务。

最后,根据它们的表现分等级,贴上标签,就可以出厂啦!

整个过程非常精细,而且全是高科技设备自动完成,保证了我们日常使用的电子设备里,那些微小而强大的芯片能够顺利诞生。

基于TSMC55工艺的ELC流程制盐工艺流程图摘要:相对于TSMC65纳米工艺,TSMC55纳米工艺提供了更小的面积、更快的速度。

ELC不仅可以检查厂商提供的65纳米标准单元库,还可以产生相应的55纳米标准单元库。

本文首先介绍了ELC特征化技术原理,在没有相应ARM55标准单元库的情况下,通过对ARM65标准单元库进行ELC特征化流程,得到速度更快的ARM 55标准单元库。

并将其应用在实际的设计中进行综合,综合结果与厂商提供的经验值一致。

关键词:ELC,GDS,ShrinkELC process with TSMC55 technologyMENG Shao-peng, MA qiang(East China Research Institute of Electronic Engineering, Hefei 230031,China)Abstract: Compared with TSMC 65 nm technology, TSMC 55 nm technology can provide smaller area and higher frequency. ELC (Encounter Library Characterization) not only can check the 65nm standard cell library from foundry, but also can generate the corresponding 55 nm standard cell library. This paper firstly presents a simple view of the ELC design concept, then we generate the 55nm standard cell library by applying ELC design flow on 65nm standard cell library and use it in an actual design synthesis. Experimental results demonstrate perfect consistency with values provided by foundry.Keyword:ELC;GDS;Shrink1前言随着超深亚微米技术的不断发展,特别是当设计转向90 nm以下工艺节点之后,流片成本不断增大,同时新的工艺由于其不稳定性导致流片良率下降。

基于TSMC55工艺的ELC流程制盐工艺流程图摘要:相对于TSMC65纳米工艺,TSMC55纳米工艺提供了更小的面积、更快的速度。

ELC不仅可以检查厂商提供的65纳米标准单元库,还可以产生相应的55纳米标准单元库。

本文首先介绍了ELC特征化技术原理,在没有相应ARM55标准单元库的情况下,通过对ARM65标准单元库进行ELC特征化流程,得到速度更快的ARM 55标准单元库。

并将其应用在实际的设计中进行综合,综合结果与厂商提供的经验值一致。

关键词:ELC,GDS,ShrinkELC process with TSMC55 technologyMENG Shao-peng, MA qiang(East China Research Institute of Electronic Engineering, Hefei 230031,China)Abstract: Compared with TSMC 65 nm technology, TSMC 55 nm technology can provide smaller area and higher frequency. ELC (Encounter Library Characterization) not only can check the 65nm standard cell library from foundry, but also can generate the corresponding 55 nm standard cell library. This paper firstly presents a simple view of the ELC design concept, then we generate the 55nm standard cell library by applying ELC design flow on 65nm standard cell library and use it in an actual design synthesis. Experimental results demonstrate perfect consistency with values provided by foundry.Keyword:ELC;GDS;Shrink1前言随着超深亚微米技术的不断发展,特别是当设计转向90 nm以下工艺节点之后,流片成本不断增大,同时新的工艺由于其不稳定性导致流片良率下降。

同时,电子产品特别是便携式消费电子类产品设计规模不断增大,导致芯片面积、功耗也线性增长。

这在客观上就要求设计师追求更短的沟道长度即更加先进的工艺,以便改善芯片的面积、功耗等等,这样就与前面提到的新工艺带来的成本、良率等问题产生矛盾。

在这种情况下,生产厂商提供了half_node工艺,即在原有工艺基础上通过shrink GDS文件的尺寸,来减少芯片的尺寸,比如65 nm的产品通过shrink变成55 nm的产品。

下面以TSMC 65 nm 工艺Shrink 到55 nm工艺的过程为例,Shrink带来的好处是芯片流片出来的面积是原来的81%,而整个芯片的速度可以增加5%~10%。

TSMC 55 nm工艺需要相应的库即55 nm库来支持,从而实现综合及物理实现过程。

但是有些IC公司只有支持标准工艺的库而缺乏half_node工艺的库。

本文通过对ARM提供的基于TSMC 65 nm库进行ELC的流程,得到 55 nm 的标准单元库,经过综合得到shrink后芯片的时序结果。

2ELC特征化技术ELC (Encounter Library Characterizer)[1],在安装sign off 工具ETS时会自动安装在其子文件夹下。

ELC通过提取原有库文件,建立仿真环境,然后通过调用仿真工具(HSPICE、SPECTRE、ELDO)对库里的标准单元进行仿真并且得到仿真结果。

ELC主要有以下步骤:(1)分析spice格式下的电路类型、功能、逻辑结构。

(2)产生电路的功能模型。

(3)生成电路的定义文件,包括PIN之间的延时、方向等特性。

(4)定义仿真环境,包括电压、温度、输入斜率、输出负载等参数。

(5)启动并执行仿真工具。

(6)产生ALF文件,通过ALF文件转换成需要的.LIB格式。

simulation setup file是由db_prepare命令产生,默认的文件名为elc.st,在产生仿真文件之前需在elfg中指定原始的库文件,仿真文件就是从该库文件抽取出来的。

model setup file 的内容包括spice model 的路径以及指定的corner。

其格式如下所示:.lib‘/home/work/elc_run/CLN55GPOJS_1d8_1k_v1d 1p2.l”TT3基于TSMC 55工艺的ELC流程库由ARM提供,为了提高频率、减小芯片面积,需要走half_node 流程,即将65 nm工艺缩小到55 nm的工艺,同时ARM并未提供55 nm 的标准单元库。

为了产生ARM55纳米标准单元库,首先将65 nm标准单元的GDS2文件读入Calibre[2],并且调入TSMC提供的55 nm PDK的DRC、LVS RULE文件,确定无DRC、LVS错误。

并且由Calibre XRC抽取库文件的参数,得到带由寄生参数的spice list。

XRC抽取寄生参数分为三个步骤(1)抽取得到PHDB文件。

(2)抽取得到PDB文件。

(3)抽取得到带寄生参数的spice list。

其中PHDB文件包含了版图信息、电路连接关系,PDB文件包含了每个NET的参数信息,最后生成的带寄生参数的spice list用来在ELC仿真。

需要注意的是在分别执行三个步骤的RULE file 应该是同一个,即TSMC 55 nm工艺PDK提供的SVRF文件。

下面是此次实验中elfg文件的内容,其中EC_SIM_TYPE = ”SPECTRE”,指定了仿真工具为SPECTRE。

仿真工具可以为SPECTRE、HSPICE、ELDO。

EC_CHAR = “ECSM-TIMING”;指定了仿真种类即进行时序的仿真,同时还可以定义需要的仿真种类例如功耗等。

SUBCKT = “tcbn55gplus_100b_lpe.spi”指定了带寄生数的spice list。

EC_AVERAGE_PIN_CAP设为3是在仿真提取输入PIN电容值的时候取三个点的平均值。

EC_BI_DARTIO设置为1.1,是设置bisection仿真时候,采用pass/fail方式时,取pass/fail点的10%为限。

EC_HOLD_INTERNAL_FLAG=1是设置在提取hold值时,采用内部节点的方式。

DESIGNS可以选择需要进行ELC的标准单元。

SETUP文件可以采用db_prepare ?create_setup的命令从原始TSMC65的库产生一个样本。

XDESIGNS指定了不需要进行ELC的标准单元。

* * * * * *EC_SIM_USE_LSF = 1;EC_SIM_LSF_PARALLEL = 4;EC_SIM_LSF_CMD = ””;EC_SIM_NAME = ”spectre”;EC_SIM_TYPE = ”SPECTRE”EC_SPICE_SIMPLIFY = 1;EC_AVERAGE_PIN_CAP = 3;EC_BI_DRATIO = 1.1;EC_HOLD_INTERNAL_FLAG = 1;EC_ALF_SIGNIFICANT = 4;EC_SIM_SUPPLY1_NAMES=“VDD VDDL”;EC_SIM_SUPPLY0_NAMES = “VSS”;DESIGNS = “*”;SETUP = “tsmc55g.st”;MODEL = “model.setup”;PROCESS = “TT”;XDESIGNS = “LVL* ISO* TIEH TIEL DCAP* G*”;以下为ELC运行脚本文件内容:* * * * *db_open tsmc55g_tc_25db_preparefdb_spieces spectre keep_logkeep_work statedb_out lib tsmc55g_tc_25.libprocess TT stateoutput_slew_ratio 0.8db_close4ELC结果与分析本次实验将对ARM 65 shrink后(即55纳米)的单元库进行ELC,提前得到设计在进行shrink后的性能。

以低阈值电压的单元库中BUFX4MA12TL[3]为例,即将elfg文件中DESIGNS 设置为“BUFX4MA12TL”。

在ARM提供的65纳米标准单元库中BUFX4MA12TL原来的时序lookup_table如图1所示。

在进行ELC处理之后,BUFX4MA12TL(shrink为55纳米的标准单元)的时序lookup_table 变成如图2所示。

通过对两个lookup_table的比较,可以看出在相同的条件下,ARM 65纳米标准单元库中BUFX4MA12TL 在Shrink后,自身延迟比原来减小了10%~15%。

同时将所有标准单元进行Shrink并产生新的单元库,采用新的单元库进行综合,综合结果改善了约10%,该结果与厂商提供的经验值相吻合。

5结束语本文提出了基于TSMC55工艺的ELC流程,并且将ARM提供的65纳米标准单元BUFX4MA12TL通过ELC产生了55纳米标准单元的BUFX4MA12TL。

将前后二者比较,发现后者比前者快10%~15%。

将65纳米单元库整体转换成55纳米标准单元库,同时分别采用二者进行综合,其综合结果与厂商提供的经验值一致。

__[1]CADENCE. “Encounter Library Characterizer User Guide” . V8.1.1[2]MENTOR. “Calibre xRC User’s Manual”. Vxx.2[3]ARM.“TSMC 65nm CLN65G+LVT Process 12-Track Advantage v2.1 Standard Cell Library Aatabook”内容仅供参考。