数电第二章参考答案

- 格式:docx

- 大小:204.40 KB

- 文档页数:3

数字电子技术第二章(逻辑门电路)作业及答案第二章(逻辑门电路)作业及答案1.逻辑门电路如下图所示:(1)电路均为TTL电路,试写出各个输出信号的表达式。

(2)电路若改为CMOS电路,试写出各个输出信号的表达式。

答案:(1),,,(2),,,2、已知TTL反相器的电压参数为V IL(max)=0.8V,V OH(min)=3V,V TH=1.4V,V IH(min)=1.8V,V OL(max)=03V,V CC=5V,试计算其高电平噪声容限V NH和低电平噪声容限V NL。

答案:V NL= V IL(max) - V OL(max)=0.5V,V NH= V OH(min) - V IH(min) =1.2V。

3、试写出图2-1、图2-2所示逻辑电路的逻辑函数表达式。

解:(1)(2)4、试分析图2-3所示MOS电路的逻辑功能,写出Y端的逻辑函数式,并画出逻辑图。

5、试简要回答下列问题。

(1)有源(图腾柱)输出与集电极开路(OC)输出之间有什么区别?解:OC门输出端只能输出低电平和开路状态,其输出级需要上拉电阻才能输出高电平,且上拉电源可以与芯片电源不同,因此常用于不同电源电压芯片之间实现信号电平变换,OC门输出端可以并联实现线与;有源输出可以输出低电平与高电平,两个有源输出端连接在一起时,若是一个输出端输出高电平,另外一个输出端输出低电平时,可引起较大电流损坏输出级。

(2)TTL逻辑电路输入端悬空时,可视为输入高电平信号处理,而CMOS逻辑电路输入端则不允许悬空使用,试说明其原因。

解:因为CMOS电路的输入端具有非常高的输入阻抗,容易受到干扰,一旦受到干扰后,会使输出电平发生转换,产生功耗,因此输入端不能悬空,应该连接确定的逻辑电平。

6.请查阅74LS00芯片手册(常规温度范围的),回答如下问题:(1)电源电压范围;(2)输出高电平电压范围;(3)输出低电平电压范围;(4)输入高电平电压范围;(5)输入低电平电压范围;(6)该芯片的电源电流;(7)典型传播延迟时间;(8)扇出系数。

习题目录2.1 (2)2.2 (2)2.3 (2)2.4 (3)2.5 (3)2.6 (4)2.7 (4)2.8 (4)2.9 (4)2.10 (4)2.11 (5)2.12 (5)2.13 (7)2.14 (8)2.1 有A 、B 、C 三个输入信号,试列出下列问题的真值表,并写出最小项表达式∑m ( )。

(1)如果A 、B 、C 均为0或其中一个信号为1时。

输出F=1,其余情况下F=0。

(2)若A 、B 、C 出现奇数个0时输出为1,其余情况输出为0。

(3)若A 、B 、C 有两个或两个以上为1时,输出为1,其余情况下,输出为0。

F 1m 4)F 2m )3m 7)2.2 试用真值表证明下列等式:(1)A ⎺B+B ⎺C+A ⎺C=ABC+⎺A ⎺B ⎺C (2)⎺A ⎺B+⎺B ⎺C+⎺A ⎺C=AB BC AC 证明:(1)真值表相同,所以等式成立。

(真值表相同,所以等式成立。

2.3 对下列函数,说明对输入变量的哪些取值组合其输出为1? (1)F (A,B,C )=AB+BC+AC(2)F (A,B,C )=(A+B+C)(⎺A+⎺B+⎺C) (3)F (A,B,C )=(⎺AB+⎺BC+A ⎺C)AC解:本题可用真值表、化成最小项表达式、卡诺图等多种方法求解。

(1)F 输出1的取值组合为:011、101、110、111。

(2)F 输出1的取值组合为:001、010、011、100、101、110。

(3)F输出1的取值组合为:101。

2.4试直接写出下列各式的反演式和对偶式。

(1)F(A,B,C,D,E)=[(A⎺B+C)·D+E]·B(2) F(A,B,C,D,E)=AB+⎺C⎺D+BC+⎺D+⎺CE+B+E(3) F(A,B,C)=⎺A⎺B+C ⎺AB C解:(1) ⎺F=[(⎺A+B)·⎺C+⎺D]·⎺E+⎺BF'=[(A+⎺B)·C+D]·E+B(2) ⎺F=(⎺A+⎺B)(C+D)·(⎺B+⎺C)·D·(C+⎺E)·⎺B·⎺EF'=(A+B)(⎺C+⎺D)·(B+C)·⎺D·(⎺C+E)·B·E(3)⎺F=(A+B)·⎺C+ A+⎺B+CF'=(⎺A+⎺B)·C+⎺A+B+⎺C2.5用公式证明下列等式:(1)⎺A⎺C+⎺A⎺B+BC+⎺A⎺C⎺D=⎺A+BC(2)AB+⎺AC+(⎺B+⎺C) D=AB+⎺AC+D(3)⎺BC⎺D+B⎺CD+ACD+⎺AB⎺C⎺D+⎺A⎺BCD+B⎺C⎺D+BCD=⎺BC+B⎺C+BD(4)A⎺B⎺C+BC+BC⎺D+A⎺BD=⎺A + B +⎺C+⎺D证明:(1) ⎺A⎺C+⎺A⎺B+BC+⎺A⎺C⎺D ——⎺A⎺C⎺D被⎺A⎺C削去=⎺A(⎺B+⎺C)+BC=⎺A BC+BC ——削去互补因子=⎺A+BC(2) AB+⎺AC+(⎺B+⎺C) D=AB+⎺AC+BC D+BC ——增加冗余因子BC,为了削去BCD中的BC =AB+⎺AC+D(3)⎺BC⎺D+B⎺CD+ACD+⎺AB⎺C⎺D+⎺A⎺BCD+B⎺C⎺D+BCD=⎺BC⎺D+BD+ACD+⎺AB⎺C⎺D+⎺BCD+B⎺C⎺D ——B⎺CD与BCD合并成BD=⎺BC⎺D+BD+ACD+⎺AB⎺C⎺D+⎺BCD+B⎺C ——BD与B⎺C⎺D削去互补因子=⎺BC⎺D+BD+ACD+⎺BCD+B⎺C ——⎺AB⎺C⎺D被B⎺C削去=⎺BC+BD+ACD+B⎺C ——⎺BC⎺D与⎺BCD合并=⎺BC+BD+CD+ACD+B⎺C ——增加CD,可削去ACD=⎺BC+B⎺C+BD(4)A⎺B⎺C+BC+BC⎺D+A⎺BD=A⎺B⎺C (BC+BC⎺D)+⎺A+B+⎺D ——BC+BC⎺D削去互补因子=A⎺B⎺C (⎺B+⎺C+⎺D)+⎺A+B+⎺D=A⎺B⎺C +A⎺B⎺C⎺D+⎺A+B+⎺D=A⎺B⎺C+⎺A+B+⎺D=⎺A+ B +⎺C+⎺D2.6已知⎺ab+a⎺b=a⊕b,⎺a⎺b+ab=a b,证明:(1)a⊕b⊕c=a b c(2)a⊕b⊕c=⎺a ⎺b ⎺c证明:(1)a⊕b⊕c=(a⊕b)⊕c=a⊕b · c+(a⊕b)·⎺c=(a b)·c+ a b⎺c=a b c(2)(a⊕b)⊕c = (a⊕b) c=a b c=a b ⎺c=⎺a ⎺b ⎺c2.7试证明:(1)若⎺a⎺b+ a b=0则a x+b y=a⎺x + b⎺y证明:⎺a⎺b+ a b=0 即a b=0 ∴a =⎺bax + by =⎺bx + by = ⎺bx · by=(b+⎺x)(⎺b+⎺y)=b⎺y+⎺b⎺x+⎺x⎺y=a⎺x+b⎺y(2)若⎺a b+a⎺b=c,则⎺a c + a⎺c=b证明:a⊕b=c => a⊕b⊕c=c⊕c => a⊕b⊕c=0 => a⊕b⊕c⊕b=0⊕b => a⊕c=b2.8将下列函数展开成最小项之和:(1)F(ABC)=A+BC(2)F(ABCD)=(B+⎺C)D+(⎺A+B) C(3)F(ABC)=A+B+C+⎺A+B+C解:(1)F(ABC)=A+BC=A(B+⎺B)(C+⎺C)+(A+⎺A)BC=⎺ABC+A⎺B⎺C+A⎺BC+AB⎺C=∑m(3,4,5,6)(2) F(ABCD)=(B+⎺C)D+(⎺A+B) C=BD+⎺CD+⎺AC+BC=∑m(1,3,5,6,7,9,13,14,15)(3) F(ABC)=A+B+C+⎺A+B+C=∑m(0,2,6)2.9将题2.8中各题写成最大项表达式,并将结果与2.8题结果进行比较。

第二章逻辑门电路第一节重点与难点一、重点:1.TTL与非门外特性(1)电压传输特性及输入噪声容限:由电压传输特性曲线可以得出与非门的输出信号随输入信号的变化情况,同时还可以得出反映与非门抗干扰能力的参数U on、U off、U NH和U NL。

开门电平U ON是保证输出电平为最高低电平时输入高电平的最小值。

关门电平U OFF 是保证输出电平为最小高电平时,所允许的输入低电平的最大值。

(2)输入特性:描述与非门对信号源的负载效应。

根据输入端电平的高低,与非门呈现出不同的负载效应,当输入端为低电平U IL时,与非门对信号源是灌电流负载,输入低电平电流I IL通常为1~1.4mA。

当输入端为高电平U IH时,与非门对信号源呈现拉电流负载,输入高电平电流I IH通常小于50μA。

(3)输入负载特性:实际应用中,往往遇到在与非门输入端与地或信号源之间接入电阻的情况,电阻的取值不同,将影响相应输入端的电平取值。

当R≤关门电阻R OFF时,相应的输入端相当于输入低电平;当R≥ 开门电阻R ON时,相应的输入端相当于输入高电平。

2.其它类型的TTL门电路(1)集电极开路与非门(OC门)多个TTL与非门输出端不能直接并联使用,实现线与功能。

而集电极开路与非门(OC 门)输出端可以直接相连,实现线与的功能,它与普通的TTL与非门的差别在于用外接电阻代替复合管。

(2)三态门TSL三态门即保持推拉式输出级的优点,又能实现线与功能。

它的输出除了具有一般与非门的两种状态外,还具有高输出阻抗的第三个状态,称为高阻态,又称禁止态。

处于何种状态由使能端控制。

3.CMOS逻辑门电路CMOS反相器和CMOS传输门是CMOS逻辑门电路的最基本单元电路,由此可以构成各种CMOS逻辑电路。

当CMOS反相器处于稳态时,无论输出高电平还是低电平,两管中总有一管导通,一管截止,电源仅向反相器提供nA级电流,功耗非常小。

CMOS器件门限电平U TH近似等于1/2U DD,可获得最大限度的输入端噪声容限U NH和U NL=1/2U DD。

2.1 列出下列各函数的真值表。

(1)B A AC C B A F +=),,(; (2)C B A C B A F ⊕⊕=),,(; 答案:2.2 试用真值表证明下列等式成立。

(1)))((C A B A BC A ++=+ 答案:A B C A BC +(A B)(A C)++0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1112.3 分别用摩根定律和反演规则对下列表达式求反。

(1)))((D C B D C B A F +++=; (2)D A D C ABC F ++=; (3))(D C B A CD B A F +++=。

答案:(1) FAB(C D)(B C D)=+++=A B CD BCD +++(2)F ABC CD AD =++ =(A B C)(C D)(A D)++++(3)F AB CD(A BC D)=+++ =AB CD A(BC D)+++2.4 用对偶规则求各式的对偶式。

(2)DE C B D A ++; (3)D C B A +++。

答案:(2) (A D)(B C(D E)+++(3) ABCD2.5 三人表决电路的输入信号A 、B 、C 表示甲、乙、丙三人对议案的态度。

当某人支持该议案时,相应的输入为1,否则为0。

仅当2人或2人以上支持时,该议案才能通过,这时输出F 为1,否则为0。

试导出该电路的真值表并写出其逻辑表达式。

答案:A B C F0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 11F ABC ABC ABC ABC =+++2.6 X =X 2X 1X 0和Y =Y 2Y 1Y 0分别是某数据处理电路的输入和输出,且均为二进制数。

若(1) 0≤X ≤2时,Y =2X ; (2) 3≤X ≤5时,Y =X -1; (3) X ≥6时,Y =X 。

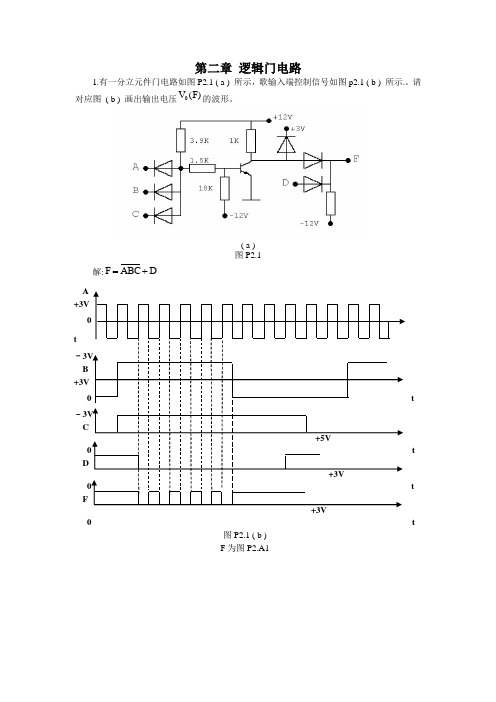

第二章 门电路思考题与习题参考答案: [题2-1]解:图p2-1(a):V v I 7.0-<时,二极管D 导通,否则D 截止。

输出信号1O v 波形如图D2-1(a)所示。

图p2-1 (b):V v I 7.0>时,二极管D 导通,否则D 截止。

输出信号2O v 波形如图D2-1(b)所示。

图p2-1 (c):V v I 7.3-<时,二极管D 导通,否则D 截止。

输出信号3O v 波形如图D2-1(c)所示。

图p2-1 (d):V v I 7.3>时,二极管D 2导通,V v I 7.2-<时,D 1导通,V v V I 7.37.2<<-时, D 1、D 2截止。

输出信号4O v 波形如图D2-1(d)所示。

图D2-1[题2-2]解:图p2-1(a):设三极管导通,mA i B 14.0807.012=-=, mA i C 2.414.030=⨯=而mA I CS8.75.13.012=-=,所以三极管处于导通状态,V v O 7.55.12.412=⨯-= 图p2-1(b):因为0<I v ,三极管截止,V V v CC O 12== 图p2-1(c):设三极管导通,mA i B 28.0407.012=-=,(a)(b)(c)(d)mA i C 4.828.030=⨯=,而mA I CS 8.75.13.012=-=, 所以三极管处于饱和状态,V v v CES O 3.0== [题2-3]解:当TN GS I V v v <=时,TN U 为N 沟道增强型MOS 管的开启电压,此时处于截止状态,此时漏极D 和源极S 之间未形成有效的N 型导电通道, 0=D i ,这个状态为截止状态, D 、S 之间就如同一个断开的开关。

当V V v v TN GS I 2=≥=时,此时处于导通状态。

导通状态时,D 、S 之间形成N 型导电沟道,当GS V 一定时,D 、S 间可近似等效为线性电阻,这个电阻称为导通电阻ON R ,在D 、S 极之间就如同一个导通电阻为ON R 的闭合开关。

思考题:题2.1.1 答:肖特基二极管(SBD)、分流。

题2.1.2 答:基区、滞后。

题2.1.3 答:(A)、(B) 。

题2.1.4 答:对。

题2.2.1 答:A、B。

题2.2.2 答:C、D。

题2.2.3 答:4ns。

题2.2.4 答:(A)、(C)、。

题2.2.5 答:降低、降低。

题2.2.6 答:0、1和三态题2.2.7 答:若一个输出高电平,另一个输出低电平时,会在T4和T5间产生一个大电流,烧毁管子。

OC门“线与”在输出接一电阻和一5-30V电源电压。

题2.2.8 答:能、分时。

题2.2.9 答:1. 为了缩短传输延迟时间,电路中使用肖特基管和有源泄放电路,另外,还将输入级的多发射极管改用SBD代替,由于SBD没有电荷存储效应,因此有利于提高电路的工作速度。

电路中还接入了D3和D4两个SBD,当电路的输出端由高电平变为低电平时,D4经T2的集电极和T5的基极提供了一条通路,一是为了加快负载电容的放电速度,二是为了加速T5的导通过程。

另外,D3经T2的集电极为T4的基极提供了一条放电通路,加快了T4的截止过程。

2. 为降低功耗,提高了电路中各电阻的阻值,将电阻R5原来接地的一端改接到输出端,以减小T3导通时电阻R5上的功耗。

题2.3.1 答:A。

题2.3.2 答:A。

题2.3.3 答:A。

题2.3.4 答:导通。

题2.3.5 答:B、C。

思考题:题2.4.1 答:(A)分流。

题2.4.2 答:(B) 内部电阻和容性负载。

题2.4.3 答:(B) 3.3V;(C)5V;(D) 30V。

题2.4.4 答:CMOS反相器和CMOS传输门。

题2.4.5 答:加入缓冲器保证输出电压不抬高或者降低,正逻辑变负逻辑或者相反,与非变成或非,或者或非变为与非。

题2.4.6 答:(C)低、高。

题2.4.7答:(A) OD门;(B) OC门;(C)三态门。

16题2.4.8 答:(A)驱动大负载;(B)电平移位。

第1章习题与参考答案【题1-1】将以下十进制数转换为二进制数、八进制数、十六进制数。

〔1〕25;〔2〕43;〔3〕56;〔4〕78解:〔1〕25=〔11001〕2=〔31〕8=〔19〕16〔2〕43=〔101011〕2=〔53〕8=〔2B〕16〔3〕56=〔111000〕2=〔70〕8=〔38〕16〔4〕〔1001110〕2、〔116〕8、〔4E〕16【题1-2】将以下二进制数转换为十进制数。

〔1〕10110001;〔2〕10101010;〔3〕11110001;〔4〕10001000解:〔1〕10110001=177〔2〕10101010=170〔3〕11110001=241〔4〕10001000=136【题1-3】将以下十六进制数转换为十进制数。

〔1〕FF;〔2〕3FF;〔3〕AB;〔4〕13FF解:〔1〕〔FF〕16=255〔2〕〔3FF〕16=1023〔3〕〔AB〕16=171〔4〕〔13FF〕16=5119【题1-4】将以下十六进制数转换为二进制数。

〔1〕11;〔2〕9C;〔3〕B1;〔4〕AF解:〔1〕〔11〕16=〔00010001〕2〔2〕〔9C〕16=〔10011100〕2〔3〕〔B1〕16=〔1011 0001〕2〔4〕〔AF〕16=〔10101111〕2【题1-5】将以下二进制数转换为十进制数。

〔1〕1110.01;〔2〕1010.11;〔3〕1100.101;〔4〕1001.0101解:〔1〕〔1110.01〕2=14.25〔2〕〔1010.11〕2=10.75〔3〕〔1001.0101〕2=9.3125【题1-6】将以下十进制数转换为二进制数。

〔1〕20.7;〔2〕10.2;〔3〕5.8;〔4〕101.71解:〔1〕20.7=〔10100.1011〕2〔2〕10.2=〔1010.0011〕2〔3〕5.8=〔101.1100〕2〔4〕101.71=〔1100101.1011〕2【题1-7】写出以下二进制数的反码与补码〔最高位为符号位〕。

思考题与习题2-1 输入信号的波形如图T2-1(a)所示,试画出图(b)中Y 1-Y 6的波形图(不考虑门电路的传 输延迟时间)。

DA Y DB Y B Y CDAB Y ABCY AY ⊕=+===+===6543211图T2-1 2-2 指出图T2-2中各门电路的输出是什么状态(高电平、低电平或高阻状态)。

已知这些门电路均为74系列TTL 门电路。

图T2-2011110010101011010111874321=⋅+⋅==⊕==+==⋅==+==⋅⋅=Y Y Y Y Y Y Y 5为高阻,Y 6为高阻。

2-3试说明在下列情况下,用内阻为20k Ω/V 的三用表的5V 量程去测量如图T2-3所示的74 系列与非门U I2端的电压应为多少: (1)U I1悬空;U I2=1.4 V (2)U I1接0V ;U I2=0 V (3)U I1接3V ;U I2=1.4 V (4)U I1接5.1Ω电阻到地;U I2=0 V(5) U I1接10k Ω电阻到地。

U I2=1.4 V图T2-3图T2-32-4试说明下列各种门电路中,哪些可以将输出端并联使用(输入端的状态不一定相同 )。

(1) 具有推拉式输出级的电路;×(2) TTL 的OC 门;√线与(3) TTL 的三态门;√总线应用(4) 普通的CMOS 门;×(5) CMOS 三态门。

√2-5 CMOS 门电路不宜将输入端悬空使用,请说明原因。

CMOS 门电路输入阻抗高,很容易受到干扰,并且CMOS 电路为场效应管,是电压控制电流器件,悬空时容易出现静电等瞬时高压烧毁器件的现象,因此输入端不宜悬空,必须根据 实际情况做相应的处理。

2-6 请对应于输入波形画出图T2-6所示电路在下列两种情况下的输出波形:(1)忽略所有门的传输延迟时间;(2)考虑每个门都有传输延迟时间t pd 。

图T2-62-7 电路如图T2-7所示,试分别列出电路的功能真值表以及输出端F 1和F 2的逻辑表达式, 并说明电路实现的逻辑功能。