数字电路教案阎石第三章逻辑门电路

- 格式:doc

- 大小:675.00 KB

- 文档页数:12

武夷学院

教案

课程名称:数字电路与逻辑设计基础

课程类型:□理论课□实践课□√理论、实践课

学时: 54(理论学时36)学分: 3

授课教师:范有机

授课班级: 09计科(1)、(2)、(3)班

授课学期:2009至2010学年第 2 学期

教材名称:数字电路与逻辑设计基础(第五版阎石

主编)

参考资料:1.康华光《电子技术基础》(数字部分第五版)2.邓元庆《数字电路与逻辑设计》

2010年8 月15 日

数字电路与逻辑设计课程教案

数字电路与逻辑设计课程教案

数字电路与逻辑设计课程教案

数字电路与逻辑设计课程教案

数字电路与逻辑设计课程教案

数字电路与逻辑设计课程教案

数字电路与逻辑设计课程教案。

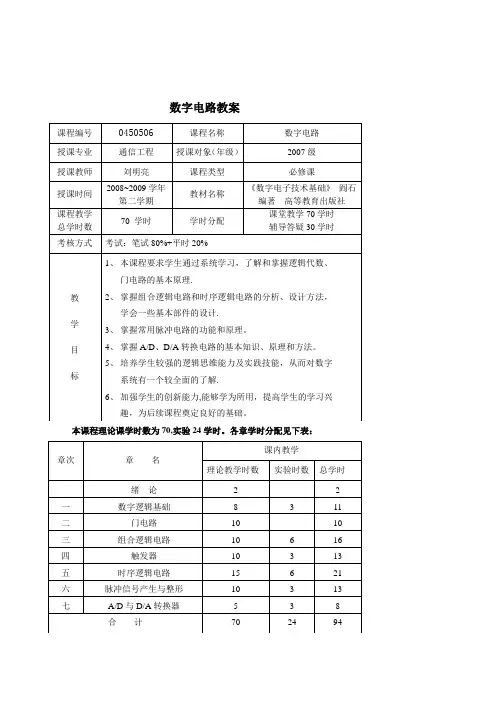

数字电路教案本课程理论课学时数为70,实验24学时。

各章学时分配见下表:第一章逻辑代数基础【本周学时分配】本周5学时。

周二1~2节,周四3~5节。

【教学目的与基本要求】1、掌握二进制数、二-十进制数(主要是8421 BCD码)2、熟练掌握逻辑代数的若干基本公式和常用公式。

3、熟练掌握逻辑函数的几种表达形式.【教学重点与教学难点】本周教学重点:1、绪论:重点讲述数字电路的基本特点、应用状况和课程主要内容。

2、逻辑代数的基本运算:重点讲述各种运算的运算规则、符号和表达式.3、逻辑代数的基本公式和常用公式:重点讲述逻辑代数的基本公式与普通代数公式的区别,常用公式的应用背景.4、逻辑函数的表示方法:重点讲述各种表示方法的特点和相互转换方法。

本周教学难点:反演定理和对偶定理:注意两者之间的区别、应用背景和变换时应注意的问题。

【教学内容与时间安排】一、绪论(约0.5学时)1、电子电路的分类。

2、数字电路的基本特点.3、数字电路的基本应用。

4、本课程的主要内容;5、本课程的学习方法和对学生的基本要求。

二、数制与码制(约1.5学时)(若前置课程已学,可作简单复习0。

5学时)1、几种不同进制(二、八、十、十六进制)。

2、几种不同进制相互转换。

3、码制(BCD码)。

三、逻辑代数1、基本逻辑运算和复合逻辑运算:与、或、非运算是逻辑代数的基本运算;还可以形成其他复合运算,常用的是与非、或非、与或非、异或、同或运算。

(约0。

5学时)2、常用公式(18个)(约0。

5学时)3、基本定理(代入定理、反演定理、对偶定理)(约0。

5学时)4、逻辑函数的概念及表示方法(约0。

5学时)5、逻辑函数各种表示方法间的转换:常用的转换包括:函数式←→真值表;函数式←→逻辑图(约1学时)【教学方法与教学手段】采用课堂讲授的方法,可组织学生讨论逻辑代数公式和普通代数公式的相同和不同之处,讨论逻辑函数各种表示方法的特点和相互转换方法。

【作业】P38 1。

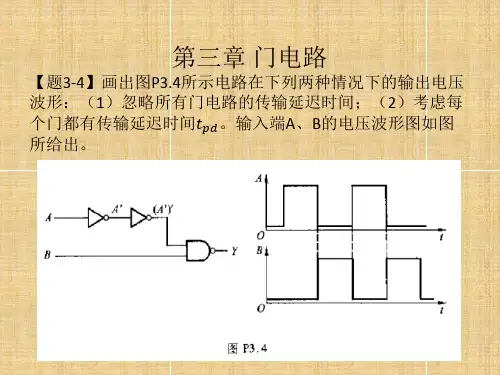

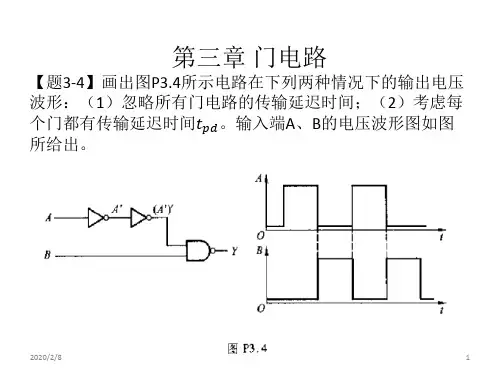

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路。

用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态。

在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL 电路)。

另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

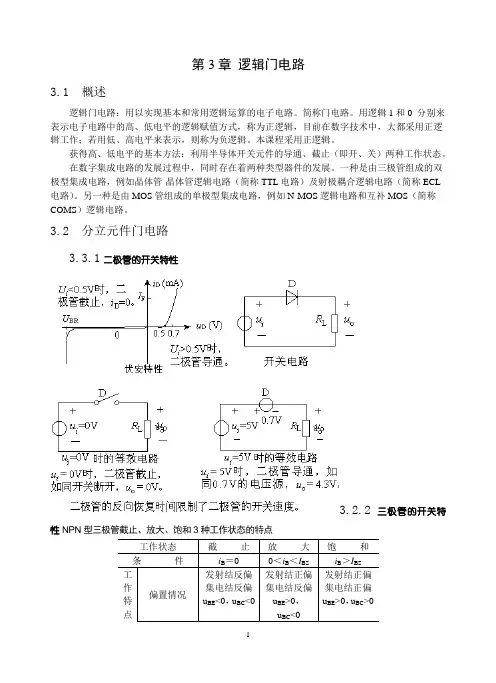

3.2 分立元件门电路3.3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点3.2.3二极管门电路1、二极管与门2、二极管或门3.2.4三极管非门3.2.5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

特点:开启电压低,其正向导通电压只有0.4V,比普通硅二极管0.7V的正向导通压降小得多;没有电荷存储效应;制造工艺和TTL电路的常规工艺相容,甚至无须增加工艺就可制造出SBD。

(2)采用有源泄放电路上图中的V6、R3、R6组成。

2、TTL与非门的工作原理(1)V1的等效电路V1是多发射极三极管,其有三个发射结为PN结。

故输入级用以实现A、B、C与的关系。

其等效电路如右图所示。

(2)工作原理分析①输入信号不全为1:如u A=0.3V,u B= u C =3.6V则u B1=0.3+0.7=1V,T2、T5截止,T3、T4导通忽略i B3,输出端的电位为:u Y≈5―0.7―0.7=3.6V输出Y为高电平。

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路。

用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态。

在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL 电路)。

另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3.2 分立元件门电路3.3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点3.2.3二极管门电路1、二极管与门2、二极管或门3.2.4三极管非门3.2.5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

特点:开启电压低,其正向导通电压只有0.4V,比普通硅二极管0.7V的正向导通压降小得多;没有电荷存储效应;制造工艺和TTL电路的常规工艺相容,甚至无须增加工艺就可制造出SBD。

(2)采用有源泄放电路上图中的V6、R3、R6组成。

2、TTL与非门的工作原理(1)V1的等效电路V1是多发射极三极管,其有三个发射结为PN结。

故输入级用以实现A、B、C与的关系。

其等效电路如右图所示。

(2)工作原理分析①输入信号不全为1:如u A=0.3V,u B= u C =3.6V则u B1=0.3+0.7=1V,T2、T5截止,T3、T4导通忽略i B3,输出端的电位为:u Y≈5―0.7―0.7=3.6V输出Y为高电平。

②输入信号全为1:如u A=u B=u C 3.6V则u B1=2.1V,T2、T5导通,T3、T4截止输出端的电位为:u Y=U CES=0.3V输出Y为低电平。

功能表逻辑表达式:集成与非门电路引脚排列图(顶视):(74LS00内含4个2输入与非门,74LS20内含2个4输入与非门)3、电压传输特性和噪声容限(1)电压传输特性定义:门电路输出电压u o随输入电压变化的特性曲线称为电压传输特性。

(电压传输特性曲线见课本图3.3.3.)(2)概念输入电平范围:高电平U iHmin~U iHmax=1.2~5V;低电平U iLmin~U iLmax=0.2~1.0V·关门电平。

上述输入低电平中的最大值,即U OFF = U iLmax =1.0V。

只有当输入u I <U OFF 时,与非门才关闭,输出高电平。

·开门电平。

上述输入高电平中的最小值,即U ON =U iHmin=1.2V只有当输入u I >U ON 时,与非门才开通,输出低电平。

·阈值电压。

工作在电压传输特性曲线转折区中点对应的输入电压称为阈值电压,又称为门槛电压。

用U TH表示。

近似分析时,可以认为:当u I <U TH时,与非门工作在关闭状态,输出高电平U OH;当u I >U TH时,与非门工作在开通状态,输出低电平U OL。

(3)噪声容限在输入信号上叠加的噪声电压只要不超过允许值,就不会影响电路的正常逻辑功能,这个允许值称为噪声容限。

电路的噪声容限越大,其抗干扰能力就越强。

4、输入负载特性定义:输入电压u I随输入端对地外接电阻R I变化的曲线,称为输入负载特性。

(1)在V2和V5导通前,u I随R I的增大而上升,输入电压u I在R I上升到V2和V5开始导通时,u I不能用上式进行计算。

当u I上升到1.1V 时,V1的基极电压被钳在1.8V上,V2和V5导通,输出u o为低电增U OL,此后,u I不再随R I的增大而升高。

u I随R I 变化的曲线如上面右图所示。

·维持输出高电平的R I最大值称为关门电阻,用R OFF表示,其值约为700Ω。

·维持输出低电平的R I最小值称为开门电阻,用R ON表示,其值约为2。

1KΩ。

5、输出负载特性输出电压u o随负载电流I O变化的特性曲线称为输出负载特性。

6、传输延迟时间由于二极管、三极管由导通变为截止或由截止变为导通时,都需要一定的时间,再加上其它原因,输出电压u o的脉冲波形不仅比输入波形延迟了一定的时间,而且波形的上升沿和下降沿也都变坏了。

3.3.2低功耗肖特基系列3.3.3其它功能的TTL门电路TTL集成逻辑门电路除与非门外,常用的还有集电极开路与非门、或非门、与或非门、三态门和异或门等。

它们都是在上面所述的非门的基础上发展出来的。

1、集电极开路与非门(OC门)·电路结构与逻辑符号·作用与功能问题的提出:为解决一般TTL与非门不能线与而设计的。

(作用)功能:接入外接电阻R后:①A、B不全为1时,u B1=1V,T2、T3截止,Y=1。

②A、B全为1时,u B1=2.1V,T2、T3饱和导通,Y=0。

外接电阻R的取值范围为:·应用(a)实现线与(b)驱动显示器(c)实现电平转换2、与或非门3、三态输出门(TSL 门)·电路结构和逻辑符号·工作原理①当EN=0时,二极管D截止,TSL门的输出状态完全取决于输入信号A、B的状态,电路输出与输入的逻辑关系和一般与非门相同。

②当EN=1时,二极管D导通,一方面使u C2 =1V,V4截止;另一方面使u B1 =1V,从而使V2和V5截止。

输出端开路,电路处于高阻状态。

结论:电路的输出有高阻态、高电平和低电平3种状态。

·三态输出门的应用(a)构成单向总线(b)构成双向总线TTL数字集成电路及主要参数TTL系列集成电路①74:标准系列,前面介绍的TTL门电路都属于74系列,其典型电路与非门的平均传输时间t pd =10ns,平均功耗P=10mW。

②74H:高速系列,是在74系列基础上改进得到的,其典型电路与非门的平均传输时间t pd=6ns,平均功耗P=22mW。

③74S:肖特基系列,是在74H系列基础上改进得到的,其典型电路与非门的平均传输时间t pd=3ns,平均功耗P=19mW。

TTL与非门主要参数(1)输出高电平U OH:TTL与非门的一个或几个输入为低电平时的输出电平。

产品规范值U OH≥2.4V,标准高电平U SH=2.4V。

(2)高电平输出电流I OH:输出为高电平时,提供给外接负载的最大输出电流,超过此值会使输出高电平下降。

I OH表示电路的拉电流负载能力。

(3)输出低电平U OL:TTL与非门的输入全为高电平时的输出电平。

产品规范值U OL≤0.4V,标准低电平U SL=0.4V。

(4)低电平输出电流I OL:输出为低电平时,外接负载的最大输出电流,超过此值会使输出低电平上升。

I OL表示电路的灌电流负载能力。

(5)扇出系数N O:指一个门电路能带同类门的最大数目,它表示门电路的带负载能力。

一般TTL门电路N O≥8,功率驱动门的N O可达25。

(6)最大工作频率f max:超过此频率电路就不能正常工作。

(7)输入开门电平U ON:是在额定负载下使与非门的输出电平达到标准低电平U SL的输入电平。

它表示使与非门开通的最小输入电平。

一般TTL门电路的U ON≈1.8V。

(8)输入关门电平U OFF:使与非门的输出电平达到标准高电平U SH的输入电平。

它表示使与非门关断所需的最大输入电平。

一般TTL门电路的U OFF≈0.8V。

(9)高电平输入电流I IH:输入为高电平时的输入电流,也即当前级输出为高电平时,本级输入电路造成的前级拉电流。

(10)低电平输入电流I IL:输入为低电平时的输出电流,也即当前级输出为低电平时,本级输入电路造成的前级灌电流。

(11)平均传输时间t pd:信号通过与非门时所需的平均延迟时间。

在工作频率较高的数字电路中,信号经过多级传输后造成的时间延迟,会影响电路的逻辑功能。

(12)空载功耗:与非门空载时电源总电流I CC与电源电压V CC的乘积。

三、TTL集成电路逻辑门电路的使用注意事项(1)关于电源等:对于各种集成电路,使用时一定要在推荐的工作条件范围内,否则将导致性能下降或损坏器件。

(2)关于输入端:数字集成电路中多余的输入端在不改变逻辑关系的前提下可以并联起来使用,也可根据逻辑关系的要求接地或接高电平。

TTL电路多余的输入端悬空表示输入为高电平(3)关于输出端:具有推拉输出结构的TTL门电路的输出端不允许直接并联使用。

输出端不允许直接接电源V CC或直接接地。

3.4 CMOS集成逻辑门电路一、CMOS反相器1、MOS管的符号增强型NMOS管和增强型PMOS管的符号如右图所示:2、CMOS反相器(1)u A=0V时,T N截止,T P导通。

输出电压u Y=V DD=10V。

(2)u A=10V时,T N导通,T P截止。

输出电压u Y=0V。

二、其它功能的CMOS电路CMOS与非门和或非门CMOS与非门①A、B当中有一个或全为低电平时,T N1、T N2中有一个或全部截止,T P1、T P2中有一个或全部导通,输出Y为高电平。

②只有当输入A、B全为高电平时,T N1和T N2才会都导通,T P1和T P2才会都截止,输出Y才会为低电平。

CMOS或非门①只要输入A、B当中有一个或全为高电平,T P1、T P2中有一个或全部截止,T N1、T N2中有一个或全部导通,输出Y为低电平。

②只有当A、B全为低电平时,T P1和T P2才会都导通,T N1和T N2才会都截止,输出Y才会为高电平。

2、漏极开路的CMOS门(OD门)和TTL电路中的OC门一样,CMOS门电路中也有漏极开路的门电路,即OD门。

下图所示为二输入漏极开路的与非缓冲/驱动器,也具有与非功能,,其逻辑符号亦在下图标示出,与OC门符号相同。

3、CMOS传输门·电路结构与逻辑符号·工作原理①C=0时,即C端为低电平(0V)、端为高电平(+V DD)时,T N和T P都不具备开启条件而截止,输入和输出之间相当于开关断开一样。

②C=1时,即C端为高电平(+V DD)、端为低电平(0V)时,T N和T P都具备了导通条件,输入和输出之间相当于开关接通一样,u o=u i。

4、CMOS三态输出门电路及逻辑符号如图所示。

①,T P2、T N2均导通,T P1、T N1构成反相器。