数字下变频的FPGA实现

- 格式:doc

- 大小:522.50 KB

- 文档页数:4

• 189•两路供电一路是NORMAL POWER,一路是ESS POWER,线路图上也是两路供电但实际操作中按要求拔出跳开关后DEU 上还有电,带电拆装容易损坏DEU ,所以在进行拆装时还要整机断电(图1)。

AMM 23-73-00-22700-00-B 。

2)DEU 的联接端和终端:DEU 上的终端/联接端盒是根据DEU 在飞机上的安装位置决定的IPC23-73-09-08H 图而且两者件号是不同的(图2、图3)。

航后报告有故障信息CAM NOT LOADED 或OBRM/CIDS(101RH)-SDF1之类故障一般就要重新安装CAM 或OBRM 卡然后进行测试。

注意COM 卡和OBRM 及PRAM 卡在FAP上会显示件号,拔出后会显示图2图3NONE ,重新安装后要做一遍上电测试才会出现件号。

航后报告有信息SMOKE 一般情况下要更换DIRECTOR,因为烟雾探测是有CIDS 计算机SDF 部分的功能。

总结:CIDS 系统功能强大涉及到的部件及故障多种多样,引起的原因也各不相同,排故时要考虑到的东西很多,我们平时要本着从易到难,从简单到复杂的思路进行排故,尽量不要把问题搞大。

因为虽然CIDS 系统大都是客舱内的故障但有些还是影响飞行或者是根本就无法放行,所以对CIDS 系统还是要有一定的了解,对我们在航前,过站能快速准确的对相应的故障有一个正确处理措施保障航班的正常运行有很大的帮助。

引言:雷达发射信号的带宽直接决定雷达的距离分辨率,高分辨率目标识别雷达要求更高的信号带宽,以实现对目标型号的具体识别。

对于要求信号实时处理的雷达系统,高速的ADC 采样速率与低速的FPGA 流水处理速率,需要引入多相滤波理论,通过并行多相分解实现FPGA 低速处理高速的ADC 采样信号,并且通过合适的抽取速率以降低数字下变频后信号的处理速率。

1 数字下变频的多相分解传统的窄带信号数字下变频理论是将信号混频、低通滤波、抽取。

软件无线电中数字下变频技术研究及FPGA实现的开题报告一、研究背景及意义:软件无线电技术(Software Defined Radio,SDR)正在迅速发展,无线通信的下变频(Intermediate Frequency,IF)处理是其中的核心环节之一。

IF处理是指在接收机中通过将射频信号与本振信号进行混频,将高频信号转换为低频信号的信号处理过程。

数字下变频技术是IF处理的一种关键技术,它可以将下变频过程中涉及的许多电路、器件转化为数字信号处理的形式,大大降低系统成本,并便于实现复杂的算法。

FPGA(Field-Programmable Gate Array)作为数字电路设计的重要手段,因其灵活性、可重构性和实时性等优点,被广泛应用于SDR系统中。

本次研究旨在深入研究数字下变频技术,结合FPGA技术实现数字下变频电路,并优化设计算法,提高系统的性能指标,为SDR系统的设计和开发提供技术支持。

二、研究内容:1、数字下变频技术的原理及算法研究;2、基于FPGA的数字下变频电路设计;3、数字下变频电路性能指标测试;4、数字下变频电路算法优化研究。

三、研究方法:1、文献研究:搜集和分析数字下变频技术和FPGA技术的相关文献和资料,了解和掌握相关知识和技术;2、仿真模拟:通过软件仿真模拟,验证数字下变频电路的性能指标,优化算法设计;3、实验测试:通过硬件实验测试,验证数字下变频电路的性能指标,进一步完善算法设计。

四、预期成果:1、深入掌握数字下变频技术及FPGA技术;2、实现基于FPGA的数字下变频电路;3、测试数字下变频电路的性能指标,以及优化算法;4、撰写学术论文,发表相关研究论文。

五、研究进度安排:第一年:1、查阅数字下变频技术和FPGA技术的文献资料,熟悉研究领域;2、完成数字下变频电路设计的前期准备和仿真环境搭建;3、完成数字下变频电路的仿真验证。

第二年:1、基于FPGA实现数字下变频电路;2、进行硬件实验测试,并对测试数据进行分析;3、对数字下变频电路的算法进行优化。

数字下变频电路的FPGA实现随着数字化时代的到来,数字信号处理技术已经成为了许多领域中不可或缺的一部分。

其中,数字下变频技术是一种非常重要的数字信号处理技术,被广泛应用于雷达、通信、音频处理等领域。

本文将介绍数字下变频电路的FPGA实现。

数字下变频电路的基本原理数字下变频电路的基本原理是将输入信号进行混频,将高频信号转换为低频信号,并对低频信号进行采样和滤波,得到一个纯净的低频信号。

数字下变频电路通常由数字信号处理器、数字乘法器和数字低通滤波器等组成。

FPGA实现数字下变频电路的优势 FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,能够根据需要实现各种数字电路。

与传统的数字信号处理芯片相比,FPGA具有以下优势:高速并行处理能力:FPGA内部具有大量的可编程逻辑器件,可以实现高速并行处理,提高处理速度和效率。

灵活性:FPGA可以通过重新编程实现不同的数字电路,方便灵活,可以快速适应不同的应用场景。

可靠性:FPGA内部具有严格的质量保证措施,保证了数字电路的可靠性和稳定性。

设计数字下变频电路的算法:根据具体应用场景和要求,利用MATLAB 等软件设计数字下变频电路的算法。

将算法转换为硬件描述语言:将设计的数字下变频电路算法转换为硬件描述语言(如VHDL或Verilog),并利用EDA工具进行仿真和验证。

将硬件描述语言编译成二进制文件:将生成的硬件描述语言编译成二进制文件,以便在FPGA上实现。

将二进制文件下载到FPGA中:将生成的二进制文件下载到FPGA中,通过调试和测试,最终实现数字下变频电路。

结论数字下变频电路的FPGA实现具有高速并行处理能力、灵活性和可靠性等优势,已经被广泛应用于雷达、通信、音频处理等领域。

通过设计算法、转换为硬件描述语言、编译成二进制文件以及下载到FPGA中等步骤,可以实现数字下变频电路的高效、快速和可靠实现。

数字下变频电路是一种重要的信号处理单元,它在通信、雷达、电子对抗等领域有着广泛的应用。

数字下变频技术的研究及FPGA实现的开题报告一、选题背景随着数字技术的不断发展,数字下变频技术应用越来越广泛,尤其是在航空、舰船和工业控制等领域,数字下变频技术的应用已经成为一种趋势。

数字下变频技术是指使用数字信号处理器或FPGA等数字电路,将输入的交流电信号转化为直流电信号,并通过PWM技术输出不同频率的电流信号,实现变频器的功率调节功能。

针对数字下变频技术在工业应用中存在的一些问题,本研究计划借助FPGA技术,设计实现一种高效、可靠的数字下变频技术方案。

二、选题意义目前,传统的变频器主要采用模拟电路实现,系统效率低、系统复杂度高、功耗大、电磁干扰等问题十分突出。

数字下变频技术则能够很好地解决这些问题,同时还具有高速、高精度、高可靠性、低成本等优势。

通过本研究设计的数字下变频技术方案,可以有效地提高变频器的性能表现,减少设备成本,进一步推动数字化技术在工业应用领域的发展。

三、研究方法本研究计划采用FPGA技术实现数字下变频技术方案。

具体研究方法如下:1. 数字信号处理模块的设计。

将输入的交流电信号转化为直流电信号,并进行数字信号处理,获得适合输出的数字信号。

2. PWM模块的设计。

通过PWM技术控制输出电流的频率和占空比,实现电机的功率调节功能。

3. 硬件平台的搭建。

将设计好的数字信号处理模块和PWM模块集成到FPGA芯片中,搭建出数字下变频器的硬件平台。

4. 软件程序的编写。

编写实现数字下变频技术的软件程序,在FPGA 芯片中运行,控制数字下变频器工作。

四、预期成果本研究预期实现一种高效、可靠的数字下变频技术方案,并通过FPGA实现硬件平台及相应的软件程序。

该方案的预期成果包括:1. 实现输入电压转化为输出电流的功能,并可根据需要进行功率调节。

2. 实现高速、高精度的数字信号处理功能,提高系统效率及稳定性。

3. 实现较低的功耗、EMI及设备成本。

五、可行性分析本研究采用FPGA技术实现数字下变频技术方案具有较高的可行性和实际应用价值。

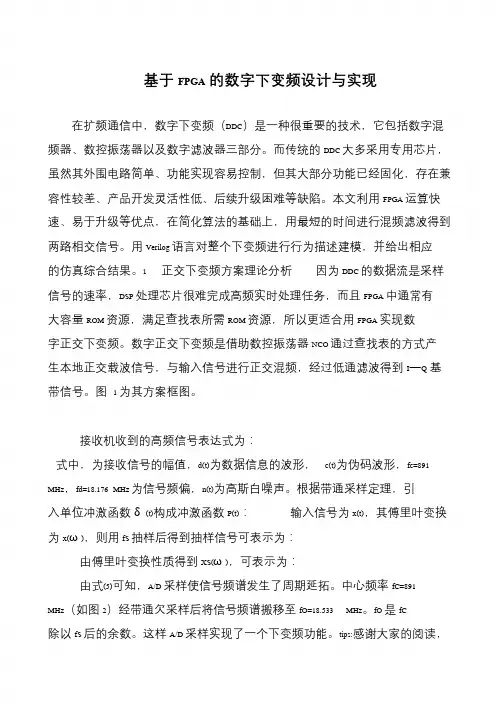

基于FPGA的数字下变频设计与实现在扩频通信中,数字下变频(DDC)是一种很重要的技术,它包括数字混频器、数控振荡器以及数字滤波器三部分。

而传统的DDC 大多采用专用芯片,虽然其外围电路简单、功能实现容易控制,但其大部分功能已经固化,存在兼容性较差、产品开发灵活性低、后续升级困难等缺陷。

本文利用FPGA 运算快速、易于升级等优点,在简化算法的基础上,用最短的时间进行混频滤波得到两路相交信号。

用Verilog 语言对整个下变频进行行为描述建模,并给出相应的仿真综合结果。

1 正交下变频方案理论分析因为DDC 的数据流是采样信号的速率,DSP 处理芯片很难完成高频实时处理任务,而且FPGA 中通常有大容量ROM 资源,满足查找表所需ROM 资源,所以更适合用FPGA 实现数字正交下变频。

数字正交下变频是借助数控振荡器NCO 通过查找表的方式产生本地正交载波信号,与输入信号进行正交混频,经过低通滤波得到I―Q基带信号。

图1 为其方案框图。

接收机收到的高频信号表达式为:式中,为接收信号的幅值,d(t)为数据信息的波形,c(t)为伪码波形,fc=891 MHz,fd=18.176 MHz 为信号频偏,n(t)为高斯白噪声。

根据带通采样定理,引入单位冲激函数δ(t)构成冲激函数P(t):输入信号为x(t),其傅里叶变换为x(ω),则用fS 抽样后得到抽样信号可表示为:由傅里叶变换性质得到XS(ω),可表示为:由式(5)可知,A/D 采样使信号频谱发生了周期延拓。

中心频率fC=891 MHz(如图2)经带通欠采样后将信号频谱搬移至fO=18.533 MHz。

fO 是fC 除以fS 后的余数。

这样A/D 采样实现了一个下变频功能。

tips:感谢大家的阅读,。

数字下变频的FPGA实现作者:郑传家屈德新邱晓军周铁解放军理工大学通信工程学院来源: 电子产品世界摘要:本文介绍了数字下变频的组成结构,并通过一个具体的实例,给出了FPGA实现的具体过程。

关键词:FPGA;数字下变频;VHDL引言数字化中频(DIF)频谱分析仪在高中频实现数字化处理,具有分析带宽大、RBW小、测量时长短,可对复杂信号实施时—频分析的功能,因而得到越来越广泛的应用。

但由于现有的数字信号处理器(DSP)处理速度有限,往往难以对高速率A/D采样得到的数字信号直接进行实时处理。

为了解决这一矛盾,需要采用数字下变频(DDC)技术,将采样得到的高速率信号变成低速率基带信号,以便进一步的分析处理。

用现场可编程阵列(FPGA)来设计数字下变频器有许多好处:FPGA在硬件上具有很强的稳定性和极高的运算速度,在软件上具有可编程的特点,可以根据不同的系统要求,采用不同的结构来完成相应的功能,具有很强的灵活性,便于进行系统功能扩展和性能升级。

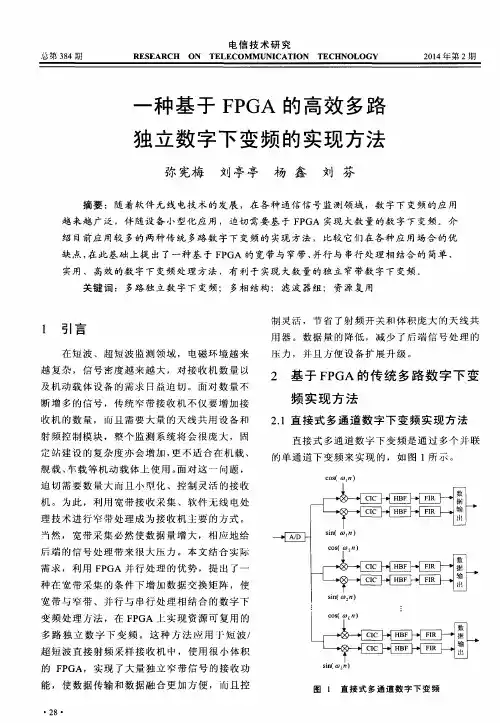

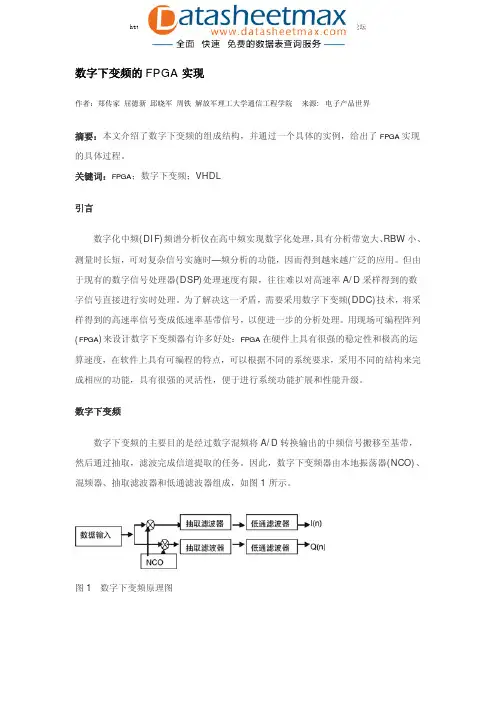

数字下变频数字下变频的主要目的是经过数字混频将A/D转换输出的中频信号搬移至基带,然后通过抽取,滤波完成信道提取的任务。

因此,数字下变频器由本地振荡器(NCO)、混频器、抽取滤波器和低通滤波器组成,如图1所示。

图1 数字下变频原理图A/D变换后的信号分成两个信号,一个信号乘以正弦序列(同相分量),下变频至零中心频率上,通过抽取滤波器、整形低通FIR滤波形成与原信号相位相同的信号;另一路信号乘以经过90度相移的正弦序列(正交分量),同样是下变频至零中心频率上,再通过相同的抽取滤波器、整形低通FIR滤波器,形成与原信号正交的信号。

这样,DDC 输出的低速率、零中频的正交的两路信号送往DSP等数字信号处理器进行后续的数字处理。

DDC的FPGA以某中频数字化接收机为例来说明如何实现基于FPGA的数字下变频器。

输入信号为中频26MHz,带宽500KHz的调频信号,该信号经过A/D变换之后送到DDC(A/D 采样精度为8位,采样率20MHz),要求DDC将其变换为数字正交基带信号,并实现10倍抽取,即输出给基带处理器的数据速率为2MSPS,最后再经过16阶FIR滤波器进行信号整形。

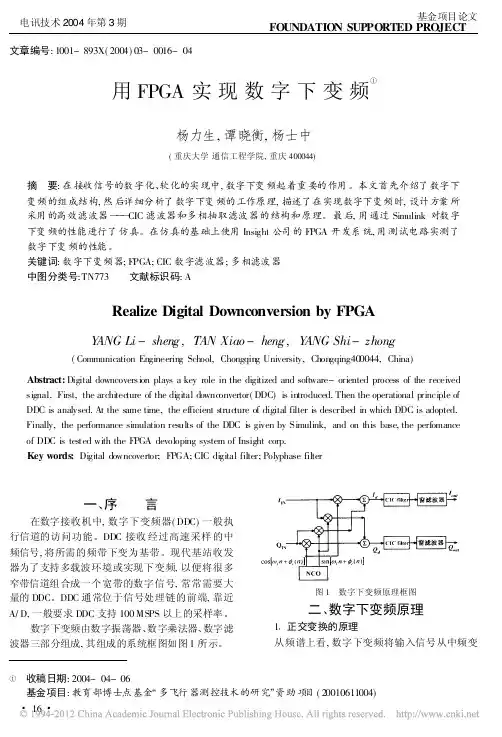

文章编号:1001-893X(2004)03-0016-04用FPGA 实现数字下变频杨力生,谭晓衡,杨士中(重庆大学通信工程学院,重庆400044)摘 要:在接收信号的数字化、软化的实现中,数字下变频起着重要的作用。

本文首先介绍了数字下变频的组成结构,然后详细分析了数字下变频的工作原理,描述了在实现数字下变频时,设计方案所采用的高效滤波器 CIC 滤波器和多相抽取滤波器的结构和原理。

最后,用通过Simulink 对数字下变频的性能进行了仿真。

在仿真的基础上使用Insight 公司的FPGA 开发系统,用测试电路实测了数字下变频的性能。

关键词:数字下变频器;FPGA;CIC 数字滤波器;多相滤波器中图分类号:TN773 文献标识码:ARealize Digital Downconversion by FPGAY ANG Li -shen g ,TAN Xiao -heng ,Y ANG Shi -zhong(Communication Engineering School,Chongqing University,Chongqing400044,China)Abstract:Digital downcoversion plays a key role in the digitized and software-oriented process of the received signal.First,the architec ture of the digital downc onvertor(DDC)is introduced.Then the operational principle of DDC is analysed.At the same time,the efficient struc ture of digital filter is described in which DDC is adopted.Finally,the performance simulation results of the DDC is given by Simulink,and on this base,the perfomance of DDC is tested with the FPGA devoloping system of Insight corp.Key words:Digital downcovertor;FPGA;CIC digital filter;Polyphase filter一、序 言在数字接收机中,数字下变频器(DDC)一般执行信道的访问功能。

基于FPGA的DDC(数字下变频)设计与实现微系统设计、测试与控制课程大作业之基于FPGA的DDC(数字下变频)的设计与仿真摘要 (1)ABSTRACT (2)第一章绪论 (3)1.1 数字下变频(DDC)研究背景 (3)1.2 DDC概述 (4)1.3 本文研究内容和结构安排 (5)第二章数字下变频(DDC)基础理论 (7)2.1 数字下变频器 (7)2.1.1 数字变频的基本原理与结构 (7)2.1.2影响数字变频器性能的主要因素72.2 数字信号采样理论 (8)2.2.1低通信号采样理论 (8)2.2.2 带通信号采样理论 (9)2.3 数字正交检波 (10)2.3.1 低通滤波法 (10)2.3.2 多相滤波结构变换法 (11)2.4 多抽样率数字信号处理理论 (13)2.4.1 整数倍抽取和内插 (13)2.4.2 多抽样率系统的恒等变换 (16)2.4.3 多相滤波结构 (17)2.5 相关算法介绍 (19)2.5.1 CORDIC算法 (19)2.5.2 FIR滤波器 (21)2.6 本章小结 (22)第三章数字下变频(DDC)各模块设计 (23)3.1 数字下变频的基本实现方案 (23)3.2 基于DDS的数控振荡器的设计 (23)3.2.1 混频器模块设计 (23)3.2.2 DDS的特点 (25)3.3抽取滤波 (27)3.4 本章小结 (29)第四章数字下变频器设计验证和逻辑综合 (30)4.1基于DDS的数控振荡器的仿真和验证304.2 FIR滤波器的仿真和验证 (32)4.3 抽取模块仿真验证 (33)4.4 DDC整体的仿真和验证 (33)4.4.1 MATLAB与modelsim仿真 (34)4.4.2 FPGA综合报告 (35)4.5 本章小结 (36)第五章总结与展望 (37)参考文献 (39)摘要数字下变频(Digital Down Convert—DDC)是将中频信号下变频至零频,且使信号速率降至适宜通用DSP器件处理速率的技术。

1 引言数字下变频DDC(digital down lonvwrsionl作为系统前端A/D转换器与后端通用DSP器件间的桥梁,通过降低数据流的速率,将低速数据送给后端通用DSP器件处理,其性能的优劣将对整个软件无线电系统的稳定性产生直接影响。

采用专用DDC器件完成数字下变频,虽具有抽取比大、性能稳定等优点,但价格昂贵,灵活性不强,不能充分体现软件无线电的优势。

FPGA工艺发展迅速,处理能力大大增强,相对于ASIC,DSP,其具有吞吐量高、开发周期短、可实现在线重构诸多优势。

基于这些优点,FPGA在软件无线电的研发中具有重要作用。

2 数字下变频系统数字下变频器在软件无线电系统中完成的功能结构如图1所示,其中包括直接数字频率合成器DDS(direct digital synthesizer)、数字混频器、FIR滤波器、抽取等模块。

原始模拟中频信号经A/D转换器带通采样后得到数字中频信号,输入DDC后先与DDS产生的两路正交本振信号相乘(数字混频),将数字中频搬移到基带。

混频后得到的数据率和采样率一致,后级FIR滤波器要达到该处理速率。

硬件实现相当困难,因此首先通过抽取模块大大降低数据速率,然后使用高阶FIR低通滤波器对整个信道整形滤波。

滤波输出的两路正基带信号交由下一级DSP器件进行处理。

2.1 混频器的FPGA实现数字混频器将原始采样信号与查找表生成的正、余弦波形分别相乘,最终得到两路互为正交的信号。

由于输入信号的采样率较高,因此要求混频器的处理速度大于等于信号采样率。

单通道的数字下变频系统需要两个数字混频器.也就是乘法器。

XC2V1000器件内嵌64个18×18位硬件乘法器,其最高工作频率为500 MHz,因此采用硬件乘法器完全能够满足混频器的设计要求。

使用Xilinx公司的Multiplier IP核可以轻松实现硬件乘法器的配置。

该设计中采用两路14位的输入信号,输出信号也为14位。

基于FPGA的数字下变频研究实现的开题报告一、研究背景数字下变频技术是电力电子学科中的重要研究方向,其核心思想是通过数字信号处理技术将交流电能转换为可控的直流电能,进而通过逆变器将其转换为交流电源,用于驱动各种负载。

数字下变频技术被广泛应用于工业控制、交通运输、农业生产、医疗卫生等领域,已成为电力电子学科中不可或缺的重要部分。

FPGA(Field Programmable Gate Array)是一种基于现场可编程门阵列结构的可编程逻辑设备,具有可编程性高、灵活性强、速度快等优点,广泛应用于数字信号处理、计算机视觉、通信网络、高级控制等领域,并成为数字下变频研究中的重要工具。

因此,基于 FPGA 的数字下变频技术的研究具有重要意义,对于提高数字下变频技术的效率、可靠性和应用范围具有重要意义。

二、研究内容和方法本文研究基于 FPGA 的数字下变频技术,主要包括以下内容:1. 数字下变频技术的原理和发展现状。

介绍数字下变频技术的基本原理和逆变器的工作原理,总结数字下变频技术的发展现状和研究动态。

2. 基于 FPGA 的数字下变频技术的设计和实现。

通过对数字下变频技术进行分析和研究,设计和实现基于 FPGA 的数字下变频的系统结构,并实现数字信号的采集、处理、控制等功能,从而实现优化系统的效率和控制质量。

3. 数字下变频技术的实验验证。

通过搭建数字下变频技术实验平台,验证基于 FPGA 的数字下变频技术的可行性和优越性,分析其在实际应用中的多重优势和局限性。

研究方法涉及理论分析与建模、软硬件开发、系统实现与测试。

三、研究预期结果1. 实现基于 FPGA 的数字下变频系统,并验证其可行性和优越性。

2. 提高数字下变频技术的效率和控制质量,优化系统架构和设计方案。

3. 推动数字下变频技术的应用和发展,为工业控制、交通运输、农业生产、医疗卫生等领域的应用提供关键技术支持。

四、研究意义本研究的成果将具有重要的实际应用价值和理论意义。

1 引言

数字下变频DDC(digital down lonvwrsionl作为系统前端A/D转换器与后端通用DSP器件间的桥梁,通过降低数据流的速率,将低速数据送给后端通用DSP器件处理,其性能的优劣将对整个软件无线电系统的稳定性产生直接影响。

采用专用DDC器件完成数字下变频,虽具有抽取比大、性能稳定等优点,但价格昂贵,灵活性不强,不能充分体现软件无线电的优势。

FPGA工艺发展迅速,处理能力大大增强,相对于ASIC,DSP,其具有吞吐量高、开发周期短、可实现在线重构诸多优势。

基于这些优点,FPGA在软件无线电的研发中具有重要作用。

2 数字下变频系统

数字下变频器在软件无线电系统中完成的功能结构如图1所示,其中包括直接数字频率合成器DDS(direct digital synthesizer)、数字混频器、FIR滤波器、抽取等模块。

原始模拟中频信号经A/D转换器带通采样后得到数字中频信号,输入DDC后先与DDS产生的两路正交本振信号相乘(数字混频),将数字中频搬移到基带。

混频后得到的数据率和采样率一致,后级FIR滤波器要达到该处理速率。

硬件实现相当困难,因此首先通过抽取模块大大降低数据速率,然后使用高阶FIR低通滤波器对整个信道整形滤波。

滤波输出的两路正基带信号交由下一级DSP器件进行处理。

2.1 混频器的FPGA实现

数字混频器将原始采样信号与查找表生成的正、余弦波形分别相乘,最终得到两路互为正交的信号。

由于输入信号的采样率较高,因此要求混频器的处理速度大于等于信号采样率。

单通道的数字下变频系统需要两个数字混频器.也就是乘法器。

XC2V1000器件内嵌64个18×18位硬件乘法器,其最高工作频率为500 MHz,因此采用硬件乘法器完全能够满足混频器的设计要求。

使用Xilinx公司的Multiplier IP核可以轻松实现硬件乘法器的配置。

该设计中采用两路14位的输入信号,输出信号也为14位。

图2为混频器的结构图。

2.2 DDS的FPGA实现

采用ISE中的IPCORE实现DDS,由于原始信号为60±7 MHz带通信号,经过100 MHz MD 转换器产生一个中频为40 MHz的信号,将DDS输出频率设为40 MHz,产生频率为40 MHz 两路正交I/Q信号,并与原始信号混频后产生两路零中频正交信号,实现下变频。

其中DDS 参数设置动态范围(SFDR)为80 dB;频率分辨率(Frequency Resolution)为0.4Hz;DDS输

出频率(Frequency)为40 MHz。

DDS的仿真结果如图3所示。

2.3 抽取模块的FPGA实现

经混频后,到达抽取模块的是两路速率为100 MHz,位宽为14位的正交信号,为了更方便处理这两路正交信号,需降低信号速率。

该设计中,按照4:1的比例抽取信号,抽取完成后,变为速率为25 MHz,位宽为14位的信号。

抽取模块的实现是在ISE中采用VHDL语言编写。

首先对时钟4分频,将系统时钟100 MHz经分频变成25 MHz.再利用该25 MHz时钟控制两个D触发器.将经混频后速率为100 MHz,位宽为14位的两路I,Q正交信号分别作为这两个D触发器的输入信号,即可完成4:l抽取。

经抽取模块后,信号变为速率为25 MHz,位宽为14位的信号。

图4为分

频的仿真波形。

2.4 FIR滤波器的FPGA实现

FIR滤波器也是由ISEIPCORE实现,因为经DDS后的信号是带宽为14 MHz的零中频信号,只考虑正频率范围,故PFIR的通带截止频率为7 MHz,在MATLAB中设计一个通带截止频率为7 MHz的FIR,将系数量化为14位二进制数值存入系数文件*.coe,将其导入FIR即可;FIR的阶数(系数长度)越高,性

能越好,但考虑资源占用情况,FIR的阶数不宜过高,该设计采用35阶FIR。

故FIR参数设置为:结果

分辨率(Result Resolution)为16位;滤波器阶数(Fiher Length)为35;系数精度(Precision)为14位。

图5为FIR滤波器的结构。

2.5 FPGA器件选型

设计将对采样率为100 MHz的高速带通信号进行数字下变频处理,对系统的处理速度要求较高。

由于Xilinx公司的FPGA处理速度较Ahera公司的更快,并且在系统稳定性和可操作性方面均优于Altera。

考虑到数字下变频对系统的处理速度、可靠性、稳定性均有较高的要求.因此选用Xilinx公司的Virtex一2系列的XC2V1000器件。

XCl2V1000器件内部包含1 280个CLB,每个CLB由4个Slice构成,共5 120个Slice,满足设计需求。

3 系统调试与结果分析

Xilinx的FPGA的开发工具为ISE,目前版本已更新到lO.2。

ISE是一个集成的开发环境,包括HDL 编辑器、IP—CORE Cenerator System、约束编辑器、静态时序分析工具、功耗分析工具等十多种工具。

这些工具可以帮助设计人员提高工作效率。

ISE可以方便集成第三方工具,如仿真工具Mod一elsim、综合工具Synplify。

此外Xmnx的工具Clfipseope可以在线观察FPGA内部信号波形,Plan Ahead工具可以通过简化综合与布局布线间的步骤,大大减少设计时间,与ISE结合使用时可以实现30%的性能提升。

在ISE环境下采用VHDL语言实现DDC的各个模块。

经过硬件调试,系统功能正常,将FPGA产生的各部分数据导入MARLAB中,得出的运算结果波形如图6所示。

DDC模块原本不改变输入信号的位宽,输入为14位,100 MHz的单路信号,输出本应为两路位宽14位,速率100MHz的零中频正交信号。

而实际输出为两路位宽30位,速率100 MHz的零中频正交

信号,所以先要截取该两路30位信号,恢复至14位宽度,然后再抽取。

经实验验证,在设计中,对两路(1/Q路)位宽为30位的信号进行13~26位截位,其效果最佳,信号质量性能都能得到保证。

4 结语

采用FPGA实现DDC,具有速度快,灵活性强等优点。

该系统设计采用Xilinx的FPGA平台,其中有许多免费的IP核可供选用,在实现较好性能的同时,可有效减小开发的周期和难度,因此,该设计方案具有广泛的应用潜力。