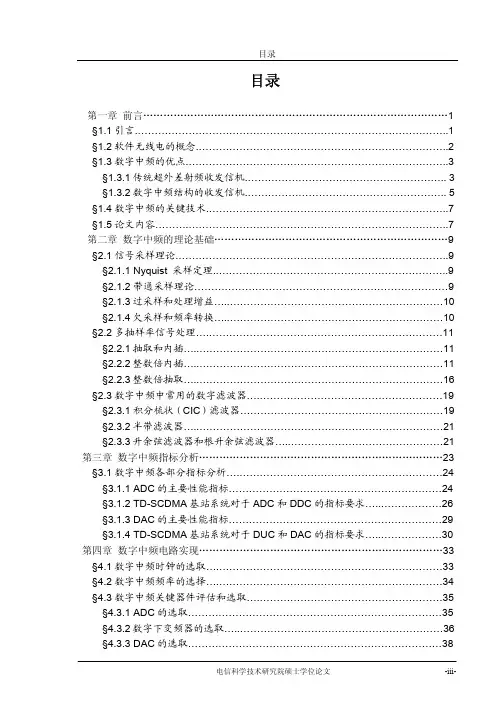

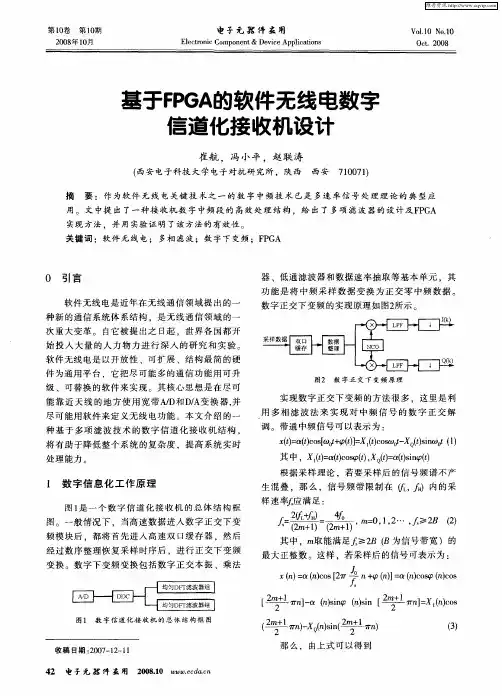

数字中频的基本原理和FPGA的实现

- 格式:doc

- 大小:445.50 KB

- 文档页数:10

数字差分BPSK扩频接收机的设计与FPGA实现摘要:本文提出了一种全数字差分BPSK扩频接收机的实现方案,通过Simulink仿真验证了该方案具有较低的误码率。

然后利用Verilog硬件描述语言编程,通过了综合和仿真验证,最后在Xilinx公司FPGA上实现了整个系统。

该系统经过优化设计,具有易于硬件实现,占用芯片资源少等优点,对实际工程有一定的指导意义。

关键字:FPGA,扩频,同步,数字差分,BPSK,接收机,可编程逻辑1引言随着软件无线电技术的发展,传统的基于复杂模拟硬件的接收设备逐渐向数字IC 产品过渡,而FPGA作为ASIC产品原型设计的可编程逻辑器件,以其丰富的逻辑资源和可重新配置的优势,成为人们前期研究与开发的重要手段。

因此,在可编程逻辑器件上实现数字扩频接收机关键技术进行研究,具有重要的应用价值。

本文给出了一种数字差分BPSK直接序列扩频接收机的方案,并通过simulink进行了仿真,同时本文深入探讨了方案中的关键技术在FPGA中的实现结构,在保证系统稳定性,和不影响系统性能的前提下降低硬件复杂度的问题上提出了FPGA实现方案,并最终在Xilinx XC2V500 FPGA上实现了整个系统,对工程实践有一定的指导意义。

2. 数字差分BPSK扩频接收机的结构与实现数字BPSK扩频接收机原理图见图1,系统主要可以分为三个部分:解调电路、PN 码捕获电路和PN码跟踪电路。

图1 数字差分BPSK扩频接收机原理图通过Simulink仿真该系统,同时结合Xilinx公司FPGA特点,对硬件电路实现进行探讨,在保证系统性能的前提下,减小硬件实现复杂度。

下面将具体介绍电路各部分原理与硬件实现。

2.1 数字解调BPSK信号的解调通常采用相干解调的方式,已经证明跟踪低信噪比的抑制载波信号的最佳装置是Costas环及平方环[1],并且这两种结构是等效的,在数字域中通常采用Costas环实现载波同步。

Costas环电路结构见图1解调电路,电路各部分实现如下。

第30卷 第3期2009年9月制 导 与 引 信GU I DANC E &F UZEVol.30No.3Sep.2009文章编号:167120576(2009)0320056204基于多相滤波的数字中频正交相干检波系统王亚军, 李 明(西安电子科技大学雷达信号处理国家重点实验室,陕西西安710071) 摘 要:针对宽带接收机数据率高而难以实时处理的问题,分析了基于多相滤波的数字中频正交相干检波方法,仿真比较了该方法与基于传统结构低通滤波器的实现方法的性能,给出了在F P G A 中的实现结构,并进行了仿真验证,证明了该方法可以在不增加资源消耗量的同时,大大提高系统吞吐率,具有明显的速度优势,能较好地满足宽带接收机的实时性要求。

关键词:相干检波;下变频;低通滤波器中图分类号:TN911.72 文献标识码:ADigital Inter media te Fr equency Q ua drature Coher entDetection System B a sed on Polyphase Filter ingWA N G Ya 2j un , L I M i ng(Nat ional K ey Lab of Radar Signal Processi ng ,X i ’a n Elect ron Science andTechnology Univer si ty ,X i ’an Shaanxi 710071,China) Abst ract :It ’s difficult to p rocess real 2ti me for t he high data rat e of wideba nd receiver ,t he met hod of di gi tal i nt ermediat e f requency quadrat ure coherent det ection based on poly 2pha se filt eri ng wa s a nalyzed.The perfor ma nce of t hi s met hod was compared wit h t hat of t ra 2dit ional low pass fi lte r archit ect ure by si mulat io n.The i mpl eme nta tion on F P G A was showed and t he si mulat io n resul t i ndicat es t hat for it s high t hroughput rat e a nd low reso urce cost ,t hi s met hod has a grea t advant age of speed and i s very fit for t he real 2ti me demand of t he wideband recei ver.K ey w or ds :coherent detection ;dow n conversion ;low pass fil ter收稿日期:2009-02-20作者简介王亚军(3),男,硕士,主要从事实时信号处理的研究;李 明(6),男,教授,博士生导师,主要从事雷达系统设计、雷达信号处理与监测、高速实时信号处理等的研究。

装……订……线基于FPGA的分频器设计一、实验目的1、了解EDA软件在电子设计当中的重要作用EDA:EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术:就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性。

2、熟悉并掌握MAXPLUS II 或QUARTUS II等开发软件的基本使用方法。

3、运用图解法设计分频器电路,并进行电路仿真。

二、实验内容利用MAXPLUS II开发软件设计分频电路。

1MHz图分频电路框图从图中我们可以看出将1MHZ的脉冲连续6次除10,即可得到我们需要的输出频率。

利用MAXPLUS II 或QUARTUS II等开发软件的器件库,找到一个BCD的计数器:74LS160,(如图)从它的波形图中可看到它具有的逻辑功能:BCD计数,异步清零,有进位输出。

其中CLK—为时钟信号;ENT、ENP—为使能信号,高电平有效;CLRN—异步清零端,电平为高时,计数器清零,电平为低时,允许计数;QD~QA—计数器输出端;RCO—进位输出端。

图74LS160图形符号装……订……线图74LS160波形图74LS160是一个对输入时钟进行十分频的器件。

当计数器从0计数到9时,RCO从低电平跳到高电平,在下一个脉冲到来时,RCO再回到低电平。

每十个计数脉冲RCO翻转一次,利用RCO特性,将前一级的TC输出端接到下一级的时钟输入端,就完成了连续分频的目的。

调用6次74LS160,即可完成设计电路要求。

结合FPGA与DSP实现对高速中频采样信号处理平台的设计详解现代社会正向数字化、信息化方向高速发展,在这一过程中,往往需要高速信号的实时性数字化处理。

例如,随着科技的进步,现代雷达等应用信号的数字化处理上有了长足的发展,但也带来了新的问题,这些应用的数字信号处理具有海量运行需求的应用背景,如巡航导弹末制导雷达地形匹配、合成孔径雷达的成像处理、相控阵雷达的时空二维滤波处理等领域。

目前,单片DSP难以胜任许多信号处理系统的要求。

而常见的解决方案也是高速A/D采样与信号处理功能是在多块不同的板卡上实现,这给实际应用带来很多不便。

鉴于上述现有技术所存在的问题,本设计平台的目的是:

(1)实现高速中频信号(如雷达信号)的数字化处理并进行实时传输数据或进行数据的实时计算,并能通过输出电路进行结果显示;

(2)自定义控制总线可以实现对高速中频信号处理板进行灵活控制,具有较强的可配置性和丰富的灵活性;

(3)高速A/D采样与D/A回放及数据处理单元集成在一块板上,在集成度高的同时也降低了高速信号在传输过程中出现差错的概率。

1 平台设计方案高速中频采样信号处理平台由主控制电路、高速A/D与D/A电路、信号处理单元电路、光纤通道电路、时钟管理电路、存储单元和外部接口电路组成,其总体框图如图1所示。

在实际应用过程中,四路A/D通道可以接收不同的信号源的信号,D/A通路可以对外进行数据显示等多种功能,时钟管理电路管理内外时钟的使用及对板上系统供给工作时钟,两路光纤通道可以与其他高速设备相连接,自定义总线可以与CPU或主控制器相连接对平台进行有效灵活的控制。

1.1 高速A/D与D/A设计

四路高速A/D采样通道采用两片NS公司的ADC081000实现,每片有两个A/D通道,。

数字中频的基本原理和FPGA的实现 1.基本原理 数字中频主要分两部分,数字上变频(DUC)和数字下变频(DDC)。它们的主要功能是相反,但原理和实现的方法是十分相似。在R8905项目中由于采用了零中频技术,数字上变频和下变频有一些差别,数字上变频没有了NCO模块。另外为了降低输出信号的峰均比又加入了削峰模块CFR,而CGC模块的引入则是补偿削峰所引起的功率损失。

CPRI接口处理RCF 2倍内插HB2倍内插CFRCGCCIC54倍内插

3.84M7.68M15.36M61.44M

图1 数字上变频模块框图 在数字下变频中RSSI模块是信号的功率检测模块,它配合AGC电路将信号的输出功率稳定在一定范围内。

NCOCIC54倍抽取HB2倍抽取RRCAGC

RSSI61.44M15.36M7.68Mcpri

图2 数字下变频模块框图 在DDC和DUC中主要使用3种滤波器分别是RRC,HB和CIC,它们个自有个自的特点。 RRC滤波器一般来讲阶数比较多,多用于低频处。由于它的阶数比较多,所以可以得到比较锐利的带通特性,但它所用的乘法器比较多。CIC滤波器不需要乘法器,但它的带内不是很平坦,适合用在高频处。而HB滤波器的特性正好在它们之间,它有约一半的系数是0可以讲乘法器的个数减少一半。 削峰模块CFR实际上也是一组滤波器,它的功能是将CDMA信号中的峰值信号减小一些,以减小输出信号的峰均比,使射频功率放大器的效率更高。削峰的模块框图如图3 图3 单级削峰示意图 削峰的原理是这样的一个复信号(I,Q)如果它的模大于某个门限,就将其减去这个门限得到一个复信号(dI,dQ),否则(dI,dQ)=(0,0)。将(dI,dQ)送到fir滤波器中,fir滤波器是一个低通滤波器将峰值限定在一定的带宽内,防止影响临道。将原信号(I,Q)减去滤波后的信号(fir_i,fir_q)就得到了削峰的值。如果有必要这这样的削峰可以连续做几次,在R8905设计中削峰用了两次。 2. 滤波器的设计 由于在滤波的同时还有内插和抽取,所以充分利用这一特性可以减少FPGA使用的资源。另外滤波器的系数一般都是对称的,可以将头和尾的数相加再乘滤波器的系数,这样可以大大减少乘法器的使用。以R8905中的上变频RRC为例来说明: 设a(n)为RRC滤波器的系数而x(n)为3.84M输入数据则考虑了内插后的滤波器的数学表达式为 y=a(0)*x(n)+a(1)*0+a(2)*x(n-1)+.........+a(n-1)*0+a(0)*x(0) =a(0)*(x(n)+x(0)) +a(2)*( x(n-1)+x(1))...... 其FPGA实现的逻辑框图如下 图4 DUC RRC滤波器实现逻辑图 其中使用了4个乘法器和四个RAM以及一个ROM来存数据。RRC_CTR_6144模块控制这些乘法器和ROM。参考代码如下: ////////////////////////////////////////// ////////////////////////////////////////// // Date : Sat Jul 21 10:51:51 2007 // // Author : duan chenghong // // Company : zte // // Description : // RRC滤波器用了4个RAM和4个乘法器完成IQ两路的滤波功能, // I,Q的处理方法完全相同。数据同时写入4个RAM中,但读的地址不// 同,由于RRC滤波器的系数是对称的所以读RAM的地址也是对称的,将地址 // 对称的RAM读出数相加再和RRC滤波器系数相成再累加就可以得到最后的结果 ////////////////////////////////////////// ////////////////////////////////////////// module rrc_ctr_6144 (waddr, raddr0, raddr1, raddr2, raddr3, clk, reset, data_en, dat0_out, dat1_out, dat2_out, dat3_out, coef, raddr_coef, ih, il, qh, ql, coef_h, coef_l, mih, mil, mqh, mql, idat, qdat, rrc_en); output [5:0] waddr ; reg [5:0] waddr ; output [5:0] raddr0 ; wire [5:0] raddr0 ; output [5:0] raddr1 ; wire [5:0] raddr1 ; output [5:0] raddr2 ; wire [5:0] raddr2 ; output [5:0] raddr3 ; wire [5:0] raddr3 ; input clk ; wire clk ; input reset ; wire reset ; input data_en ; wire data_en ;

input [31:0] dat0_out ; wire [31:0] dat0_out ; input [31:0] dat1_out ; wire [31:0] dat1_out ; input [31:0] dat2_out ; wire [31:0] dat2_out ; input [31:0] dat3_out ; wire [31:0] dat3_out ; input [31:0] coef ; wire [31:0] coef ; output [3:0] raddr_coef ; wire [3:0] raddr_coef ; output [16:0] ih ; reg [16:0] ih ; output [16:0] il ; reg [16:0] il ; output [16:0] qh ; reg [16:0] qh ; output [16:0] ql ; reg [16:0] ql ; output [15:0] coef_h ; wire [15:0] coef_h ; output [15:0] coef_l ; wire [15:0] coef_l ; input [32:0] mih ; wire [32:0] mih ; input [32:0] mil ; wire [32:0] mil ; input [32:0] mqh ; wire [32:0] mqh ; input [32:0] mql ; wire [32:0] mql ; output [15:0] idat ; reg [15:0] idat ; output [15:0] qdat ; reg [15:0] qdat ; output rrc_en ; reg rrc_en ; assign coef_h=coef[31:16]; assign coef_l=coef[15:0];

reg [3:0] cnt; always@(posedge clk or negedge reset) if(~reset) waddr<=0; else if(data_en) waddr<=waddr+1'b1;

always@(posedge clk or negedge reset) if(~reset) cnt<=0; else if(data_en) cnt<=0; else cnt<=cnt+1'b1;

assign raddr_coef = cnt[3]?cnt-3:cnt-1'b1; //系数的地址 assign raddr0 =cnt[3]?waddr-23+cnt[2:0]:waddr-23+cnt[2:0]-1; assign raddr1 =cnt[3]?waddr-23+cnt[2:0]+6:waddr-23+cnt[2:0]+6-1; assign raddr2 =cnt[3]?waddr-cnt[2:0]-1:waddr-cnt[2:0]-1 ; assign raddr3 =cnt[3]?waddr-cnt[2:0]-6-1:waddr-cnt[2:0]-6-1 ; // 4个RAM的读地址 always@(posedge clk or negedge reset) if(~reset) ih<=0; else ih<={dat0_out[31],dat0_out[31:16]}+{dat2_out[31],dat2_out[31:16]};

always@(posedge clk or negedge reset) if(~reset) il<=0; else il<={dat1_out[31],dat1_out[31:16]}+{dat3_out[31],dat3_out[31:16]};

always@(posedge clk or negedge reset) if(~reset) qh<=0; else qh<={dat0_out[15],dat0_out[15:0]}+{dat2_out[15],dat2_out[15:0]};

always@(posedge clk or negedge reset) if(~reset) ql<=0; else ql<={dat1_out[15],dat1_out[15:0]}+{dat3_out[15],dat3_out[15:0]}; //为防止相加溢出,补一位

wire [35:0] ex_mih,ex_mil,ex_mqh,ex_mql; assign ex_mih=mih[32]? {3'b111,mih}:{3'b000,mih}; assign ex_mil=mil[32]? {3'b111,mil}:{3'b000,mil}; assign ex_mqh=mqh[32]? {3'b111,mqh}:{3'b000,mqh}; assign ex_mql=mql[32]? {3'b111,mql}:{3'b000,mql}; //为防止累加溢出,补3位