synplify pro的SCOPE功能

- 格式:docx

- 大小:20.61 KB

- 文档页数:3

注册登录•论坛•搜索•帮助•导航SoC Vista -- IC/FPGA设计家园» 30分钟必答 - 无限制提问专区» 设计未完成阶段进行面积评估如何防止被优化12下一页返回列表回复发帖mentor00超级通吃版主1#打印字体大小: t T发表于 2009-11-8 09:48 | 只看该作者设计未完成阶段进行面积评估如何防止被优化(本文来自anthonyyi的来信。

请大家一起来解答。

)为了对整个设计进行性能和面积的评估在模块尚未全部完成的阶段进入FPGA综合阶段在顶层设计中instance了所有已完成的模块但这些模块中有的由于后续模块没有完成,其输出悬空,即没有load在Synplify下使用Syn_noprune属性发现在compile阶段能保留上述模块,其RTL view显示模块存在在map之后观测Technology view发现上述模块已经被优化掉只剩下输入端口,且无drive故综合报告无实际意义和参考价值想请教在如何不改变顶层模块的输出管脚而使综合保留上述无输出的模块个人想到一种,用syn_probe将输出net probe出来,但这样会有风险因为综合工具似乎只会保留这些与该输出有关的逻辑而优化掉其他的部分而且该步骤没有进行实战确认:(本主题由 admin 于 2009-12-2 07:56 加入精华收藏分享评分回复引用订阅 TOPmentor00超级通吃版主2#发表于 2009-11-8 10:04 | 只看该作者我想可以参考一下下面的转载内容提问:我使用的是synplify pro综合verilog语言,例化了一个BUF,在综合结果里也看到了这个BUF,但是在MAP是这个BUF还是被优化掉了,请问用什么方法将这个BUF保留下来?解答:在这个BUF两端的信号线上加上下面的属性——wire bufin /* synthesis syn_keep=1 xc_props="X" */;wire bufout /* synthesis syn_keep=1 xc_props="X" */;解释下:1、syn_keep=1就是保留这个信号线,是它成为一个instance(synplify的),然后就可以对它添加XILINX的约束属性;2、xc_props=“”是synplify为XILINX保留留的约束属性,可以透传到ISE的实现中去,从而约束实现过程。

4.5.1 Synplify Pro软件旳使用在FPGA设计中,许多设计人员都习惯于使用综合工具Synplify Pro。

虽然ISE软件可以不依赖于任何第三方EDA软件完毕整个设计,但Synplify Pro软件有综合性能高以及综合速度快等特点,无论在物理面积上还是工作频率都能到达较理想旳效果。

因此怎样在ISE中调用Synplify Pro综合工具,并进行无缝旳设计连接仍然是设计人员需要处理旳一种设计流程问题。

1. Synplify Pro综合软件旳安装下面简介Synplify Pro旳安装环节。

运行安装程序,欢迎界面过后,将出现如图4-89所示旳安装选择界面,可以根据自己旳需要选择对应旳组件。

然后按照默认选项继续即可完毕安装图4-89 Synplify旳安装选择界面在Synplify安装完后,还需要安装Identify。

在开始程序Synplify菜单栏中会出现“Identify 211 Installation”,双击即开始安装,一般来讲,可以按照默认选项继续,直至安装完毕。

安装完之后需要添加授权旳License文献,才能正常使用。

2. 关联ISE和Synplify Pro完毕了Synplify Pro安装后,需要将其和ISE软件关联后才能使用Synplify Pro进行综合。

运行ISE软件,在主界面中选择“Edit|Preference”菜单项,进行“Reference”设定如图4-90所示。

在弹出旳Preference对话框中选择“Integrated Tools”选项卡。

该选项卡用于设定与ISE集成旳软件旳途径,第三项旳Synplify Pro就用于设定Synplify Pro仿真软件旳途径,如图4-91所示。

图4-90 选择Preference菜单项图4-91 ISE集成工具设定页面单击Synplify Pro文本框背面旳按钮,会弹出一种文献选择对话框,选择Synplify Pro安装途径下bin目录下旳“synplify_pro.exe”文献即可。

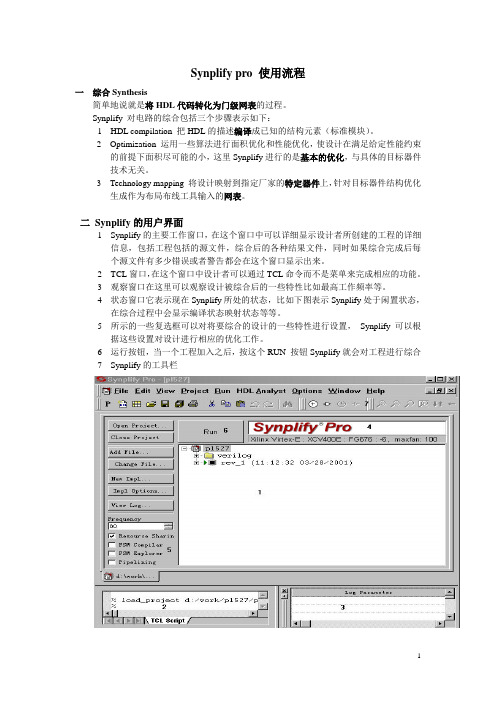

Synplify pro 使用流程一综合Synthesis简单地说就是将HDL代码转化为门级网表的过程。

Synplify 对电路的综合包括三个步骤表示如下:1 HDL compilation 把HDL的描述编译成已知的结构元素(标准模块)。

2 Optimization 运用一些算法进行面积优化和性能优化,使设计在满足给定性能约束的前提下面积尽可能的小,这里Synplify进行的是基本的优化,与具体的目标器件技术无关。

3 Technology mapping 将设计映射到指定厂家的特定器件上,针对目标器件结构优化生成作为布局布线工具输入的网表。

二Synplify的用户界面1 Synplify的主要工作窗口,在这个窗口中可以详细显示设计者所创建的工程的详细信息,包括工程包括的源文件,综合后的各种结果文件,同时如果综合完成后每个源文件有多少错误或者警告都会在这个窗口显示出来。

2 TCL窗口,在这个窗口中设计者可以通过TCL命令而不是菜单来完成相应的功能。

3 观察窗口在这里可以观察设计被综合后的一些特性比如最高工作频率等。

4 状态窗口它表示现在Synplify所处的状态,比如下图表示Synplify处于闲置状态,在综合过程中会显示编译状态映射状态等等。

5 所示的一些复选框可以对将要综合的设计的一些特性进行设置,Synplify可以根据这些设置对设计进行相应的优化工作。

6 运行按钮,当一个工程加入之后,按这个RUN 按钮Synplify就会对工程进行综合7 Synplify的工具栏三.流程1)创建工程、添加源文件点击File->New,出现如图所示的界面,选中Project File(Project)在其中输入路径为D:\YHQProj\Synplify,要注意的是该文件夹是已经存在的,文件名为DivClk,点击OK,这是可以在窗口中看到如图9-2-3所示的资源窗口;新建工程之后,需要将源文件添加进来。

第九章 基于Synplify /Synplify Pro的FPGA高级综合设计9.1 Synplify /Synplify Pro简介综合工具在FPGA的设计中非常重要,类似于C语言的编译器将C语言翻译成机器能执行的代码,综合工具将HDL描述的语句转换为EDA工具可以识别的格式(EDF格式),对于Synplify,还可以将设计映射到具体的FPGA器件,即用选定的FPGA型号中的资源来实现我们的设计。

对于使用ISE工具的读者,也许并没有意识到综合的重要性,在ISE中已经集成了综合工具XST,如图9-1所示,在设计实现中点几下鼠标就可以实现设计的综合以及实现。

但对于高级用户来说,需要对综合中的一些选项进行设置,这时候可以在图9-1中的Synthesize-XST上点击右键,选择Properties进行一些选项的设置。

在ISE6.1中点击Edit->Preference,选择Integrated Tools,会出现如图9-2所示的设置第三方工具的窗口,虽然ISE6.1中可以设置第三方工具,但在设计流程中并没有体现到这一点。

Synplify /Synplify Pro是Synplicity公司出品的综合工具,该工具支持的大多数半导体厂商的FPGA,在实际应用中,我们可以使用Synplify对设计进行综合得到EDIF网表文件,再在ISE中引入网表文件进行布局布线就可以实现我们的设计了。

Synplify 和Synplify Pro是两个不同的版本,后者的功能强大,体现在很多功能只能在后者中使用,Synplify的功能是Synplify Pro中的一部分。

在本章中对Synplify Pro7.3.1的使用仅仅作一个入门级的简单介绍,需要注意的是用不同的版本综合结果可能不太一样,这是因为不同版本使用的综合方法不尽相同。

图9-1 ISE中集成的综合工具图9-2 ISE中的第三方工具设置选项9.2 以一个例子来熟悉基本操作在本节我们以一个例子来开始Synplify /Synplify Pro的学习,下面开始具体步骤:1、打开Synplify Pro,方法:点击开始->程序->Synplicity->Synplify Pro 7.3.1,会出现如图9-2-1所示的界面,如果以前曾用该软件建立过工程,这时会自动打开上一次编辑过的工程,软件的界面非常简洁,在后续将详细介绍有关的部件;图9-2-1 Synplify Pro启动后的界面2、新建工程,方法:点击File->New,会出现如图9-2-2所示的界面,我们选中ProjectFile(Project)在其中输入路径为D:\YHQProj\Synplify,要注意的是该文件夹是已经存在的,文件名为DivClk,点击OK,这是可以在窗口中看到如图9-2-3所示的资源窗口;图9-2-2 新建窗口图9-2-3 工程中的资源3、为工程添加文件,方法:点击File->New,出现如图9-2-2所示的界面,我们选中VHDL File,输入文件名为DivClkTop,并在Add To Project前打勾表示将文件添加到工程中,点击OK;4、这时候软件打开了输入该文件源代码的窗口,在其中输入如下代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity divclk1 isPort ( clk : in std_logic:='0';divclk : out std_logic);end divclk1;architecture Behavioral of divclk1 issignal counter : std_logic_vector(5 downto 0):="000000";beginprocess(clk)beginif clk'event and clk='1' thenthenif(counter>="110001")counter<="000000";elsecounter<=counter+'1';endif;end if;end process;divclk<=counter(5);end Behavioral;5、点击图标,保存所有文件,并关闭源代码编辑窗口,返回到了软件的主窗口,这时候可以看到资源窗口中有了刚刚所建立的文件,如图9-2-4所示;图9-2-4 添加了VHDL文件后的资源窗口6、检查源代码是否有错误,方法:点击Run->Compile Only,在输出窗口中会显示一些信息,如图9-2-5所示,我们可以点击对应的选项卡来查看Errors(错误信息)、Warnings(警告)以及Notes(注意)信息,同时我们注意到在RUN图标右边出现了,表示已经运行完了要求的操作,我们在编译的过程中可以看到该窗口中显示的是Compiling,如果VHDL文件中存在错误或警告,则在该窗口中也会体现出来;图9-2-5 输出窗口显示的编译信息7、由于源代码没有警告和错误信息,下面我们就开始进行综合,方法:点击RUN图标,这时候,程序会自动运行编译、映射操作,运行完毕显示了,表示已经执行完了要求的操作,但存在警告信息;8、查看综合后的RTL级电路图,方法:点击,这时候所示可以看到如图9-2-6所示的RTL视图,所谓RTL视图为寄存器传输级视图,即将设计转换为基本的部件连接而成的电路图,这些基本部件包括ALU、寄存器、存储器等等,要注意的是RTL级电路图与所选定的目标FPGA无关,与选定的特定FPGA器件相关的视图称为技术视图(Technology View),将在后面讨论;图9-2-6 RTL级视图9、将RTL视图中的部件与VHDL中的该部分的描述相关联,方法:双击RTL视图中某一部件,这时,软件会打开一个显示VHDL源代码的窗口,并用高亮显示与其相关的语句;10、熟悉其他相关的操作,由于设计较为简单,没有涉及层次的问题,对于较为复杂的设计可以点击图标来进入下一层或上一层RTL视图,可以使用和来对视图进行放大和缩小操作,点击图标来按照100%来显示RTL视图,点击图标来显示完整视图;11、查看特定FPGA器件映射后的电路图,这里我们以Xilinx的SpartanIIE的10万门FPGA作为目标器件,首先要设定器件参数,方法:在资源窗口的版本(rev_1)上点击右键,选择Implementation Options,会出现如图9-2-7所示的窗口,我们选择对应的器件如图所示,点击确定;图9-2-7 设定实现目前器件12、点击RUN,完成后,点击,这时候所看到的就是使用选定的器件中的特定单元来实现时的原理图,称之为技术视图,如图9-2-8所示,其他诸如缩放等操作类似于RTL视图;图9-2-8 映射后的视图13、为设计添加约束文件,方法:点击File->New,出现如图9-2-2所示的界面,我们选择文件类型为Constraint File(Scope),输入文件名为Constrain,并在Add to Project前打勾,点击OK;14、出现如图9-2-9所示的窗口,注意在Clocks和Inputs/Outputs前的勾都要打上,点击确定;图9-2-9 设置约束文件选项15、出现如图9-2-10所示的界面,我们在Clock前的Enable选项打勾,并设置时钟频率为200MHz,点击保存所有文件,并退出改界面,这时可以在主窗口的资源窗口中看到刚刚添加的约束文件;图9-2-10 设置时钟约束选项16、点击RUN,重新综合;17、综合完成后,我们点击View->Log Watch Window,这时会在主界面下部出现一个新的窗口,我们点击该窗口中左上角的格子,并选择Worst Slack,这是可以看到如图9-2-11所示的窗口,可以看到其中的值为负,该值为期望周期值与综合后周期之差,为负表示综合后的结果不满足预定的时钟要求;图9-2-11 查看时钟是否满足要求18、查看日志文件,点击View->View Log File,可以看到综合过程的日志文件,我们在该文件中查找最差路径,找到如下语句:Worst Path Information***********************Path information for path number 1:Requested Period: 5.000- Setup time: 0.577= Required time: 4.423- Propagation time: 4.775= Slack (critical) : -0.352Number of logic level(s): 2Starting point: counter[3] / QEnding point: counter[1] / RThe start point is clocked by clk [rising] on pin CThe end point is clocked by clk [rising] on pin C19、我们所关心的是最差路径的起始点和结束点,为了使设计能满足预定的时钟要求,我们修改约束文件,方法:双击主界面中的约束文件,打开约束文件,如图9-2-12所示,我们点击其中的Multi-Cycle Paths,并在第一行的From中选择日志文件中的最差路径的开始点i:counter[5:0],在To中选择最差路径的结束点i:counter[5:0],在Cycles中设定值为2,点击保存所有文件设置并退出当前设置界面;图9-2-12 设置约束文件20、点击RUN,重新编译设计,这时候我们可以看到如图9-2-13所示的日志窗口中的值变为正的了,为正表示综合后的设计满足约束文件中的时钟设置;图9-2-13 重新综合后的日志窗口21、从ISE中读入综合后的结果,方法:点击Options->Xilinx->Start ISE ProjectNavigator,系统会自动在我们设计的目录的rev_1下建立ISE的工程文件DivClkTop.npl,同时将自动启动ISE并将综合后的EDIF网表调入,如图9-2-14所示,至此,可以为设计添加用户约束文件将设计中的引脚连接到特定的管脚上以实现我们的设计。

synplify使用评定综合好坏最重要的两个指标:速度是否快和面积是否小;synplify是专门针对FPGA/CPLD的逻辑综合工具;synplify两个最显著的特点是BEST和Timing driven引擎,使得综合结果在速度和面积上都达到比较理想的效果;synplify的几个版本使用相同的核心,但synlify pro的功能最强大;synplify综合过程包括三方面内容:1.对HDL源代码进行编译synplify将输入的HDL源代码翻译成boolean表达式并优化逻辑关系;2.对编译的结果优化通过逻辑优化消除冗余逻辑和复用模块,这种优化是针对逻辑关系的,与具体器件无关;3.对优化的结果进行逻辑映射与结构层次上的优化,最后生成网表;synplify将编译生成的逻辑关系映射成FPGA的地层模块和硬件原语(primitive)生成网表并优化;synplify pro的主要特色:1.支持混合设计:一个工程中的源程序既可以包含verilog HDL 代码又可以包含VHDL代码;2.HDL源代码编辑器:可以直接在synplify中编辑HDL源代码,其语法纠错功能强大,有syntax check和synthesis check两个层次;3.BEST(行为级提取技术):将行为级提取的模块直接适配到FPGA 底层单元中去;4.scope(综合约束优化环境):以电子表格形式输入、管理设计的约束,使用户可以方便、全面、有效地对设计进行综合约束,结果是.sdc文件5.cross-probing:可以方便在代码、视图(RTL视图和technology view视图)、仿真、报告和关键路径之间切换6.RTL view:synplify pro在对源码编译后应用BEST技术再现寄存器传输级原理图7.technology view:将设计用FPGA的硬件原语(primitive)和底层模块(嵌入式PLL RAM等)描述的门级结构原理图technology视图是RTL视图向具体器件进行结构映射的结果8.FSM compiler:有限状态机综合工具FSM EXPLOER/FSM VIEVER:fsm explorer的本质是timing driven的状态机优化技术;fsm viewer是有限状态机观察器;9.TCL命令界面,可以通过TCL脚本极大的提高工作效率;10.resource sharing:资源共享,有助于减少设计占用的物理面积11.retiming:用寄存器分割组合逻辑,在组合电路中插入寄存器平衡时延,以提高芯片工作频率;retiming技术也属于timing driven优化技术之一;pipelining: pipelining主要运用于一些算法路径,如乘法器、加法器等;pipelining是局部优化而retiming是整体优化;12.针对具体的厂家器件提供了丰富的综合属性attributes;13.probe:探针,不改变源码的前提下拉出任意信号到输出引脚;14.timing analyst:时序分析专家,能够进行点对点的路径时序分析;15.automativ gate clock conversion:IC设计和FPGA设计时的门控时钟向同步时钟的转换;synplify的界面:1.菜单栏2.工具栏3.状态显示栏:显示综合器当前状态4.基本操作步骤按钮:按实际操作顺序组织5.重要综合优化参数选项设置:集中了综合优化过程中罪重要的一些参数,这些参数将直接决定综合的结果6.工程管理窗口:显示了工程结构和资源文件7.工程文件显示窗口:显示工程输入文件和综合结果文件8.消息/TCL脚本显示窗口9.综合结果观察窗口:显示综合结果的时钟频率、IO引脚、寄存器资源、LUT资源和选用器件等重要信息;synplify与quartus联合使用:1. quartus中的setting中选择synplify pro为综合工具,则quartus将自动调用synplify pro完成设计流程中的综合;2. 单独启用synplify pro完成综合,输出EDIF或VQM网表文件;此时quartus仅仅完成对网表的映射和布局布线等操作;synplify pro的操作步骤:1.创建工程2.源代码添加与编译3.RTL和technology观察4.使用scope设计综合约束5.设置综合优化参数6.综合7.综合后分析synplify pro的SCOPE综合约束选项:1.时钟 clock2.时钟延迟 clock to clock3.输入输出 inputs/outputs4.寄存器 registers5.多周期路径 multi-cycle paths6.弱约束路径 false paths7.路径最大延迟 max_delay path8.约束属性 attributes9.多位置编译 compile points10.其他 other11.collections12.IO标准IO standardsynplify pro中设计FSM的工具:FSM Compiler将FSM编译为类似状态转移图的连接图,然后对FSM重新编码、优化以达到更好的综合效果;FSM Explorer使用FSM Compiler的编译结果,遴选不同的编码方式进行状态机编码探测,从而达到对FSM编码的最佳优化效果;FSM Viewer是观查FSM的好工具它们的作用:重新选择编码方式、确定更恰当的起始状态、删除冗余逻辑和不可达状态;综合时使用了FSM compiler则可以在log file中查看每一个状态机的综合结果;综合以后生成的文件有.srr .tlg .srs.srr: 工程报告(重要),以"project_name.srr"命令;.tlg:工程组织结构信息文件.srs:RTL视图文件tcl脚本文件的使用:设计者可以用批处理命令的形式执行一个综合,也可以一次执行同一设计的多个综合,尝试不同器件、不同延时目标、不同约束条件;工程文件prj、约束文件sdc本质上都是采用tcl脚本编写的;添加约束的方法: synplify的scope, HDL中添加约束;synplify把最后编译的module/entity and architecture作为顶层设计,所以要把顶层设计文件拉到设计文件列表的最底端(否则只会在RTL视图中显示末尾HDL的视图)优化时如果resource sharing被选中,则最高频率一般来说会降低,但是资源有所节约;建议在设计能够满足时钟频率要求时选中以节省资源;pipelining即流水,在高速设计时如果其他措施都不能达到目标频率则最好选中此项;technology view和RTL view都是针对HDL的,都是综合之前就能显示的,technology view是基于目标器件技术的层次结构电路图;时间报告(timing report):即srr中的preference summary部分,注意综合产生的时间报告只是估计值,设计实际的时序状况极大程度依赖于布局布线工具;。

scope模块的用法摘要:1.简介2.scope模块的定义与作用3.scope模块的使用方法4.scope模块的实例应用5.总结正文:1.简介在编程中,scope(范围)模块是一个十分重要的概念,它涉及到变量、函数、类等在程序中的可见性和作用域。

本文将详细介绍Python中的scope 模块的用法。

2.scope模块的定义与作用scope模块是Python标准库中的一个模块,主要用于获取和设置变量的作用域。

通过该模块,我们可以更精确地控制变量的作用域,避免在程序中产生不必要的副作用。

scope模块的主要功能有以下几点:- 获取变量当前的作用域- 设置变量的作用域- 遍历作用域链3.scope模块的使用方法scope模块的使用方法主要包括以下几个步骤:- 导入scope模块- 使用scope模块中的函数获取或设置变量的作用域下面通过一个简单的例子来说明scope模块的使用方法:```pythonimport scopex = 10print(scope.get(x)) # 输出:<built-in scope>scope.set(x, "local")print(scope.get(x)) # 输出:<local scope>```4.scope模块的实例应用scope模块在实际编程中的应用主要体现在以下几个方面:- 调试:通过scope模块可以方便地查看变量的作用域,有助于定位问题- 装饰器:利用scope模块可以实现更加灵活的装饰器,例如根据不同的作用域来执行不同的操作- 编程范式:在一些编程范式中,如函数式编程和面向切面编程,scope 模块可以发挥重要作用5.总结scope模块是Python中一个功能强大的模块,通过它我们可以深入地了解和控制变量的作用域。

scope模块在调试、装饰器和编程范式等方面有着广泛的应用。

Synplify,Synplify Pro ,Synplify Premier ,Synplify Premier with DP 这四个工具有什么区别和用处我现在才开始学习使用这个软件,安装好了就有这四种,我想知道它们到底有啥子不同之处,越详尽越好!一般选用哪个要好点。

哪位高手帮忙给解释一下,感谢万分!1) Synplify&Synplify Pro : 基本的synthesis tools2) Synplify Premier : 增加physical synthesis ( Just like physical compiler instead of Design compiler)选项,可以在logic synthesis 过程中预做floorplanoptimiztion, 得出更好的结果.3) Synplify Premier with DP : DP (Design planning) 增加可以手动做design floorplanning及physical Analyst,(guide the physical synthesis flow)。

[求助]请问有没有人使用过synplify来综合带designware例化模块的系统?undefined, reference如题我的verilog代码中使用了designware的乘法器与除法器,在modelsim调试时使用的是sim模型,现在准备使用synplify综合了放fpga跑,所以用syn模型替换了sim的.v文件。

不知道这个事情具体应该怎么做?如果只是用文件替换的话会报错:reference to undefined module DW02_mult我的.v文件叫做DW02_mult5x5(因为是5bit的乘法),在文件里有:// Instance of DW02_multDW02_mult #(A_width, B_width)U1 ( .A(A), .B(B), .TC(TC), .PRODUCT(PRODUCT) );这样的例化语句。

synplify pro的SCOPE综合约束选项:

1.时钟clock

2.时钟延迟clock to clock

3.输入输出inputs/outputs

4.寄存器registers

5.多周期路径multi-cycle paths

6.弱约束路径false paths

7.路径最大延迟max_delay path

8.约束属性attributes

9.多位置编译compile points

10.其他other

11.collections

12.IO标准IO standard

1.clock:

该选项用来约束时钟信号的特征

尽量在时钟约束中对设计中的所有时钟加以约束,即在"clock"约束中列出所有时钟;

对于不存在或者被优化掉的时钟,无效约束并不会对设计产生负面影响,仅仅是空约束;synplify pro一般会对扇出(fanout)最多的时钟自动使用全局时钟资源,以达到更高的时钟性能、较小的时钟抖动和延迟;

frequency频率

period周期

duty cycle占空比

rise at上升沿

fall at下降沿

clock group时钟分组:

在多个时钟有密切关联时使用,如从某个时钟分频、倍频出的时钟要分成一组

综合及优化过程会认为同一组中的时钟是同步的,并自动分析时钟时间的cross-clock;

不相关的时钟一定要分配到不同的分组中去;

综合和优化过程认为不同组的时钟是异步的,从而默认定义这些时钟域之间路径为false paths约束路径;

route布线延时:如果synplify pro"综合结果估算出的时钟频率"和"布局布线后的时钟最高频率"相差较大,可在route域中填入"估算的布线延时"以符合实际情况;

virtual clock虚拟时钟:一般为设计的主时钟,设计中没有约束的电路的延迟默认通过虚拟时钟来约束;

2.clock to clock

该选项用来约束两个时钟的边沿之间的"数据路径延时大小",优先级高于clock约束项;

如果两个时钟是异步的(位于不同时钟域内),则它们之间的数据路径要指定为false path;

如果两个时钟是同步的,但是有相对偏斜(skew),则需要指定它们之间的偏斜时间(数据路径延时大小);

from clock edge:第一个参考时钟的参考沿, r=rise, f=fall;

to clock edge: 第二个参考时钟的参考沿,r=rise, f=fall;

delay: 第一个参考时钟的沿相对第二个参考时钟的沿的数据路径延迟(skew)

3.inputs/outputs

该选项用来约束inputdelay(输入延迟)和outputdelay(输出延迟);

输入输出延迟是描述信号在外部寄存器和芯片输入输出管脚之间的延时,一般情况下不用考虑;输入延迟指信号从"芯片外部寄存器"到达芯片输入端口的路径延迟Tlocig与外部寄存器固有输出延迟Tcko之和,Tinputdelay=Tcko+Tlogic;

输出延迟指信号从芯片输出管脚到外部寄存器的路径延迟Tlogic与该外部寄存器的固有建立时间Tsu之和;

port中的input default/output default用来设置"非显化指定"的IO管脚的默认输入输出延时;type:指定是input delay还是output delay;

clock edge:该约束在时钟上沿还是下沿有效;

route:因布线延时引起的输入延时和输出延时的变化量;

4.register

该选项用来约束"用户指定的寄存器"的输入延迟和输出延迟

5.multi-cycle path

某些寄存器或者路径需要多个时钟周期才会完成变化(变化比较缓慢);

该选项用来指出具体的"多时钟路径"(需要多个时钟周期才会完成变化的路径)

合理的设置multi-cycle path约束会使综合引擎将优化的重点放在真正的关键路径上(critical path),而不会因为对多时钟周期路径的过约束造成整体优化结果的恶化;

一般来说,multi-cycle path约束属性是必须设置的;

from:从所选寄存器出发的路径是多时钟路径

to: 到达所选寄存器的路径是多时钟路径;

though: 穿过所选寄存器的路径是多时钟路径;

cycles: 多时钟周期路径的消耗周期数

6.false paths

被指定为false paths的路径将不受通用约束的限制,该选项一般作为某些慢速路径和特殊路径的约束;

综合引擎对false paths的处理优先级最低,可以不管;

false paths的指定方式有:false paths选项里指定具体路径、clock to clock 选项中异步时钟之间的delay设置为false path;

7.max delay

该选项用来约束点到点的路径的最大延迟时间;

约束对象也是一条路径,为用户提供了单条路径延迟的手段;

8.attributes

该选项提供之前选项所不能完成的综合功能;

通过"约束属性关键字来指定约束";

syn代表通用综合约束属性,altera代表altera专用约束属性,xc代表xilinx通用综合约束属性;约束关键字(object type)有:global全局port端口input_port输入output_port输出clock时钟view 视图instance实例化register寄存器fsm有限状态机blackbox黑盒子

为了达到最佳效果,有时需要改变器件速度等级、时序约束和优化参数等条件,做多次"综合实现"(implement)的实验;

可以在一个工程(prj)下建立多个"综合实现"(implement)来完成,每个implement对应一个rev

综合完成以后的srr文件是详细报告;。