6-2 无限长单位冲激晌应 (IIR) 数字滤波器的设计方法

- 格式:ppt

- 大小:7.23 MB

- 文档页数:205

摘要数字信号处理在科学和工程技术等许多领域中得到了广泛的应用,其中数字滤波器是现代数字信号处理系统的重要组成部分。

无限长单位冲激响应(IIR)数字滤波器是非常重要的一类滤波器,与有限长单位冲激响应(FIR)数字滤波器相比,IIR能够以较低的阶次获得较高的频率选择特性从而得到了广泛的应用。

本课题采用一种基于现场可编程门阵列(FPGA)的IIR数字滤波器的设计方案。

首先基于IIR数字滤波器的相关理论知识,研究了IIR数字滤波器的常用设计方法,并分析了各种IIR数字滤波器的实现结构等基本理论,由分析结果确定了所要设计的IIR数字滤波器的实现结构。

然后基于FPGA的结构特点,研究了IIR数字滤波器的FPGA设计与实现,并通过Quartus Ⅱ设计平台,采用自顶向下的模块化设计思想,将整个IIR数字滤波器分为:时序控制、延时、补码乘加和累加四个功能模块。

分别对各模块进行VHDL语言描述,并进行了仿真和综合。

仿真结果表明,本设计的IIR数字滤波器运算速度较快,系数改变灵活,有较好的参考价值。

关键词:数字滤波器;无限长单位冲激响应;现场可编程门阵列;VHDL硬件描述语言ABSTRACTDigital signal processing is widely used in lots of fields, such as in science and project technique, Digital filter is one of the important contents of digital signal process. Infiinite impulse response units (IIR) digital filter is a very important type of filters. With its good characteristic of frequency selection in lower order in comparison with finite impulse response (FIR), IIR digital filter is widely applied in modern signal processing systems. This subject is a IIR digital filter design based on the using of field programmable gate array (FPGA). Firstly, based on the analysis of IIR basic realization architectures and the related theoretic analysis, the design methods of IIR sigital filter has been discussed and the structures of a variety of IIR digital filter which can be realized has been analysised. For the results of the theoretical analysis, the final architecture and realization of IIR digital has been decided, Based on the structural characteristics of FPGA, the FPGA design and realization of IIR digital filter has been researched. By used the design plant of Quartus Ⅱ, we adopt blocking method named “Top-down ” and divide the entire IIR digital filter into four blocks, which are Clock control, Time delay, Multiply-addition and Progression. After described with VHDL,we do emulate and synthesis to each block. The result shows that, the introduced IIR digital filter runs fast, and the coefficient changes agility. It has high worth for consulting.Key Words: Digital filter; infinite impulse response units; field programmable gate array; VHDL hardware description language目录1器件简介 (1)2 IIR数字滤波器的相关理论 (4)2.1 IIR滤波器的基本理论 (4)2.1.1 IIR数字滤波器的幅频特性 (5)2.1.2 IIR数字滤波器的相频特性 (7)2.2 IIR数字滤波器的实现结构 (7)2.2.1 直接型结构 (7)2.2.2 级联型结构 (8)2.2.3并联型结构 (10)2.3 数字滤波器的有限字长效应理论 (10)2.3.1 数字表示 (11)2.3.2 输入量化 (12)2.3.3 系数量化 (13)2.3.4 乘积量化 (17)2.3.5 极限环 (19)3 IIR数字滤波器的分析设计 (21)3.1 IIR数字滤波器的模拟转换设计法 (21)3.2 IIR数字滤波器的S-Z变换设计 (21)3.2.1标准Z变换 (22)3.2.2双线性Z变换 (24)3.3 IIR数字滤波器的零极点累试法 (25)3.4 优化设计法 (25)3.5 IIR数字滤波器的硬件实现方案 (25)4 EDA技术和可编程逻辑器件 (30)4.1 电子设计自动化EDA技术 (30)4.2 可编程逻辑器件 (30)4.2.1 FPGA概要 (31)4.2.2 FPGA设计语言 (31)4.2.3 FPGA开发环境 (32)5 IIR数字滤波器的设计与仿真结果分析 (33)5.1 各模块的设计与仿真结果分析 (33)5.1.1 时序控制模块的设计与仿真结果分析 (33)5.1.2 延时模块的设计与仿真结果分析 (34)5.1.3 补码乘加模块的设计与仿真结果分析 (35)5.1.4 累加模块的设计与仿真结果分析 (36)5.1.5 顶层模块设计 (36)5.2 IIR数字滤波器的仿真与结果分析 (37)5.2.1 IIR数字滤波器的系统设计 (37)5.2.2 IIR数字滤波器的系统仿真与结果分析 (38)5.2.3 高阶IIR数字滤波器的实现 (39)6 IIR数字滤波器的硬件实现 (40)6.1 IIR数字滤波器的硬件实现平台 (40)6.1.1 硬件结构 (40)6.1.2器件介绍 (41)6.1.3 JTAG链简介 (43)6.1.4 FPGA的配置 (44)6.2 IIR数字滤波器的VHDL设计 (45)6.2.1 接口定义 (45)6.2.2 综合与仿真 (45)6.3 数字滤波器的实现 (45)结束语 (46)参考文献 (47)致谢 (48)附录1 各模块VHDL程序 (49)1器件简介数字滤波器是具有一定传输选择特性的数字信号处理装置,其输入、输出均为数字信号,实质上是一个由有限精度算法实现的线性时不变离散系统。

实验四 无限冲激响应(IIR )数字滤波器设计一、实验目的1.熟悉用双线性变换法设计IIR 数字滤波器的原理和方法;2.了解用脉冲响应不变法设计IIR 数字滤波器的原理和方法;3.掌握双线性变换及脉冲响应不变法设计的滤波器的频域特性,了解双线性变换法及脉冲响应不变法的特点;4.掌握数字滤波器的计算机仿真方法;二、实验原理介绍IIR 数字滤波器的系统函数为1z -的有理分式: 1011()1N kk Nk k b z H z a z -=-==+∑∑ 设计IIR 滤波器的系统函数,就是要确定()H z 的阶数N 及分子分母多项式的系数k a 和k b ,使其()()j j z e H e H z ωω==满足指定的频率特性。

由于模拟滤波器的设计有许多简单而严谨的设计公式和大量的图表可以利用,因此IIR 滤波器设计的方法之一是:先设计一个合适的模拟滤波器,然后将模拟滤波器通过适当的变换转换成满足给定指标的数字滤波器。

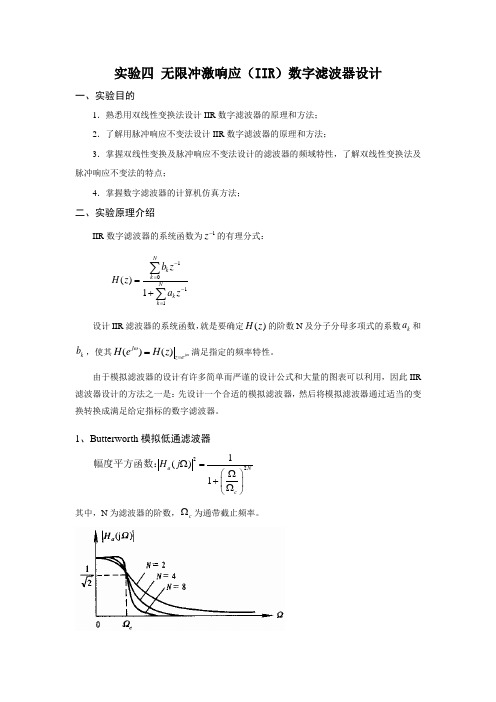

1、Butterworth 模拟低通滤波器221()1a N c H j Ω=⎛⎫Ω+ ⎪Ω⎝⎭幅度平方函数:其中,N 为滤波器的阶数,c Ω为通带截止频率。

2.Chebyshev 模拟低通滤波器 2221()1()a N c H j C εΩ=Ω+Ω幅度平方函数:3、脉冲响应不变法原理 用数字滤波器的单位脉冲响应序列h(n)逼近模拟滤波器的冲激响应()a h t ,让h(n)正好等于()a h t 的采样值,即:()()a h n h nT =其中,T 为采样间隔。

如果以()a H s 和H(z)分别表示()a h t 的拉氏变换及h(n)的Z 变换,则:12ˆ()()sT a a z e k H z H s H s j k T T π∞==-∞⎛⎫==- ⎪⎝⎭∑4、双线性变换法原理双线性变换法是通过两次映射采用非线性频率压缩的方法,将整个频率轴上的频率范围压缩到±π/T 之间,再用sTz e =转换到z 平面上,从而使数字滤波器的频率响应与模拟滤波器的频率响应相似。

第一章 离散时间信号与系统2.任意序列x(n)与δ(n)线性卷积都等于序列本身x(n),与δ(n-n 0)卷积x(n- n 0),所以(1)结果为h(n) (3)结果h(n-2) (2(4)3 .已知 10,)1()(<<--=-a n u a n h n,通过直接计算卷积和的办法,试确定单位抽样响应为 )(n h 的线性移不变系统的阶跃响应。

4. 判断下列每个序列是否是周期性的,若是周期性的,试确定其周期:)6()( )( )n 313si n()( )()873cos()( )(ππππ-==-=n j e n x c A n x b n A n x a分析:序列为)cos()(0ψω+=n A n x 或)sin()(0ψω+=n A n x 时,不一定是周期序列,nmm m n n y n - - -∞ = - ⋅ = = ≥ ∑ 2 31 2 5 . 0 ) ( 01当 3 4n m nm m n n y n 2 2 5 . 0 ) ( 1⋅ = = - ≤ ∑ -∞ = - 当 aa a n y n a a an y n n h n x n y a n u a n h n u n x m m nnm mn -==->-==-≤=<<--==∑∑--∞=---∞=--1)(11)(1)(*)()(10,)1()()()(:1时当时当解①当=0/2ωπ整数,则周期为0/2ωπ;②;为为互素的整数)则周期、(有理数当 , 2 0Q Q P QP =ωπ ③当=0/2ωπ无理数 ,则)(n x 不是周期序列。

解:(1)0142/3πω=,周期为14 (2)062/13πω=,周期为6 (2)02/12πωπ=,不是周期的 7.(1)[][]12121212()()()()()()[()()]()()()()[()][()]T x n g n x n T ax n bx n g n ax n bx n g n ax n g n bx n aT x n bT x n =+=+=⨯+⨯=+所以是线性的T[x(n-m)]=g(n)x(n-m) y(n-m)=g(n-m)x(n-m) 两者不相等,所以是移变的y(n)=g(n)x(n) y 和x 括号内相等,所以是因果的。

IIR数字滤波器的设计步骤1.简介I I R(In fi ni te Im pu l se Re sp on se)数字滤波器是一种常用的数字信号处理技术,它的设计步骤可以帮助我们实现对信号的滤波和频率选择。

本文将介绍I IR数字滤波器的设计步骤。

2.设计步骤2.1确定滤波器的类型I I R数字滤波器的类型分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器。

根据信号的要求,我们需确定所需滤波器的类型。

2.2确定滤波器的规格根据滤波器的应用场景和信号特性,我们需确定滤波器的通带范围、阻带范围和衰减要求。

2.3选择滤波器的原型常用的I IR数字滤波器有巴特沃斯滤波器、切比雪夫滤波器和椭圆滤波器等。

根据滤波器的需求,我们需选择适合的滤波器原型。

2.4设计滤波器的传递函数根据滤波器的规格和选定的滤波器原型,我们需计算滤波器的传递函数。

传递函数表示了输入和输出之间的关系,可以帮助我们设计滤波器的频率响应。

2.5对传递函数进行分解将滤波器的传递函数进行分解,可得到II R数字滤波器的差分方程。

通过对差分方程进行相关计算,可以得到滤波器的系数。

2.6滤波器的稳定性判断根据滤波器的差分方程,判断滤波器的稳定性。

稳定性意味着滤波器的输出不会无限增长,确保了滤波器的可靠性和准确性。

2.7选择实现方式根据滤波器的设计需求和实际应用场景,我们需选择I IR数字滤波器的实现方式。

常见的实现方式有直接I I型、级联结构和并行结构等。

2.8优化滤波器性能在设计滤波器后,我们可以对滤波器的性能进行优化。

优化包括滤波器的阶数和抗混淆能力等方面。

3.总结I I R数字滤波器的设计步骤包括确定滤波器的类型和规格、选择滤波器的原型、设计滤波器的传递函数、对传递函数进行分解、判断滤波器的稳定性、选择实现方式和优化滤波器性能等。

通过这些步骤的实施,我们可以有效地设计出满足信号处理需求的II R数字滤波器。