同步复位与异步复位-异步复位和同步复位区别-异步复位同步释放

- 格式:doc

- 大小:52.00 KB

- 文档页数:6

针对数字系统的设计,我们经常会遇到复位电路的设计,对初学者来说不知道同步复位与异步复位的区别与联系,今天我对这个问题简要的阐述下,希望对初学者有一定的参考意义,若有不正确的地方愿大家明示。

同步复位原理:同步复位只有在时钟沿到来时复位信号才起作用,则复位信号持续的时间应该超过一个时钟周期才能保证系统复位。

异步复位原理:异步复位只要有复位信号系统马上复位,因此异步复位抗干扰能力差,有些噪声也能使系统复位,因此有时候显得不够稳定,要想设计一个好的复位最好使用异步复位同步释放。

同步复位与异步复位的优劣:异步复位消耗的PFGA逻辑资源相对来说要少些,因此触发器自身带有清零端口不需要额外的门电路,这是其自身的优势,通常在要求不高的情况下直接使用异步复位就OK。

下面我用verilog来演示下同步复位与异步复位。

同步复位的verilog程序如下:module D_FF(//Input portsSYSCLK,RST_B,A,//Output portsB);//========================================= //Input and output declaration//========================================= input SYSCLK;input RST_B;input A;output B;//========================================= //Wire and reg declaration//=========================================wire SYSCLK;wire RST_B;wire A;reg B;//========================================= //Logic//========================================= always@(posedge SYSCLK)beginif(!RST_B)B<=1'b0;elseB<=A;endendmodule综合后的RTL级电路图如下:异步复位的verilog程序如下:module D_FF(//Input portsSYSCLK,RST_B,A,//Output portsB);//========================================= //Input and output declaration//========================================= input SYSCLK;input RST_B;input A;output B;//========================================= //Wire and reg declaration//=========================================wire SYSCLK;wire RST_B;wire A;reg B;//========================================= //Logic//========================================= always@(posedge SYSCLK or negedge RST_B)beginif(!RST_B)B<=1'b0;elseB<=A;endendmodule综合后的RTL级电路图如下:通过比较显然异步复位消耗的逻辑资源要少些,因此通常的设计中都采用异步复位的方式,需要进一步的学习的话,可以再研究下其它的资料。

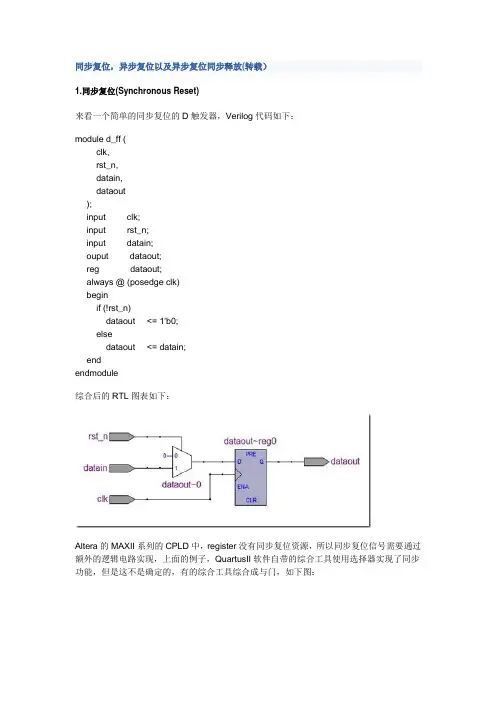

同步复位,异步复位以及异步复位同步释放(转载)1.同步复位(Synchronous Reset)来看一个简单的同步复位的D触发器,Verilog代码如下:module d_ff (clk,rst_n,datain,dataout);input clk;input rst_n;input datain;ouput dataout;reg dataout;always @ (posedge clk)beginif (!rst_n)dataout <= 1'b0;elsedataout <= datain;endendmodule综合后的RTL图表如下:Altera的MAXII系列的CPLD中,register没有同步复位资源,所以同步复位信号需要通过额外的逻辑电路实现,上面的例子,QuartusII软件自带的综合工具使用选择器实现了同步功能,但是这不是确定的,有的综合工具综合成与门,如下图:同步复位的优点:1). 抗干扰性高,可以剔除复位信号中周期短于时钟周期的毛刺;2). 有利于静态时序分析工具的分析;3). 有利于基于周期的仿真工具的仿真。

同步复位缺点:1). 占用更多的逻辑资源;2). 对复位信号的脉冲宽度有要求,必须大于指定的时钟周期,由于线路上的延迟,可能需要多个时钟周期的复位脉冲宽度,且很难保证复位信号到达各个寄存器的时序;3). 同步复位依赖于时钟,如果电路中的时钟信号出现问题,无法完成复位。

2. 异步复位(Asynchronous Reset)来看一个简单的异步复位的D触发器,Verilog代码如下:module prac (clk,rst_n,datain,dataout);input clk;input rst_n;input datain;output dataout;reg dataout;always @ (posedge clk or negedge rst_n)beginif (!rst_n)dataout <= 1'b0;elsedataout <= datain;endendmodule综合后的RTL图表如下:异步复位的优点:1). 无需额外的逻辑资源,实现简单,而且CPLD有针对复位信号的全局不限资源,可以保证复位管脚到各个寄存器的clock skew最小(注意不是到各个寄存器的延迟最小);2). 复位信号不依赖于时钟。

复位电路异步复位同步释放异步复位和同步释放是数字电路设计中常见的两种复位方式。

复位电路的作用是将电路的各个元件状态恢复到初始状态,以确保电路在启动时的可靠性和正确性。

异步复位是指在电路中引入一个异步信号,当该信号为高电平时,电路内部的各个元件都被强制复位为初始状态。

异步复位信号可以是外部输入信号,例如按键、开关等,也可以是内部产生的信号,例如定时器溢出信号等。

异步复位的优点是简单直接,可以快速将电路恢复到初始状态。

但是,异步复位也存在一些问题,例如在复位信号引入时可能导致冲突和干扰,还可能引起时序问题和电路不稳定等。

同步释放是指在电路中采用同步信号来释放复位状态。

同步信号通常是由时钟信号和其他状态信号共同产生的,只有在满足特定条件时才会触发复位释放。

同步释放可以有效地解决异步复位的问题,使电路在复位时更加稳定可靠。

同步释放的实现通常需要借助于锁存器、触发器等元件,通过时序控制和状态判定来实现复位释放的精确控制。

在实际的电路设计中,异步复位和同步释放常常结合使用,以实现对电路的可靠复位和平稳释放。

例如,可以使用异步复位电路将电路初始化为初始状态,然后通过同步信号来控制复位释放的时机,确保电路在启动时的稳定性。

此外,还可以根据具体的应用场景和需求,灵活选择异步复位或同步释放的方式。

异步复位和同步释放是数字电路设计中常用的复位方式,它们通过引入异步信号和同步信号来实现对电路的复位和释放。

在电路设计中,需要根据具体的需求和应用场景选择合适的复位方式,以确保电路的可靠性和正确性。

同时,还需要注意复位信号的引入时机和释放时机,避免引发冲突、干扰和时序问题。

通过合理设计和优化,可以实现高性能、高可靠性的复位电路,提高电路的工作效率和稳定性。

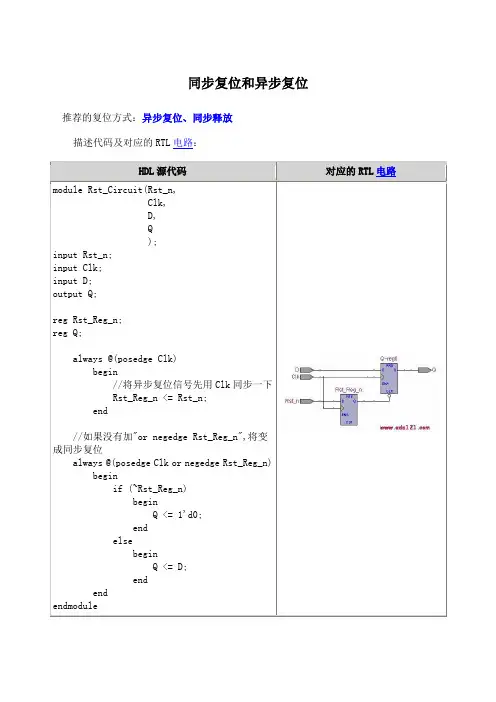

同步复位和异步复位推荐的复位方式:异步复位、同步释放描述代码及对应的RTL电路:同步一下Rst_Reg_n)注:最好在模块外面将异步复位信号同步好,再送至各模块,这样各个模块内部就不需要再分别单独同步了。

下面具体阐述一下同步、异步复位的区别,以及为什么要采用这种方式的原因。

复位电路是每个数字逻辑电路中最重要的组成部分之一。

复位电路有两个工作目的:1、仿真的时候使电路进入初始状态或者其它预知状态;2、对于综合实现的真实电路,通过复位使电路进入初始状态或者其它预知状态。

一般来说,逻辑电路的任何一个寄存器、存储器结构和其它逻辑单元都必须要附加复位逻辑电路,以保证电路能够从错误状态中恢复,可靠地工作。

常用的复位信号为低电平有效信号,在应用时外部引脚接上上拉电阻,这样能增加复位电路的抗干扰性能。

复位方式大致分为两类,即同步复位和异步复位。

这两种复位方式各有优缺点,其应用场合也各不相同。

∙如果目标器件或可用库中的触发器本身包含同步复位端口,则在实现同步复位电路时可以直接调用同步复位端。

然后很多目标器件(如PLD)和ASIC 库的触发器本身并不包含同步复位端口,这样复位信号与输入信号组成某种组合逻辑(比如复位低电平有效,只需复位与输入信号相与即可),然后将其输入到寄存器的输入端。

为了提高复位电路的优先级,一般在电路描述时使用带有优先级的if...else结构,复位电路在第一个if下描述,其它电路在else或else...if分支中描述。

∙大多数目标器件(如FPGA和CPLD)和ASIC库的触发器都包含异步复位端口,异步复位会被直接接到触发器的异步复位端口,如图所示:上时钟偏斜延时,才能保证同步复位可靠、彻底。

如图所示,假设同步复位逻辑树组合逻辑的延时为t1,复位信号传播路径的最大延时为t2,最慢时钟的周期为Period_max,时钟的skew为Clk2-Clk1,则同步复位的周期Tsyn_rst应该满足如下公式:Tsyn_rst > Period_max + (Clk2 –Clk1) + t1+ t2推荐的复位电路设计方式是异步复位、同步释放。

如何区分同步复位和异步复位?

问:如何区分同步复位和异步复位?可以理解为同步复位是作用于状态,然后通过状态来驱动电路复位的吗(这样理解的话,复位键作为激励拉高到响应拉高,是不是最少要2拍啊)?

以上问题可以理解为:1. 何时采用同步复位,何时采用异步复位;2. 复位电路是用来干嘛的;3. 激励和响应的分析(单拍潜伏期)是否适用与复位逻辑。

1. 电路中,何时采用同步或异步,取决与设计者,取决于当前设计电路的需要。

一般而言:高速逻辑应该采用同步复位,低速逻辑可以采用异步复位;涉及人机交互的复位,适合异步复位;涉及机器之间的握手交互,应该采用同步;涉及到全局作用域的复位信号,作用于高速逻辑时,应该采用同步复位,作用于低速逻辑时,应该采用异步复位。

FPGA设计异步复位同步释放有讲究异步复位同步释放首先要说一下同步复位与异步复位的区别。

同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。

异步复位的好处是速度快。

再来谈一下为什么FPGA 设计中要用异步复位同步释放。

复位信号的释放是有讲究的:我们知道,DFF 的D 端和clk 端之间时序关系是有约束的,这种约束我们通过setup time 和hold time 来check。

即D 端的data 跳变的时刻要与clk 端的时钟上升沿(或者下降沿)跳变要错开,如果这两个跳变撞到一起,我们无法保证DFF 能够sample 到正确的data,这时候不满足setup/hold time 要求,就会发生亚稳态,我们sample 到的data 可能是不稳定的中间态的值,并不是我们原本想要的data。

与此类似,异步复位端与clk 端之间也存在着类似的时序约束关系,为了准确稳定地sample 到异步复位端的reset 信号,我们要求reset 信号在clk 上升沿(或者下降沿)跳变的前后一段时间内保持稳定,不要跳变。

clk 跳变沿之前必须保持稳定的最短时间叫做recovery time,clk 跳变沿之后需要保持稳定的最短时间叫做removal time。

如果在此时间窗口内reset 信号发生跳变,不确定reset 到底有没有释放成功(类似setup+hold 时间窗口内,data 跳变,发生亚稳态,sample 到的值是不稳定的中间态值)。

在IC 设计过程中我们是会check recovery 和removal time 的,如果不满足,我们会通过布局布线的调整(后端的调整)让电路满足这个条件(实质就是让reset 跳变沿和clk 跳变沿错开);但是对于FPGA设计而言,我们一般不采用异步释放的方法,因为FPGA 的布局布线可以调整。

IC设计中同步复位与异步复位的区别异步复位是不受时钟影响的,在一个芯片系统初始化(或者说上电)的时候需要这么一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。

而同步复位需要在时钟沿来临的时候才会对整个系统进行复位。

请注意,如果芯片是有多个时钟的系统,那么如何保证不同时钟域的电路能够“同时”复位将会是一个重要的问题,此外,如果你的时钟是一个低频时钟,那么在这个系统(包括其他芯片)上电时如何保证能和其他芯片同时复位?硬件全局异步复位是必要的,请注意这里加上了“全局”,这是因为异步复位既然要对整个芯片“同时”复位,那么布线延时绝不能不考虑,使用FPGA设计时芯片的异步复位必须要走全局网络。

再提醒一点,芯片中最好不要出现多个异步复位。

一个关键原因是对于FPGA而言,多个异步复位信号难以实现前面要求的“全局网络”。

异步复位最大的优点是, 数据通路就可以不依赖于时钟而确保清洁可控。

然而, 异步复位也有其固有的缺陷。

异步复位设计的DFT (可测性设计) 与STA (静态时序分析) 的复杂性要高于同步复位设计; 但异步复位中最严重的问题是, 如果异步复位信号在触发器时钟有效沿附近“释放”(复位信号从有效变为无效) 的话, 可能会导致触发器输出的亚稳态。

同步复位和异步复位的比较(转载)无论同步还是异步复位,在对触发器时序进行分析的时候,都要考虑复位端与时钟的相位关系。

对于同步复位,复位信号可以理解为一个普通的数据信号,它只有在时钟的跳变沿才会其作用,一般只要复位信号持续时间大于一个时钟周期,就可以保证正确复位。

对于异步复位,复位可以在任何时候发生,表面上看跟时钟没有关系,但真实情况是异步复位也需考虑时钟跳变沿,因为时钟沿变化和异步复位都可以引起Q端数据变化,如果异步复位信号跟时钟在一定时间间隔内发生变化,Q值将无法确定,即亚稳态现象。

这个时候既是异步复位信号持续时间再长都没有办法,因为不定态已经传递下去。

Verilog 复位赋值详解

Verilog是一种硬件描述语言,用于描述数字电路和系统。

在Verilog中,复位是一个重要的概念,它用于将电路或模块的状态初始化为特定的值。

复位通常在系统启动时或出现异常情况时使用。

在Verilog中,有两种常见的复位方式:异步复位和同步复位。

1.异步复位

异步复位是一种立即生效的复位方式,它不需要时钟信号的配合。

当异步复位信号为高电平时,电路或模块的状态将被立即清零或置为特定的初始值。

异步复位通常用于一些不需要时钟的简单电路或模块。

例如,以下代码实现了一个简单的异步复位逻辑:

在这个例子中,reset是异步复位信号,当它为高电平时,counter_reg将被清零。

2.同步复位

同步复位是一种需要时钟信号配合的复位方式。

当同步复位信号为高电平时,电路或模块的状态将被清零或置为特定的初始值。

只有在时钟信号的上升沿到来时,同步复位才会生效。

同步复位通常用于一些需要时钟的复杂电路或模块。

例如,以下代码实现了一个简单的同步复位逻辑:

在这个例子中,reset是同步复位信号,当它为高电平时,count将被清零。

只有在时钟信号的上升沿到来时,count才会被清零。

需要注意的是,在实现复位逻辑时,应该考虑一些特殊情况,例如异步复位的延迟和同步复位的时序要求。

此外,还应该注意复位的稳定性和可靠性,以确保系统能够正常工作。

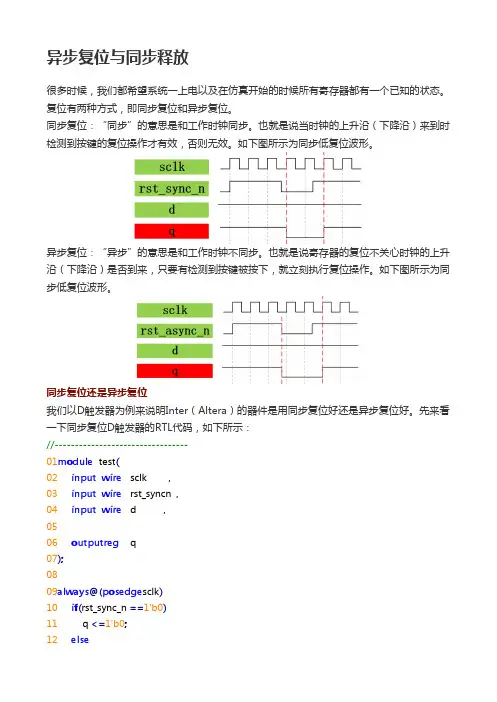

异步复位与同步释放很多时候,我们都希望系统一上电以及在仿真开始的时候所有寄存器都有一个已知的状态。

复位有两种方式,即同步复位和异步复位。

同步复位:“同步”的意思是和工作时钟同步。

也就是说当时钟的上升沿(下降沿)来到时检测到按键的复位操作才有效,否则无效。

如下图所示为同步低复位波形。

异步复位:“异步”的意思是和工作时钟不同步。

也就是说寄存器的复位不关心时钟的上升沿(下降沿)是否到来,只要有检测到按键被按下,就立刻执行复位操作。

如下图所示为同步低复位波形。

同步复位还是异步复位我们以D触发器为例来说明Inter(Altera)的器件是用同步复位好还是异步复位好。

先来看一下同步复位D触发器的RTL代码,如下所示://---------------------------------01module test(02 input wire sclk ,03 input wire rst_syncn ,04 input wire d ,0506 outputreg q07);0809always@(posedge sclk)10 if(rst_sync_n ==1'b0)11 q <=1'b0;12 else13 q <= d;1415endmodule//--------------------------------在Quartus工具中编写完RTL后点击“Start Analysis & Synthesis”图标进行分析和综合。

然后双击“Netlist Viewers”下的“RTL Viewer”查看RTL视图。

如下图所示,可以看到一个 D触发器的结构,也可以称为寄存器,但是还附加了一个选择器,用于同步复位的控制。

点击“Start Compilation”图标全编译进行布局布线,完成后我们可以看到“Flow Summary”资源使用量,如下图所示,可以看到使用了LE中的一个组合逻辑资源和一个时序逻辑资源。

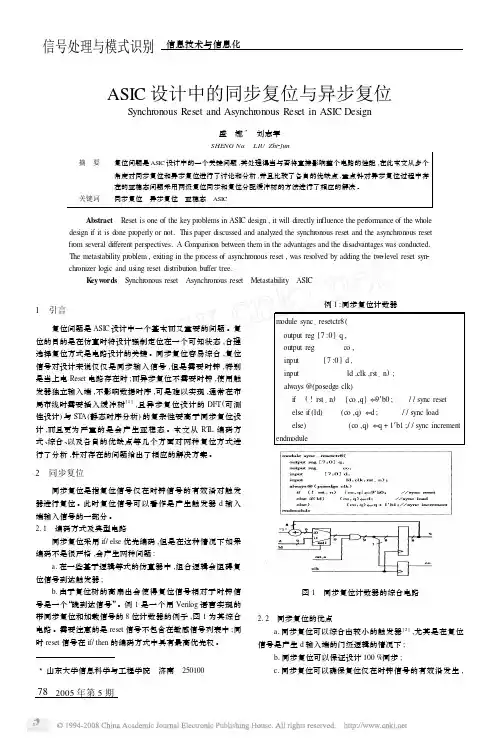

ASIC 设计中的同步复位与异步复位Synchronous Reset and Asynchronous Reset in ASIC Design盛 娜3 刘志军SHENG Na LIU Zhi 2jun摘 要 复位问题是ASIC 设计中的一个关键问题,其处理得当与否将直接影响整个电路的性能,在此本文从多个角度对同步复位和异步复位进行了讨论和分析,并且比较了各自的优缺点,重点针对异步复位过程中存在的亚稳态问题采用两级复位同步和复位分配缓冲树的方法进行了相应的解决。

关键词 同步复位 异步复位 亚稳态 ASIC Abstract Reset is one of the key problems in ASIC design ,it will directly in fluence the performance of the whole design if it is done properly or not.This paper discussed and analyzed the synchronous reset and the asynchronous reset from several different perspectives.A C omparis on between them in the advantages and the disadvantages was conducted.The metastability problem ,exiting in the process of asynchronous reset ,was res olved by adding the tw o 2level reset syn 2chronizer logic and using reset distribution bu ffer tree.K eyw ords Synchronous reset Asynchronous reset Metastability ASIC3山东大学信息科学与工程学院 济南 2501001 引言复位问题是ASIC 设计中一个基本而又重要的问题。

verilog异步复位同步释放电路

摘要:

一、异步复位和同步释放的概念

二、异步复位同步释放电路的实现

三、异步复位同步释放电路的应用

正文:

一、异步复位和同步释放的概念

异步复位是指在电路设计中,复位信号不受时钟信号的影响,只要是复位信号有效,就可以进行复位操作。

而同步释放则是指在复位信号撤销(释放)的时候,必须跟时钟信号同步,也就是说正好跟时钟同沿。

二、异步复位同步释放电路的实现

在Verilog 中,可以通过使用

always@(posedge,clk,or,negedge,resetn) 这样的代码来实现异步复位同步释放电路。

always@表示在时钟上升沿或复位信号下降沿时,对应的代码块会被执行。

通过这样的方式,可以在时钟上升沿时检测到复位信号是否有效,从而实现异步复位的功能。

三、异步复位同步释放电路的应用

异步复位同步释放电路在实际的应用中,可以用于控制FPGA 或ASIC 等集成电路的复位操作。

通过异步复位同步释放电路,可以实现在系统启动时进行复位操作,以保证系统的稳定运行。

同步复位与异步复位的区别

假设电路都是低电平复位

1、同步复位:

复位的有效条件与clk的上升沿有关,当clk的上升沿采到rst_n为低的时候可复位。

代码如下图所⽰:

仿真波形如下图所⽰:

解释:复位信号拉低后,当时钟信号上升沿到来时,输出信号才复位。

2、异步复位

复位的触发条件不仅与clk的上升沿有关,还与rst_n的下降沿有关,当clk上升沿采到rst_n为低时可复位,同时当遇到rst_n下降沿时也进⾏复位。

代码如下图所⽰:

仿真波形如下图所⽰:

解释:当clk上升沿采到rst_n为低时可复位,同时当遇到rst_n下降沿时也可进⾏复位。

3、补充:

always敏感列表中的 or 可以改成半⾓逗号(,)。

异步复位时,若使⽤复位的下降沿,则第⼀个if条件必须写成复位为0,若使⽤复位的上升沿,则第⼀个 if条件必须写成复位为1。

IC设计中同步复位与异步复位的区别

异步复位是不受时钟影响的,在一个芯片系统初始化(或者说上电)的时候需要这么一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。

而同步复位需要在时钟沿来临的时候才会对整个系统进行复位。

请注意,如果芯片是有多个时钟的系统,那么如何保证不同时钟域的电路能够“同时”复位将会是一个重要的问题,此外,如果你的时钟是一个低频时钟,那么在这个系统(包括其他芯片)上电时如何保证能和其他芯片同时复位?硬件全局异步复位是必要的,请注意这里加上了“全局”,这是因为异步复位既然要对整个芯片“同时”复位,那么布线延时绝不能不考虑,使用FPGA设计时芯片的异步复位必须要走全局网络。

再提醒一点,芯片中最好不要出现多个异步复位。

一个关键原因是对于FPGA而言,多个异步复位信号难以实现前面要求的“全局网络”。

异步复位最大的优点是, 数据通路就可以不依赖于时钟而确保清洁可控。

然而, 异步复位也有其固有的缺陷。

异步复位设计的DFT (可测性设计) 与STA (静态时序分析) 的复杂性要高于同步复位设计; 但异步复位中最严重的问题是, 如果异步复位信号在触发器时钟有效沿附近“释放”(复位信号从有效变为无效) 的话, 可能会导致触发器输出的亚稳态。

异步复位同步释放的电路

异步复位和同步释放是电路设计中常用的两种重要技术。

异步复位是指通过一个信号将电路的状态恢复到初始状态,而同步释放则是指在特定条件下,通过一个信号将电路的状态释放。

异步复位是一种非阻塞式的复位方式,它可以在任何时候发生,并立即将电路的状态恢复到初始状态。

当接收到异步复位信号时,电路中的所有存储元件将被置为预定的初始状态。

这种复位方式适用于需要快速响应的电路,比如处理实时数据的电路。

在异步复位电路中,复位信号的触发不依赖于时钟信号,因此可以在任何时刻发生。

这种复位方式的优点是快速响应和简单实现,但也存在一些缺点。

由于复位信号的触发时机不确定,可能会导致电路状态的不确定性,从而引发一些问题,比如数据丢失或错误。

同步释放是一种阻塞式的释放方式,它需要在时钟信号的边沿触发。

当接收到同步释放信号时,电路中的状态将在下一个时钟边沿时被释放。

这种释放方式适用于需要精确控制的电路,比如存储器或计数器。

在同步释放电路中,释放信号的触发依赖于时钟信号,因此释放的时机可以精确控制。

这种释放方式的优点是稳定可靠和精确控制,但也存在一些缺点。

由于释放信号需要等待下一个时钟边沿,可能会引入一定的延迟,从而影响电路的响应速度。

异步复位和同步释放是电路设计中常用的两种重要技术。

根据实际需求,可以选择适合的复位方式来设计电路,以确保电路的稳定性和可靠性。

在实际应用中,可以根据具体情况进行选择,并结合其他技术手段来实现更复杂的功能。

fpga中同步复位和异步复位的区别下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!FPGA中同步复位和异步复位的区别在FPGA设计中,复位是一个至关重要的概念,它确保了系统在启动时处于可控状态。

fpga复位方法总结

FPGA(现场可编程门阵列)的复位方法主要包括同步复位、异步复位以及同步复位异步释放。

1. 同步复位:在时钟上升沿或下降沿时,根据复位信号的状态确定是否对系统进行复位。

这种复位方式需要时钟信号的控制,在时钟信号的上升沿或下降沿时检查复位信号的状态。

如果复位信号有效,则将系统复位。

2. 异步复位:无论时钟信号处于何种状态,只要复位信号有效,就对系统进行复位。

这种复位方式简单直接,只要检测到复位信号的上升沿,就会把输出置为复位值。

但异步复位释放可能导致的问题是时序违规和亚稳态,即电路可能处于一个不稳定的中间状态。

3. 同步复位异步释放:这是一种FPGA设计方法,通常用于确保电路在重新启动后能够正常工作。

在异步复位同步释放的设计中,一组异步复位信号用于重置电路的状态,而另一组同步释放信号则用于释放电路的状态。

这种设计方法是为了保证电路的可靠性和可重复性。

以上信息仅供参考,如有需要,建议咨询专业技术人员。

同步复位与异步复位-异步复位和同步复位区别-异步复位同步释放

学习笔记2009-01-05 11:23:06 阅读107 评论0字号:大中小订阅

一、同步复位与异步复位特点:

同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。

否则,无法完成对系统的复位工作。

异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

二、异步复位和同步复位的优缺点:

1、同步复位的优点大概有3条:

a、有利于仿真器的仿真。

b、可以使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高。

c、因为他只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺。

同步复位的缺点:

a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。

同时还要考虑,诸如:组合逻辑路径延时,复位延时等因素。

b、由于大多数的逻辑器件的目标库内的DFF都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。

2、异步复位的优点也有三条:

a、大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源。

b、设计相对简单。

c、异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。

异步复位的缺点:

a、在复位信号释放(release)的时候容易出现问题。

具体就是说:倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致亚稳态。

解释一下亚稳态产生的原因:在同步系统中,如果触发器的setup time / hold time 不满足,就可能产生亚稳态,此时触发器输出端Q 在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q 端会出现毛刺、振荡、或固定在某一电压值,而不一定等于数据输入端D 的值。

这段之间称为决断时间(resolution time)。

经过resolution time 之后Q端将稳定到0 或1上,但是究竟是0 还是1,这是随机的,与输入没有必然的关系。

亚稳态实质是介于”0””1”电平之间的一个状态。

亚稳态是FF的一个固有特性。

正常采样也会有一个亚稳态时间。

当建立保持时间满足时,FF 在经历采样、亚稳态后,进入一个正确的状态。

如果建立保持时间不满足,那么FF会有一个相当长的亚稳态时间,最后随机进入一个固定态。

也就是会经历一个很长的resolution time然后,在D输出端上随机出现0或1。

亚稳态的危害:

由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出0~1 之间的中间电压值还会使下一级产生亚稳态,即导致meta stability的传播。

逻辑误判(由于组合逻辑的race,导致总线状态的不稳定)有可能通过电路的特殊设计减轻危害(如异步FIFO中Gray码计数器的作用,一次只变化一位),而亚稳态的传播则扩大了故障面,难以处理。

b、复位信号容易受到毛刺的影响。

所以,一般都推荐使用异步复位同步释放的方式,而且复位信号低电平有效。

这样就可以两全其美了。

所谓异步复位同步释放,也就是在Reset信号为低时,马上复位所有信号,而Reset信号由低到高释放时,为了防止出现亚稳态现象,而将Reset信号用D触发器向后延一周期,这样达到两全齐美的结果。

亚稳态的简单解决办法

只要系统中有异步元件,亚稳态就是无法避免的,因此设计的电路首先要减少亚稳态导致错误的发生,其次要使系统对产生的错误不敏感。

前者要靠同步来实现,而后者根据不同的设计应用有不同的处理办法。

用同步来减少亚稳态发生机会的典型电路如图1 所示。

图1 两级同步化电路

在图1 中,左边为异步输入端,经过两级触发器同步,在右边的输出将是同步的,而且该输出基本不存在亚稳态。

其原理是即使第一个触发器的输出端存在亚稳态,经过一个CLK 周期后,第二个触发器D 端的电平仍未稳定的概率非常小,因此第二个触发器Q 端基本不会产生亚稳态。

注意,这里说的是“基本”,也就是无法“根除”,那么如果第二个触发器Q出现了亚稳态会有什么后果呢?后果的严重程度是由你的设计决定的,如果系统对产生的错误不敏感,那么系统可能正常工作,或者经过短暂的异常之后可以恢复正常工作,例如设计异步FIFO 时使用格雷码计数器当读写地址的指针就是处于这方面的考虑。

如果设计上没有考虑如何降低系统对亚稳态的敏感程度,那么一旦出现亚稳态,系统可能就崩溃了。

Cures for metastability(摘自johnson 所书)

∙用反应更快的Flip-Flop,减少metastability window。

∙如图一,引入由同一时钟驱动的串接DFF。

∙降低采样频率,给DFF 更多的时间避开metastability window(亚稳态时间)。

∙使用边沿变化快速的时钟信号。

亚稳态与系统可靠性

使用同步电路以后,亚稳态仍然有发生的可能,与此相连的是平均故障间隔时间

MTBF(mean time between failure),亚稳态的发生概率与时钟频率无关,但是MTBF与时钟有密切关系。

有文章提供了一个例子,某一系统在20MHz 时钟下工作时,MTBF约为50年,但是时钟频率提高到40MHz 时,MTBF 只有1 分钟!可见降低时钟频率可以大大减小亚稳态导致系统错误的出现,其原因在于,时钟周期如果尽可能的大于resolution time 可减小亚稳态传递到下一级的机会,提高系统的MTBF,如图2 所示。

解释为什么第二个触发器D端的电平仍未稳定的概率非常小:

如果一个时钟周期>resolution time,即:使上一级寄存器有足够的时间摆脱亚稳态(满足了建立时间要求),但如果上一级DFF 采样错误,那么下级DFF 同样继承这个采样错误值,只是不会出现亚稳态,杜绝了亚稳态的传递。

如果要稳定的正确采样,必须引入高速时钟,

相应Reset信号同步器的VHDL代码如下:

Library ieee;

Use ieee.std_logic_1164.all;

Entity Rst_Synth is

Port(

Clk : in std_logic;

Arst : in std_logic;

Rst_n : out std_logic);

End Rst_Synth;

Architecture RTL of Rst_Synth is

Signal dff : std_logic;

Begin

Process(Arst, Clk)

Begin

If Arst = '0' then

Dff <= '0';

Rst_n <= '0';

Elsif(Clk'event and Clk = '1') then

Dff <= '1';

Rst_n <= Dff;

End if;

End process;

End RTL;

Veirlog代码如下:

//***************************************************** module reset(

input wire sclk,

input wire rst_in, //未处理的复位信号output reg rst_n //处理后的复位信号

);

//******************************************************

//内部寄存器定义

reg rst_Buffer; //处理后的复位信号暂存寄存器//******************************************************

//对复位信号的处理------异步复位,同步释放

//******************************************************

always@(posedge sclk or negedge rst_in)//接收数据

if(!rst_in)

begin

rst_Buffer <= 1'b0;

rst_n <= 1'b0;

end

else

begin

rst_Buffer <= 1'b1;

rst_n <= rst_Buffer;

end

//****************************************************** endmodule

//////////////////////////////////////////////////

/html/EDAjishu/2007/0405/1886.html。