异步复位同步释放

- 格式:doc

- 大小:43.50 KB

- 文档页数:2

针对数字系统的设计,我们经常会遇到复位电路的设计,对初学者来说不知道同步复位与异步复位的区别与联系,今天我对这个问题简要的阐述下,希望对初学者有一定的参考意义,若有不正确的地方愿大家明示。

同步复位原理:同步复位只有在时钟沿到来时复位信号才起作用,则复位信号持续的时间应该超过一个时钟周期才能保证系统复位。

异步复位原理:异步复位只要有复位信号系统马上复位,因此异步复位抗干扰能力差,有些噪声也能使系统复位,因此有时候显得不够稳定,要想设计一个好的复位最好使用异步复位同步释放。

同步复位与异步复位的优劣:异步复位消耗的PFGA逻辑资源相对来说要少些,因此触发器自身带有清零端口不需要额外的门电路,这是其自身的优势,通常在要求不高的情况下直接使用异步复位就OK。

下面我用verilog来演示下同步复位与异步复位。

同步复位的verilog程序如下:module D_FF(//Input portsSYSCLK,RST_B,A,//Output portsB);//========================================= //Input and output declaration//========================================= input SYSCLK;input RST_B;input A;output B;//========================================= //Wire and reg declaration//=========================================wire SYSCLK;wire RST_B;wire A;reg B;//========================================= //Logic//========================================= always@(posedge SYSCLK)beginif(!RST_B)B<=1'b0;elseB<=A;endendmodule综合后的RTL级电路图如下:异步复位的verilog程序如下:module D_FF(//Input portsSYSCLK,RST_B,A,//Output portsB);//========================================= //Input and output declaration//========================================= input SYSCLK;input RST_B;input A;output B;//========================================= //Wire and reg declaration//=========================================wire SYSCLK;wire RST_B;wire A;reg B;//========================================= //Logic//========================================= always@(posedge SYSCLK or negedge RST_B)beginif(!RST_B)B<=1'b0;elseB<=A;endendmodule综合后的RTL级电路图如下:通过比较显然异步复位消耗的逻辑资源要少些,因此通常的设计中都采用异步复位的方式,需要进一步的学习的话,可以再研究下其它的资料。

复位电路异步复位同步释放异步复位和同步释放是数字电路设计中常见的两种复位方式。

复位电路的作用是将电路的各个元件状态恢复到初始状态,以确保电路在启动时的可靠性和正确性。

异步复位是指在电路中引入一个异步信号,当该信号为高电平时,电路内部的各个元件都被强制复位为初始状态。

异步复位信号可以是外部输入信号,例如按键、开关等,也可以是内部产生的信号,例如定时器溢出信号等。

异步复位的优点是简单直接,可以快速将电路恢复到初始状态。

但是,异步复位也存在一些问题,例如在复位信号引入时可能导致冲突和干扰,还可能引起时序问题和电路不稳定等。

同步释放是指在电路中采用同步信号来释放复位状态。

同步信号通常是由时钟信号和其他状态信号共同产生的,只有在满足特定条件时才会触发复位释放。

同步释放可以有效地解决异步复位的问题,使电路在复位时更加稳定可靠。

同步释放的实现通常需要借助于锁存器、触发器等元件,通过时序控制和状态判定来实现复位释放的精确控制。

在实际的电路设计中,异步复位和同步释放常常结合使用,以实现对电路的可靠复位和平稳释放。

例如,可以使用异步复位电路将电路初始化为初始状态,然后通过同步信号来控制复位释放的时机,确保电路在启动时的稳定性。

此外,还可以根据具体的应用场景和需求,灵活选择异步复位或同步释放的方式。

异步复位和同步释放是数字电路设计中常用的复位方式,它们通过引入异步信号和同步信号来实现对电路的复位和释放。

在电路设计中,需要根据具体的需求和应用场景选择合适的复位方式,以确保电路的可靠性和正确性。

同时,还需要注意复位信号的引入时机和释放时机,避免引发冲突、干扰和时序问题。

通过合理设计和优化,可以实现高性能、高可靠性的复位电路,提高电路的工作效率和稳定性。

1、IEEE标准的硬件描述语言是Verilog HDL和VHDL共同点是:能够形式化地抽象表示电路的行为和结构;支持逻辑设计中层次与范围的描述:可借用高级语言的精巧结构来简化电路行为的描述:具有电路仿真与验证机制以保证设计的正确性;支持电路描述由高层到低层的综合转换;硬件描述与实现工艺无关;便于文档管理;易于理解和设计重用。

不同点:Verilog HDL是一种非常容易掌握的硬件描述语言,而VHDL掌握起来就比较困难。

2、把功能经过验证的、可综合的、实现后电路结构总门数在5000门以上的Verilog HDL模型称之为“软核”。

把在某一种现场可编程门阵列(FPGA)器件上实现的、经验证是正确的、总门数在5000门以上电路结构编码文件称为“固核”。

把在某一种专用集成电路工艺的(ASIC)器件上实现的、经验证是正确的、总门数在5000门以上电路结构版图掩膜称为“硬核”。

3、什么叫综合?通过综合产生的是什么?通过综合工具把行为级描述的模块通过逻辑网表自动转化为门级形式的模块叫综合。

综合由EDA工具来完成。

产生的是由与门,或门和非门组成的加法器,比较器等组合逻辑。

产生的模块很容易与某种工艺的基本元件逐一对应起来,再通过布局布线工具自动地转变为某种工具工艺的电路布线结构。

4、仿真可以在几层面上进行?每个层面的仿真有什么意义?分别为:前仿真,逻辑网表仿真,门级仿真和布线后仿真。

前仿真,逻辑网表仿真,门级仿真:可以调试和验证逻辑系统的设计和结构准确与否,并发现问题及时修改。

布线后仿真:分析设计的电路模块的运行是否正常。

5、模块由描述接口和描述逻辑功能两部分组成。

6、端口分为三种:输入口、输出口、输入/输出口。

7、reg型和wire型变量的差别是什么?reg型变量是寄存器型变量,wire型变量是连线型变量。

两者根本性的差别在于reg型变过量有个寄存器来存放变量,这个值只有变量发生改变时才会改变否则保证原来的值不变,wire型变量的值不是确定的值。

FPGA设计异步复位同步释放有讲究异步复位同步释放首先要说一下同步复位与异步复位的区别。

同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。

异步复位的好处是速度快。

再来谈一下为什么FPGA 设计中要用异步复位同步释放。

复位信号的释放是有讲究的:我们知道,DFF 的D 端和clk 端之间时序关系是有约束的,这种约束我们通过setup time 和hold time 来check。

即D 端的data 跳变的时刻要与clk 端的时钟上升沿(或者下降沿)跳变要错开,如果这两个跳变撞到一起,我们无法保证DFF 能够sample 到正确的data,这时候不满足setup/hold time 要求,就会发生亚稳态,我们sample 到的data 可能是不稳定的中间态的值,并不是我们原本想要的data。

与此类似,异步复位端与clk 端之间也存在着类似的时序约束关系,为了准确稳定地sample 到异步复位端的reset 信号,我们要求reset 信号在clk 上升沿(或者下降沿)跳变的前后一段时间内保持稳定,不要跳变。

clk 跳变沿之前必须保持稳定的最短时间叫做recovery time,clk 跳变沿之后需要保持稳定的最短时间叫做removal time。

如果在此时间窗口内reset 信号发生跳变,不确定reset 到底有没有释放成功(类似setup+hold 时间窗口内,data 跳变,发生亚稳态,sample 到的值是不稳定的中间态值)。

在IC 设计过程中我们是会check recovery 和removal time 的,如果不满足,我们会通过布局布线的调整(后端的调整)让电路满足这个条件(实质就是让reset 跳变沿和clk 跳变沿错开);但是对于FPGA设计而言,我们一般不采用异步释放的方法,因为FPGA 的布局布线可以调整。

IC设计中同步复位与异步复位的区别异步复位是不受时钟影响的,在一个芯片系统初始化(或者说上电)的时候需要这么一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。

而同步复位需要在时钟沿来临的时候才会对整个系统进行复位。

请注意,如果芯片是有多个时钟的系统,那么如何保证不同时钟域的电路能够“同时”复位将会是一个重要的问题,此外,如果你的时钟是一个低频时钟,那么在这个系统(包括其他芯片)上电时如何保证能和其他芯片同时复位?硬件全局异步复位是必要的,请注意这里加上了“全局”,这是因为异步复位既然要对整个芯片“同时”复位,那么布线延时绝不能不考虑,使用FPGA设计时芯片的异步复位必须要走全局网络。

再提醒一点,芯片中最好不要出现多个异步复位。

一个关键原因是对于FPGA而言,多个异步复位信号难以实现前面要求的“全局网络”。

异步复位最大的优点是, 数据通路就可以不依赖于时钟而确保清洁可控。

然而, 异步复位也有其固有的缺陷。

异步复位设计的DFT (可测性设计) 与STA (静态时序分析) 的复杂性要高于同步复位设计; 但异步复位中最严重的问题是, 如果异步复位信号在触发器时钟有效沿附近“释放”(复位信号从有效变为无效) 的话, 可能会导致触发器输出的亚稳态。

同步复位和异步复位的比较(转载)无论同步还是异步复位,在对触发器时序进行分析的时候,都要考虑复位端与时钟的相位关系。

对于同步复位,复位信号可以理解为一个普通的数据信号,它只有在时钟的跳变沿才会其作用,一般只要复位信号持续时间大于一个时钟周期,就可以保证正确复位。

对于异步复位,复位可以在任何时候发生,表面上看跟时钟没有关系,但真实情况是异步复位也需考虑时钟跳变沿,因为时钟沿变化和异步复位都可以引起Q端数据变化,如果异步复位信号跟时钟在一定时间间隔内发生变化,Q值将无法确定,即亚稳态现象。

这个时候既是异步复位信号持续时间再长都没有办法,因为不定态已经传递下去。

数字化设计与制造技术面试基本问题有哪些1.描述对芯片设计流程的理解目前主要接触的是前端设计,主要包括规格制定,客户向芯片设计公司提出设计要求;芯片公司根据客户需求进行方案设计和架构实现,划分具体模块;然后就是HDL编码,使用硬件描述原因呢将模块功能使用代码描述实现,也就是将实际的硬件电路通过HDL 语言编写出来,形成RTL级代码;接着就是仿真验证,检验编码设计的正确性,检验的标准是前面设计的规格;逻辑综合,仿真验证通过,进行逻辑综合。

结果是把HDL代码翻译成门级网表netlist,综合后需要再次进行仿真验证;STA静态时序分析,主要再时序上对电路进行验证,检车电路上是否存在建立时间和保持时间的违例;形式验证,这个不是很懂。

后端的就没怎么接触了,验证完之后就开始板调了。

2.谈谈你所了解的低功耗设计的方法和思路在CMOS技术中,动态功耗与门和金属引线的寄生电容充放电有关,在电容中消耗电流的一般方程式I=V*C*F其中I是电流,v是电压,C是电容,F是频率。

在FPGA设计中,电压通常是固定的,只留下电容C和频率f对电流的操纵,电容直接与随时被触发的门的数量以及连接这些门的布线长度有关,频率f直接与时钟频率有关。

为了是输入器件的功耗最小化,最小化驱动输入的信号上升和下降的时间,动态功耗随着电压的平方减弱,但是降低电压对性能有负面的影响。

3.何为同步复位和异步复位,怎么理解同步复位异步释放?与时钟同步的复位就是同步复位,与时钟无关的就是异步复位,在FPGA中的器件有不同的同步或异步器件,设计时根据具体情况具体分析。

所谓异步复位和同步释放,是指复位信号是异步有效的,即复位的发生与clk无关。

后半句“同步释放”是指复位信号的撤除(释放)则与clk相关,即同步的。

异步复位与同步释放很多时候,我们都希望系统一上电以及在仿真开始的时候所有寄存器都有一个已知的状态。

复位有两种方式,即同步复位和异步复位。

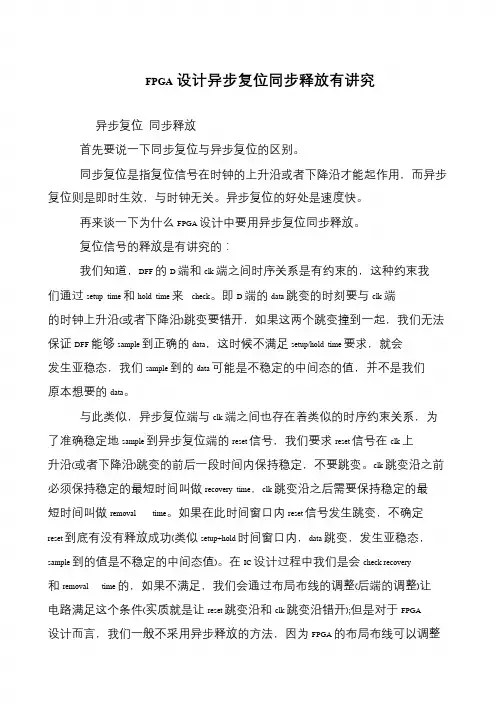

同步复位:“同步”的意思是和工作时钟同步。

也就是说当时钟的上升沿(下降沿)来到时检测到按键的复位操作才有效,否则无效。

如下图所示为同步低复位波形。

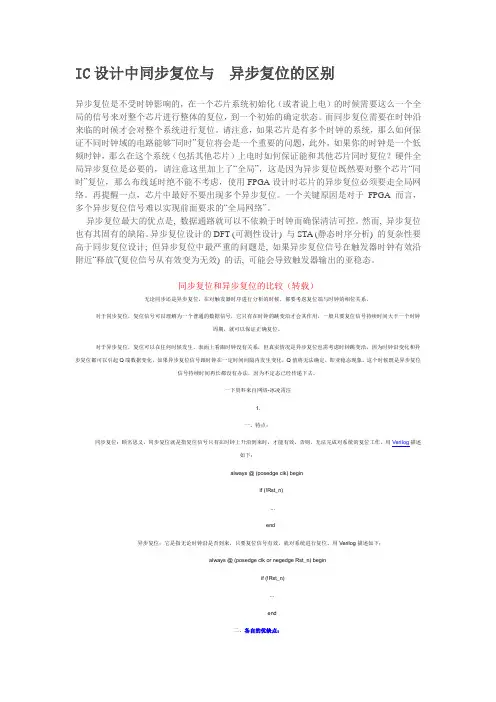

异步复位:“异步”的意思是和工作时钟不同步。

也就是说寄存器的复位不关心时钟的上升沿(下降沿)是否到来,只要有检测到按键被按下,就立刻执行复位操作。

如下图所示为同步低复位波形。

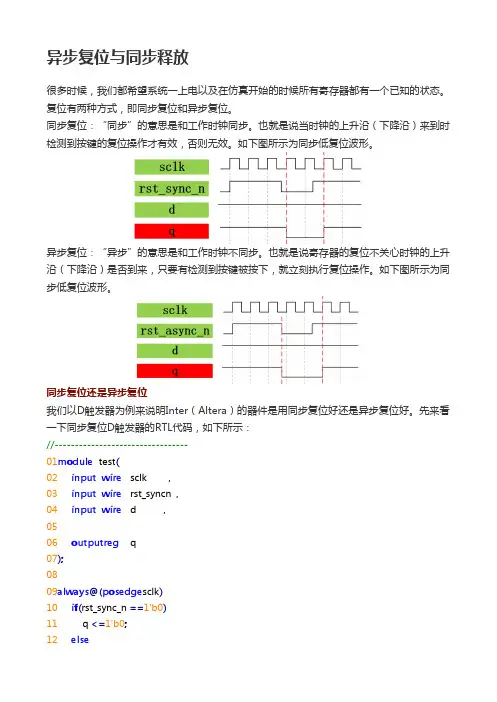

同步复位还是异步复位我们以D触发器为例来说明Inter(Altera)的器件是用同步复位好还是异步复位好。

先来看一下同步复位D触发器的RTL代码,如下所示://---------------------------------01module test(02 input wire sclk ,03 input wire rst_syncn ,04 input wire d ,0506 outputreg q07);0809always@(posedge sclk)10 if(rst_sync_n ==1'b0)11 q <=1'b0;12 else13 q <= d;1415endmodule//--------------------------------在Quartus工具中编写完RTL后点击“Start Analysis & Synthesis”图标进行分析和综合。

然后双击“Netlist Viewers”下的“RTL Viewer”查看RTL视图。

如下图所示,可以看到一个 D触发器的结构,也可以称为寄存器,但是还附加了一个选择器,用于同步复位的控制。

点击“Start Compilation”图标全编译进行布局布线,完成后我们可以看到“Flow Summary”资源使用量,如下图所示,可以看到使用了LE中的一个组合逻辑资源和一个时序逻辑资源。

课题:基于FPGA的洗衣机控制器前言一、洗衣机控制器主要内容l.任务要求和内容设计制作一个洗衣机的正反转定时控制线路。

1)控制洗衣机的电机作如下运转定时开始――正转10S――暂停5S――反转10S――暂停5S――定时到停止定时未到2)用2位七段数码管显示定时时间(S)。

2.洗衣机控制器的使用步骤:(1)电路上电后,在Start拨码开关未闭合前可以由UpKey和DownKey按键开关“+”“-”设置总的工作时间,确定洗衣机控制器工作允许时间。

(2)设定好允许工作时间后,闭合Start开关,洗衣机控制器开始工作。

(3)可以看见指示正转LED灯亮10s,停转LED灯亮5S,反转LED灯亮10s,停转LED亮5s,如此反复直至工作允许时间为0,蜂鸣器发出警报。

二、设计原理简介洗衣机控制器的设计主要是时序控制和定时器的设计,由一片FPGA和外围电路构成电器控制部分。

FPGA接收键盘的控制命令,控制洗衣机的正转、反转、停机和定时时间为0报警的工作状态、控制并显示工作状态以及显示定时时间。

对FPGA芯片的编程采用模块化的Verilog HDL (硬件描述语言)进行设计,设计由分频模块,按键消抖模块,定时时间自减模块,时序中心控制模块,数码管显示模块组成,顶层实现整个芯片的功能。

顶层使用原理图实现,底层由Verilog HDL语句实现。

FPGA的输入时钟为20M hz,因此使用了分频模块输出1hz的方波给定时器设定自减模块提供每1s自减1的信号,定时器模块输出的自减值输入给数码管显示译码模块和时序控制模块,通过译码模块定时器的值可以在数码管上显示,同时定时器的值输入到时序控制模块由此可以控制洗衣机的正转、反转、停机和报警工作方式。

通过按键消抖模块可以准确无抖动的设定定时器的工作时间。

目录一、前言 (2)二、目录 (3)三、正文 (4)3.1洗衣机控制器的整体框图及原理 (4)3.2洗衣机控制电路单元模块设计和仿真 (5)3.2.1按键消抖模块的设计 (5)3.2.2时钟分频模块的设计 (6)3.2.3定时器设定和自减模块的设计 (7)3.2.4时序中心控制模块的设计 (8)3.2.5数码管显示译码模块的设计 (9)四、电路调试 (11)五、结束语和心得体会 (12)六、参考文献 (13)七、附录 (13)7.1 FPGA系统板部分原理图 (13)7.2 FPGA系统板PCB图 (15)三、正文3.1 洗衣机控制器的整体框图及原理:基于fpga的洗衣机控制器电路主要由五大模块组成,分别为按键消抖模块,时钟分频模块,定时器设定和自减模块,时序中心控制模块,数码管显示译码模块。

fpga逻辑题目001——同步复位与异步复位的区别FPGA逻辑题目001主要探讨了同步复位与异步复位的区别,以下是对这个问题的详细分析:1. 同步复位与异步复位的基本概念:同步复位是指系统在时钟沿变化时,当复位信号满足复位条件,系统将完成复位动作。

异步复位是指时钟复位信号不依赖于时钟,只要满足复位条件,系统就会完成复位动作。

2. 同步复位的优缺点:有利于基于周期的仿真工具的仿真。

有利于静态时序分析工具的分析,可以综合出较高的工作频率。

抗干扰能力高,可以剔除复位信号中高于时钟频率的毛刺。

缺点是复位依赖于时钟信号,如果时钟信号出现故障,系统将无法正常复位。

此外,由于多数逻辑器件的目标库内的D触发器只有异步复位端口,所以综合器在综合同步复位时将在寄存器的输入端口插入组合逻辑,这会占用更多内部逻辑资源,并可能导致逻辑门时延较高。

此外,复位信号的有效脉冲宽度必须大于时钟周期,因为线路的时钟延时和路径延时可能导致需要多个时钟周期的复位脉冲宽度,并且不能保证复位信号到达各个寄存器的时序。

3. 异步复位的优缺点:优点是复位信号不依赖于时钟信号,电路在任何情况下都能实现复位,节约内部逻辑资源,设计实现简单。

由于多数逻辑器件的目标库内的D触发器都有异步复位端口,所以复位端口不需要设计额外的逻辑资源。

缺点是复位信号对电路内的毛刺敏感,容易受到外界的干扰,出现频繁复位现象。

此外,由于异步释放的随机性可能导致时序违规,当复位信号释放在时钟有效沿附近时,触发器输出可能处于亚稳态,导致复位操作失败。

此外,异步复位不利于静态时序分析工具的分析,如果复位信号不是直接来自于I/O引脚,在DFT(Design ForTest)扫描和测试时,复位信号必须被禁止,因此需要添加额外的同步电路。

4. “异步复位、同步释放”的方式:这是一种常用的复位设计方式。

其优点在于保证复位信号采集的可靠性(因为复位信号的到来与时钟信号无关),并且防止了在时钟有效沿附近释放复位信号时可能产生的亚稳态。

异步复位同步撤离方法1. 引言在计算机科学领域,异步复位和同步撤离是两种重要的方法,用于处理并发和多线程编程中的同步问题。

本文将详细介绍这两种方法的概念、原理和应用,并探讨它们在实际开发中的优缺点。

2. 异步复位异步复位是一种处理并发问题的方法,它通过在某个条件满足时触发复位操作,来实现线程的同步。

在多线程编程中,常常会遇到需要等待某个线程完成某个操作后再继续执行的情况。

异步复位可以用于解决这类问题。

2.1 原理异步复位的原理是通过信号量或事件来实现的。

当某个条件满足时,触发复位操作,将信号量或事件复位为初始状态。

其他线程在等待信号量或事件时,会被阻塞,直到复位操作完成。

2.2 应用场景异步复位常用于多线程编程中的同步问题。

例如,在生产者-消费者模型中,生产者线程生产数据并通知消费者线程消费,消费者线程消费完数据后需要通知生产者线程继续生产。

这时可以使用异步复位来实现线程间的同步。

3. 同步撤离同步撤离是一种处理并发问题的方法,它通过将某个操作从同步模式转变为异步模式来提高程序的性能和可伸缩性。

同步撤离可以用于解决并发性能瓶颈和资源争用的问题。

3.1 原理同步撤离的原理是将原本需要同步执行的操作,拆分为多个阶段,并将其中的一些阶段转变为异步执行。

这样可以减少对共享资源的争用,提高并发性能。

3.2 应用场景同步撤离常用于并发性能优化中。

例如,在一个多线程的Web服务器中,每个请求都需要从数据库中获取数据并返回给客户端。

如果每个请求都需要等待数据库操作完成后才能继续执行,那么服务器的并发性能将受到限制。

这时可以使用同步撤离来将数据库查询操作转变为异步执行,从而提高服务器的并发性能。

4. 异步复位与同步撤离的比较异步复位和同步撤离都是处理并发问题的方法,但它们的应用场景和原理有所不同。

下面对它们进行比较:4.1 应用场景•异步复位适用于需要等待某个条件满足后才能继续执行的场景,常用于多线程编程中的同步问题。

异步复位同步释放电路结构异步复位同步释放电路是一种常见的数字电路设计,主要用于将异步复位信号转换为同步释放信号。

以下从六个方面详细介绍了异步复位同步释放电路的结构。

异步复位信号生成异步复位信号是指一个高电平或低电平的信号,用于将电路中的所有寄存器或其他逻辑电路复位到初始状态。

异步复位信号的产生通常由外部输入或内部时钟信号经过一定的逻辑门组合产生。

同步释放信号生成同步释放信号是指与时钟信号同步的释放信号,用于在时钟上升沿或下降沿释放寄存器或其他逻辑电路。

同步释放信号的产生通常通过在时钟信号上添加一定的延时来实现,以确保在时钟信号的稳定期间产生释放信号。

电路模块连接方式异步复位同步释放电路通常包括多个电路模块,如寄存器、触发器等。

这些模块之间的连接方式取决于具体的设计需求。

通常,异步复位信号和同步释放信号会连接到各个模块的相应输入端,以确保正确地复位和释放各个模块。

触发器设计触发器是异步复位同步释放电路中的重要组成部分,用于在接收到异步复位信号或同步释放信号时,将电路的状态重置到初始状态或释放到下一个状态。

触发器的设计通常需要考虑其灵敏度、功耗和延迟等因素。

时序控制异步复位同步释放电路的时序控制包括复位和释放信号的时间控制以及电路状态转换的控制。

时序控制通常需要考虑时钟信号的频率和相位、复位和释放信号的延时等因素,以确保电路在正确的时间点进行复位和释放操作。

抗异常设计抗异常设计是异步复位同步释放电路中的一项重要技术,主要用于防止电路在异常情况下发生错误动作。

抗异常设计包括对电源电压波动、噪声干扰等异常情况的抵抗能力。

对于电源电压波动,可以通过增加滤波电容等元件来降低其影响;对于噪声干扰,可以通过增加屏蔽措施、优化布线等方式来降低其影响。

功耗优化功耗优化是异步复位同步释放电路中的一项重要技术,主要用于降低电路的功耗。

功耗优化可以通过优化电路结构、使用低功耗元件等方式来实现。

例如,在不影响电路性能的前提下,可以使用低功耗的逻辑门替换高功耗的逻辑门;在适当的情况下,可以使用待机模式或休眠模式来降低电路的功耗。

一、LAB内部资源Cyclone III 每个LAB包括16个LE ,每个LAB 还包括LAB control signals、LE carry chains、Register chains、Local interconnect,需要对LAB control signals 有所了解。

每个LAB 的LAB control signals 包括Two Clocks、Two clock enables、Two asynchronous clears、One synchronous clear、one synchronous load,这些信号都是LAB-wide 作用的。

LAB-wide: 比如某个LE的register 使用的时钟是clk1,那么这个clk1 的作用域是整个LAB,此LAB 内任何一个register都连接了此clk1,或者说clk1走的是LAB内的时钟网络,注意,虽然作用域是整个LAB,但是任意某个LE 可以选择不用此时钟。

这就像,家里的水龙头,整栋楼使用的是同一个供水管道(作用域:整栋楼),但是对于各家各户,提供给你们家的只是一个水龙头(接口),你可以选择打开或者不用。

对于Cyclone III 每个LAB 有Two clocks ,这就是说这个楼有两个供水管道,每户人家可以选择打开水龙头A 或者水龙头B ,或者不用水。

但是,想打开水龙头C ,对不起,这栋楼只有两个供水管道(假设每个管道只提供给各户一个接口)。

有了上边的概念,一切就简单了。

Two clocks :两个时钟域的不同LEs,可以位于同一个LAB模块内,但是三个时钟域的不同LEs,绝对不同位于同一个LAB中,编译时,布局布线时,编译器会自动把这些LEs分配到不同的LAB内,如果通过Chip Planner ECO 改动不同时钟域(三个以上)的LEs 到同一个LAB 编译时会报错;One synchronous clear :同一个LAB 只有一个同步复位线,不同同步复位的LEs 不能位于一个LAB 内!其它LAB内控制信号亦如此!二、谈一谈复位的问题1、在assignment -setting -Device and Pins -General 中Enable device-wide reset(DEV_CLRn) ,打勾,使能全局清零管脚,不打勾,这个脚就是普通IO 脚,这个脚只能chip-wide 寄存器清零,不能置 1 ,一般不用此脚当复位脚!因为复位后有些初值不希望是0 ,而且这个复位脚只能对寄存器清0 ,对组合逻辑无效。

异步复位,同步释放一、特点:同步复位:顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。

否则,无法完成对系统的复位工作。

用Verilog描述如下:always @ (posedge clk beginif (!Rst_n...end异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

用Verilog描述如下:always @ (posedge clk or negedge Rst_n beginif (!Rst_n...end二、各自的优缺点:1、总的来说,同步复位的优点大概有3条:a、有利于仿真器的仿真。

b、可以使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高。

c、因为他只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺。

他的缺点也有不少,主要有以下几条:a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。

同时还要考虑,诸如:clk skew,组合逻辑路径延时,复位延时等因素。

b、由于大多数的逻辑器件的目标库内的DFF都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。

2、对于异步复位来说,他的优点也有三条,都是相对应的a、大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源。

b、设计相对简单。

c、异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。

缺点:a、在复位信号释放(release的时候容易出现问题。

具体就是说:倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致亚稳态。

b、复位信号容易受到毛刺的影响。

三、总结:所以说,一般都推荐使用异步复位,同步释放的方式,而且复位信号低电平有效。

这样就可以两全其美了。

2:推荐的复位方式所谓推荐的复位方式就是上文中所说的:“异步复位,同步释放”。

异步复位同步释放的电路

异步复位和同步释放是电路设计中常用的两种重要技术。

异步复位是指通过一个信号将电路的状态恢复到初始状态,而同步释放则是指在特定条件下,通过一个信号将电路的状态释放。

异步复位是一种非阻塞式的复位方式,它可以在任何时候发生,并立即将电路的状态恢复到初始状态。

当接收到异步复位信号时,电路中的所有存储元件将被置为预定的初始状态。

这种复位方式适用于需要快速响应的电路,比如处理实时数据的电路。

在异步复位电路中,复位信号的触发不依赖于时钟信号,因此可以在任何时刻发生。

这种复位方式的优点是快速响应和简单实现,但也存在一些缺点。

由于复位信号的触发时机不确定,可能会导致电路状态的不确定性,从而引发一些问题,比如数据丢失或错误。

同步释放是一种阻塞式的释放方式,它需要在时钟信号的边沿触发。

当接收到同步释放信号时,电路中的状态将在下一个时钟边沿时被释放。

这种释放方式适用于需要精确控制的电路,比如存储器或计数器。

在同步释放电路中,释放信号的触发依赖于时钟信号,因此释放的时机可以精确控制。

这种释放方式的优点是稳定可靠和精确控制,但也存在一些缺点。

由于释放信号需要等待下一个时钟边沿,可能会引入一定的延迟,从而影响电路的响应速度。

异步复位和同步释放是电路设计中常用的两种重要技术。

根据实际需求,可以选择适合的复位方式来设计电路,以确保电路的稳定性和可靠性。

在实际应用中,可以根据具体情况进行选择,并结合其他技术手段来实现更复杂的功能。