频率综合器

- 格式:pdf

- 大小:1.04 MB

- 文档页数:43

DDS的原理及镜像频谱分析1.目的:(1)了解DDS的原理。

(2)分析DDS的镜像频谱2.DDS的原理2.1.DDS的概述直接数字式频率综合器DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字对系统时钟进行分频以产生所需要的频率。

DDS 有两个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的宽度宽(48bit或者更高),频率分辨率高。

图1是DDS的内部结构图,它主要分成3部分:相位累加器(PHASE_ACCMULATOR),相位幅度转换(AMPLITUDE/SINE_CONV.ALGORITHM),数模转换器(D/A_CONVERTER)图1 DDS的结构框图2.2.DDS的组成1、相位累加器:一个正弦波,它的幅度不是线性的,但是它的相位却是线性增加的。

DDS就是利用了这一特点来产生正弦信号。

如图 2,根据DDS的频率控制字的位数N,把360°平均分成了2N等份。

假设系统时钟为Fc,输出频率为Fout。

每次转动一个角度360°/2N,则可以产生一个频率为Fc/2N的正弦波的相位递增量。

那么只要选择恰当的频率控制字M,使得Fout/Fc= M/2N,就可以得到所需要的输出频率Fout=Fc*M /2N。

图2 相位累加器原理2、相位幅度转换:通过相位累加器,我们已经得到了合成Fout频率所对应的相位信息,然后相位幅度转换器把0°~360°的相位转换成相位相应的幅度值。

比如当DDS选择为2Vp-p的输出时,45°对应的幅度值为 0.707V,这个数值则以二进制的形式被送入DAC。

这个相位到幅度的转换是通过查表完成的。

3、数模转换器:的二进制数字信号被送入DAC中,并转换成为模拟信号输出。

★注意★DAC 的位数并不影响输出频率的分辨率。

频率综合器的结构引言频率综合器是一种电子器件,用于将一个或多个输入信号的频率按照一定的规律合成为一个输出信号的器件。

频率综合器在通信系统、无线电设备、音频设备等领域中具有广泛的应用。

本文将介绍频率综合器的结构及其工作原理。

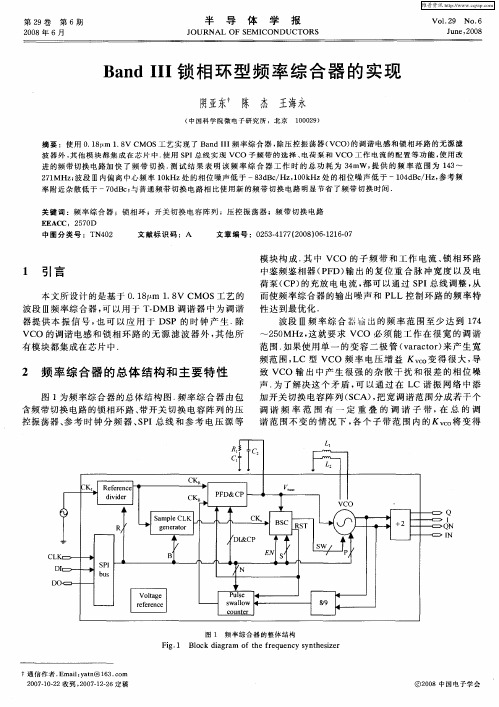

一、频率综合器的基本原理频率综合器的基本原理是利用相位锁定环(Phase-Locked Loop,简称PLL)来实现输入信号频率的合成。

PLL由相位比较器、低通滤波器、可变频率振荡器和分频器组成。

其工作原理如下: 1. 输入信号与可变频率振荡器产生的信号经相位比较器进行相位对比。

2. 相位比较器的输出经低通滤波器进行滤波,得到控制电压。

3. 控制电压作用于可变频率振荡器,使其输出信号的频率与输入信号的频率相同或相差一个整数倍。

4. 分频器将可变频率振荡器的输出信号进行分频,得到所需的输出频率。

二、频率综合器的结构频率综合器的结构可以分为三个部分:输入模块、PLL模块和输出模块。

2.1 输入模块输入模块用于接收外部的输入信号作为合成频率的参考信号。

输入模块通常包括滤波器、放大器和相位锁定环。

滤波器用于消除输入信号中的干扰,放大器用于增加信号强度,相位锁定环用于提供输入信号与合成信号之间的相位对比。

2.2 PLL模块PLL模块是频率综合器的核心部分,主要由相位比较器、低通滤波器、可变频率振荡器和分频器构成。

2.2.1 相位比较器相位比较器用于比较输入信号的相位与可变频率振荡器输出信号的相位差,产生控制电压。

2.2.2 低通滤波器低通滤波器对相位比较器的输出信号进行滤波,去除高频噪声,得到平滑的控制电压。

2.2.3 可变频率振荡器可变频率振荡器根据控制电压的调节,改变输出信号的频率,以实现输入信号频率的合成。

2.2.4 分频器分频器将可变频率振荡器的输出信号进行分频,得到所需的输出频率。

2.3 输出模块输出模块用于将频率综合器合成的输出信号输出到外部电路。

输出模块通常包括滤波器和放大器,滤波器用于去除合成信号中的高频噪声,放大器用于增加输出信号的幅度。

频率综合器的结构频率综合器是一种能够将一个或多个参考频率组合成一个输出频率的电路。

频率综合器在现代通信系统和雷达系统中广泛应用,是实现高精度、长时间稳定性、多信号频率合成的关键电路之一。

本文将会介绍频率综合器的结构及其原理。

1. 频率综合器的结构频率综合器的结构通常由一个相位锁定环(PLL)和一个可变频率倍频器组成。

相位锁定环(PLL),是一种基于反馈的控制系统,通过对输入信号进行相位比较,并与参考信号相位比较,输出一个控制电压来调整振荡器的频率,从而实现相位同步的电路。

在频率综合器中,PLL用于将参考频率精确地转换成一个稳定的中间频率,并形成一个与参考信号相位关联的合成输出信号。

可变频率倍频器,是一种将输入频率扩大或缩小的电路。

倍频器可以将指定的输入信号频率扩大或缩小,得到所需的输出信号。

可变倍频器能够根据PLL输出的控制电压自动调整倍率。

多级倍频器可以将频率扩大若干倍,并将输出信号根据输入参数锁定到所需的频率。

2. 频率综合器的原理频率综合器的原理是基于PLL和倍频器的相互作用,通过PLL将参考信号转换成中频信号,然后倍频器将中频信号扩大或缩小至所需频率,得到输出信号。

首先,参考信号与相位比较器(phase detector)进行相位比较。

相位比较器将参考信号与合成信号进行比较,并产生一个瞬时比较电压。

该电压与一个滤波器相结合,产生一个转换误差信号。

PLL通过调整振荡器频率,使得该误差信号为0,从而实现一个相位同步的电路。

其次,中频信号通过可变倍频器进行倍频,从而得到所需频率的输出信号。

其中,倍频器输出的波形必须以相位锁定环的锁定频率为参考,否则将会导致锁定失效。

同时,由于倍频器具有较大的增益,因此必须采取同步器或滤波器等措施来减小倍频器的波形畸变和噪声。

3. 应用领域频率综合器应用广泛,主要应用在以下领域:(1)通信系统:在通信系统中,频率综合器用于生成多个频率的合成信号,如高速调制和解调器、软件无线电和卫星通信系统等。