74LS74二分频与四分频电路

- 格式:doc

- 大小:133.00 KB

- 文档页数:2

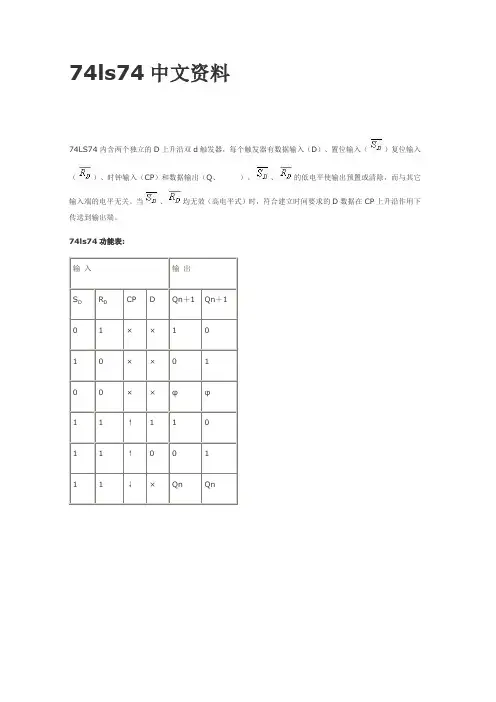

74ls74中文资料74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:输入输出S D R D CP D Qn+1 Qn+10 1 ×× 1 01 0 ××0 10 0 ××φ φ1 1 ↑ 1 1 01 1 ↑0 0 11 1 ↓×Qn Qn图1 74ls74引脚图实验:用74LS74构成4位寄存器一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;(3) 先清零;(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

并入并出:D3D2D1D0=10111个CP脉冲Q3Q2Q1Q0=结论:并入串出D3D2D1D0=10114个CP脉冲Q3=结论串入并出D3=10114个CP脉冲Q3Q2Q1Q0=结论串入串出D3=10118个CP脉冲Q3=结论图274ls153芯片管脚图引脚逻辑功能以及封装2007年12月17日 23:53 本站原创作者:本站用户评论()关键字:74ls153管脚图逻辑功能图封装:74LS163引脚功能表及管脚定义图(带时序波形图)发布:2011-08-30 | 作者: | 来源: huangjiapeng| 查看:2620次 | 用户关注:定时器由与系统秒脉冲(由时钟脉冲产生器提供)同步的计数器构成,要求计数器在状态信号ST作用下,首先清零,然后在时钟脉冲上升沿作用下,计数器从零开始进行增1计数,向控制器提供模5的定时信号TY和模25的定时信号TL。

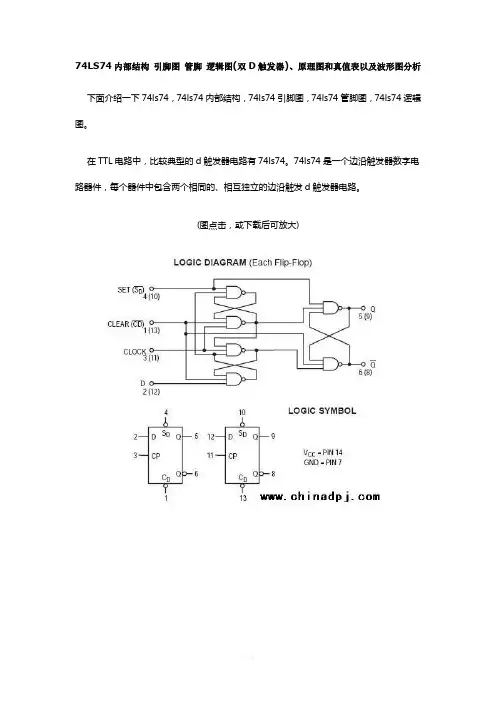

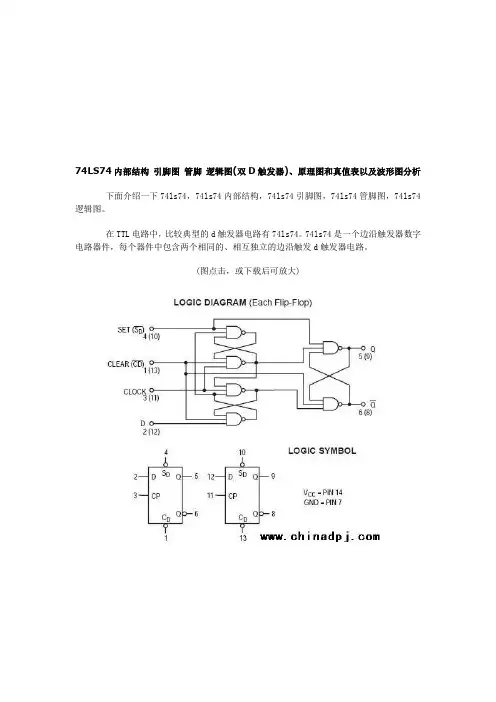

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD =0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6 =Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q =D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q 3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

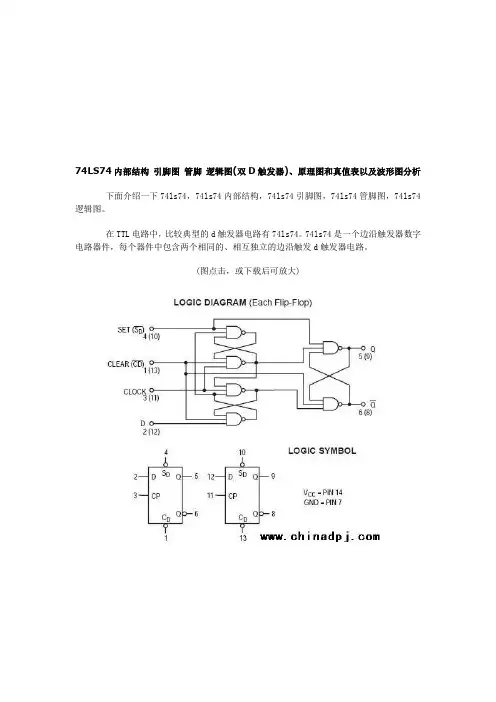

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

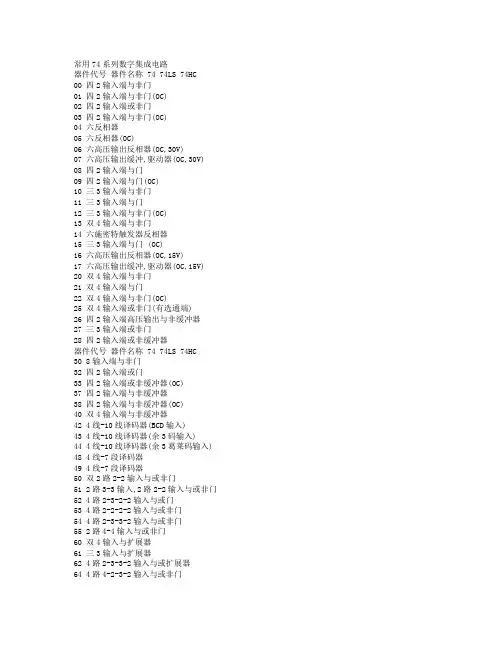

常用74系列数字集成电路器件代号器件名称 74 74LS 74HC00 四2输入端与非门01 四2输入端与非门(OC)02 四2输入端或非门03 四2输入端与非门(OC)04 六反相器05 六反相器(OC)06 六高压输出反相器(OC,30V)07 六高压输出缓冲,驱动器(OC,30V)08 四2输入端与门09 四2输入端与门(OC)10 三3输入端与非门11 三3输入端与门12 三3输入端与非门(OC)13 双4输入端与非门14 六施密特触发器反相器15 三3输入端与门 (OC)16 六高压输出反相器(OC,15V)17 六高压输出缓冲,驱动器(OC,15V)20 双4输入端与非门21 双4输入端与门22 双4输入端与非门(OC)25 双4输入端或非门(有选通端)26 四2输入端高压输出与非缓冲器27 三3输入端或非门28 四2输入端或非缓冲器器件代号器件名称 74 74LS 74HC30 8输入端与非门32 四2输入端或门33 四2输入端或非缓冲器(OC)37 四2输入端与非缓冲器38 四2输入端与非缓冲器(OC)40 双4输入端与非缓冲器42 4线-10线译码器(BCD输入)43 4线-10线译码器(余3码输入)44 4线-10线译码器(余3葛莱码输入)48 4线-7段译码器49 4线-7段译码器50 双2路2-2输入与或非门51 2路3-3输入,2路2-2输入与或非门52 4路2-3-2-2输入与或门53 4路2-2-2-2输入与或非门54 4路2-3-3-2输入与或非门55 2路4-4输入与或非门60 双4输入与扩展器61 三3输入与扩展器62 4路2-3-3-2输入与或扩展器64 4路4-2-3-2输入与或非门65 4路4-2-3-2输入与或非门(OC)70 与门输入J-K触发器71 与或门输入J-K触发器72 与门输入J-K触发器器件代号器件名称 74 74LS 74HC74 双上升沿D型触发器78 双D型触发器85 四位数值比较器86 四2输入端异或门87 4位二进制原码/反码95 4位移位寄存器101 与或门输入J-K触发器102 与门输入J-K触发器107 双主-从J-K触发器108 双主-从J-K触发器109 双主-从J-K触发器110 与门输入J-K触发器111 双主-从J-K触发器112 双下降沿J-K触发器113 双下降沿J-K触发器114 双下降沿J-K触发器116 双4位锁存器120 双脉冲同步驱动器121 单稳态触发器122 可重触发单稳态触发器123 可重触发双稳态触发器125 四总线缓冲器126 四总线缓冲器128 四2输入端或非线驱动器132 四2输入端与非门常用4000系列标准数字电路的中文名称资料型号器件名称厂牌备注CD4000 双3输入端或非门+单非门 TICD4001 四2输入端或非门 HIT/NSC/TI/GOL CD4002 双4输入端或非门 NSCCD4006 18位串入/串出移位寄存器 NSCCD4007 双互补对加反相器 NSCCD4008 4位超前进位全加器 NSCCD4009 六反相缓冲/变换器 NSCCD4010 六同相缓冲/变换器 NSCCD4011 四2输入端与非门 HIT/TICD4012 双4输入端与非门 NSCCD4013 双主-从D型触发器 FSC/NSC/TOS CD4014 8位串入/并入-串出移位寄存器 NSC CD4015 双4位串入/并出移位寄存器 TICD4016 四传输门 FSC/TICD4017 十进制计数/分配器 FSC/TI/MOTCD4018 可预制1/N计数器 NSC/MOTCD4019 四与或选择器 PHICD4020 14级串行二进制计数/分频器 FSCCD4021 08位串入/并入-串出移位寄存器 PHI/NSCCD4022 八进制计数/分配器 NSC/MOT型号器件名称厂牌备注CD4023 三3输入端与非门 NSC/MOT/TICD4024 7级二进制串行计数/分频器 NSC/MOT/TICD4025 三3输入端或非门 NSC/MOT/TICD4026 十进制计数/7段译码器 NSC/MOT/TICD4027 双J-K触发器 NSC/MOT/TICD4028 BCD码十进制译码器 NSC/MOT/TICD4029 可预置可逆计数器 NSC/MOT/TICD4030 四异或门 NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器 NSC/MOT/TICD4032 三串行加法器 NSC/TICD4033 十进制计数/7段译码器 NSC/TICD4034 8位通用总线寄存器 NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存 NSC/MOT/TI CD4038 三串行加法器 NSC/TICD4040 12级二进制串行计数/分频器 NSC/MOT/TICD4041 四同相/反相缓冲器 NSC/MOT/TICD4042 四锁存D型触发器 NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环 NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器 NSC/MOT/TI型号器件名称厂牌备注CD4048 4输入端可扩展多功能门 NSC/HIT/TICD4049 六反相缓冲/变换器 NSC/HIT/TICD4050 六同相缓冲/变换器 NSC/MOT/TICD4051 八选一模拟开关 NSC/MOT/TICD4052 双4选1模拟开关 NSC/MOT/TICD4053 三组二路模拟开关 NSC/MOT/TICD4054 液晶显示驱动器 NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器 NSC/HIT/TICD4056 液晶显示驱动器 NSC/HIT/TICD4059 “N”分频计数器 NSC/TICD4060 14级二进制串行计数/分频器 NSC/TI/MOTCD4063 四位数字比较器 NSC/HIT/TICD4066 四传输门 NSC/TI/MOTCD4067 16选1模拟开关 NSC/TICD4068 八输入端与非门/与门 NSC/HIT/TICD4069 六反相器 NSC/HIT/TICD4070 四异或门 NSC/HIT/TICD4071 四2输入端或门 NSC/TICD4072 双4输入端或门 NSC/TICD4073 三3输入端与门 NSC/TICD4075 三3输入端或门 NSC/TI型号器件名称厂牌备注CD4076 四D寄存器CD4077 四2输入端异或非门 HITCD4078 8输入端或非门/或门CD4081 四2输入端与门 NSC/HIT/TICD4082 双4输入端与门 NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器 NSC/MOT/STCD4094 8位移位存储总线寄存器 NSC/TI/PHICD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器 NSC/MOT/TICD4099 8位可寻址锁存器 NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器型号器件名称厂牌备注CD40106 六施密特触发器反相器 NSC\TICD40107 双2输入端与非缓冲/驱动器 HAR\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动 STCD40147 10-4线编码器 NSC\MOTCD40160 可预置BCD加计数器 NSC\MOTCD40161 可预置4位二进制加计数器 NSC\MOTCD40162 BCD加法计数器 NSC\MOTCD40163 4位二进制同步计数器 NSC\MOTCD40174 六锁存D型触发器 NSC\TI\MOTCD40175 四D型触发器 NSC\TI\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\TI CD40193 可预置4位二进制加/减计数器 NSC\TICD40194 4位并入/串入-并出/串出移位寄存 NSC\MOT CD40195 4位并入/串入-并出/串出移位寄存 NSC\MOT CD40208 4×4多端口寄存器型号器件名称厂牌备注CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐) CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器型号器件名称厂牌备注CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器CD22100 4×4×1交叉点开关。

基本RS锁存器和D触发器-器件实验报告基本RS触发器和D触发器一、实验目的:熟悉几种常见触发器的逻辑功能,准确理解触发器特性描述和正确对其逻辑功能进行测试操作。

熟练使用示波器来观看触发器的时序图。

二、实验内容:1(搭接一个基本RS触发器,对其功能进行测试,填写基本RS触发器特性表。

2(对边缘D触发器74 LS74的逻辑功能进行测试,填写D触发器的特性表。

3(用D触发器实现计数功能和分频功能。

4(用4个D触发器设计一个4位的环形计数器。

三、实验条件:1、硬件基础电学实验箱、双踪示波器、电源。

2、元器件:74LS00、74LS74、74LS175。

四、实验过程:1、搭接一个基本RS触发器,对其功能进行测试。

a) 实验原理:基本RS触发器是由二个与非门交叉藕合构成的。

基本RS触发器具有置"0"、置"1"ssR和"保持"三种功能。

通常称为置"1"端,因为=0时触发器被置"1"; 为置"0"端,因sRR为=0时触发器被置"0",当 = =1时状态保持。

基本RS触发器也可以用二个"或非门"组成,此时为高电平触发器。

b) 实验电路图:c)RS触发器特性表:equipment, components, equipment, temporary construction facilities, processed with strict compliance with provisions of construction floor plans, smooth roads and drainage, site formation. ----3, the site looks dignified and elegant and tidy, advertising slogans to write eye-catching appearance, walls to be clean and tidy. 4, "six-second figure"----cards to complete, custom, eye-catching, hanging in the obvious place. Management----5, district administration, "launch of Qing dynasty" focuses on managing the "cleaning, recycling, use," four Central Bank; the work is finished, clean, clear, work product protection in all procedures to periodically check the appraisals in a timely manner. 6, clean health----engineering work sites, temporary facilities clean and tidy inside and outside. 7, mechanical health----engineering machinery, vehicles are maintained in good condition, looks clean, and free from dirt, dust, electrical switchgear (box) complete with lock, mechanical safety protection equipment and complete, sensitive and reliable. 8, fire, defend----perfect fire system, set in accordance with requirements of fire equipment, set up obvious fire safety signs and signage, provide effective fire-fighting equipment, establishment of a security system, and out of the site staff to wear to work, marks and signs, implementsnn+1S R Q Q0 0 0 10 0 1 10 1 0 10 1 1 11 0 0 01 0 1 01 1 0 01 1 1 1d)实验现象以及结论:现象: 当s=0时,r=1,结果置1。

基于Multisim的红绿灯控制器仿真实现摘要介绍运用Multisim仿真软件, 设计一个十字路口交通灯控制器。

该控制器实现了对十字路口交通信号灯控制。

利用Multisim这种高效的设计平台, 能够方便地设计电路, 并用虚拟仪器库进行仿真以及验证电路是否达到设计要求。

与传统的设计方法相比, 它具有省时、低成本、高效率的优越性。

关键词:Multisim,交通控制器,EDA,CADDesign and Simulation of Traff ic Lights Controller at theCrossroads Based on MultisimAbstractA traffic lights controller at the crossroads was designed based on Multisim simulation software, and the traffic signal lights control at the crossroads was realized. It is easy to design the electric circuit by using high efficient Multisim design platform, make the simulation by virtual instrument libraries, and verify the electric circuit whether or not meet the design requirements. It has superiority of time saving, low-cost and efficient by comparing with the traditional design method. Keywords: Multisim, traffic controller, EDA, CAD目录1 绪论 (1)1.1引言 (1)1.2交通信号灯控制电路的概述 (1)2 单元模块 (3)2.1电源模块 (3)2.2秒脉冲发生模块 (3)2.3计数模块 (4)2.4逻辑电路模块 (5)2.5分频器模块 (6)3 数字电子钟电路的仿真与调试 (8)3.1交通信号灯控制电路的仿真 (8)3.2交通信号灯控制电路的实现 (8)3.3调试方法 (9)4 调试中出现的问题和解决方法 (10)5 结语 (11)参考文献 (12)1 绪论1.1引言随着计算机与微电子技术的发展, 电子设计自动化EDA领域已成为电子技术发展的主体。

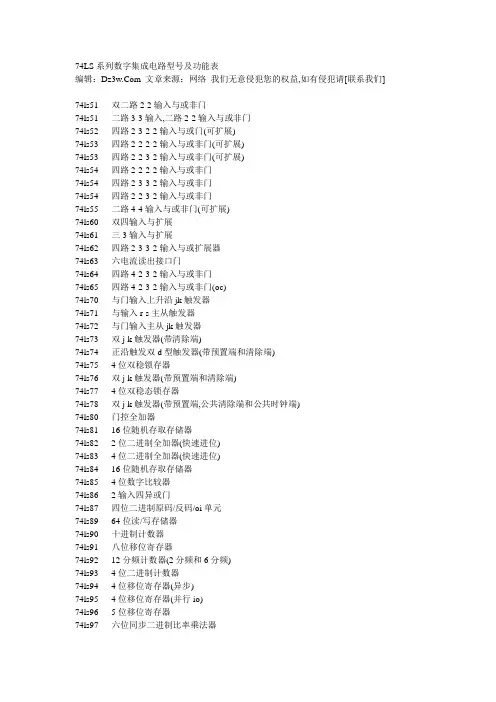

74LS系列数字集成电路型号及功能表编辑: 文章来源:网络我们无意侵犯您的权益,如有侵犯请[联系我们]74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展)74ls53 四路2-2-3-2输入与或非门(可扩展)74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端)74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器Reference URL:/info/logicIC/4186_2.html。

引言近年来, 在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要.在电子系统非常广泛应用领域内, 到处可见到解决离散信息的数字电路。

供消费用的微波炉和电视、先进的工业控制系统、空间通讯系统、交通控制雷达系统、医院急救系统等在设计过程中无一不用到数字技术。

数字电路制造工业的进步, 使得系统设计人员能在更小的空间内实现更多的功能, 从而提高系统可靠性和速度。

数字集成电路具有结构简朴(如其中的晶体管是工作于饱和与截止2种状态, 一般不设偏置电流)和同类型电路单元多(如一个计数系统需要很多同类型的触发器和门电路)的特点, 因而容易是高集成度和归一化。

由于数字集成电路与电子计算机的发展紧密相关, 因而发展不久, 目前已是集成电路中产量最高、集成度最大的一种器件。

集成电路的类型很多, 从大的方面可分为模拟和数字集成电路两大类。

虽然它们都可模拟具体的物理过程, 但其工作方式有着很大的不同。

甚至也许完全不同。

电路中的工作信号通常是用电脉冲表达的数字信号。

这种工作方式的信号, 可以表达2种截然不同的现象。

如以有脉冲表达“1”, 无脉冲便表达“0”;以“1”表达“真”, 则“0”便表达“假”, 等等。

反之亦然。

这就是“数字信号”的含义。

所以, “数字量”不是连续变化的量, 其大小往往并不改变, 但在时间分布上却有着严格的规定, 这是数字电路的一个特点。

数字式频率计基于时间或频率的A/D转换原理, 并依赖于数字电路技术发展起来的一种新型的数字测量仪器。

由于数字电路的飞速发展, 所以, 数字频率计的发展也不久。

通常能对频率和时间两种以上的功能数字化测量仪器, 称为数字式频率计(通用计数器或数字式技术器)。

在电子测量技术中, 频率是一个最基本的参量, 对适应晶体振荡器、各种信号发生器、倍频和分频电路的输出信号的频率测量, 广播、电视、电讯、微电子技术等现代科学领域。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

![[转载]分频电路,二分频、三分频和四分频](https://uimg.taocdn.com/f1aace0c640e52ea551810a6f524ccbff121caac.webp)

[转载]分频电路,⼆分频、三分频和四分频原⽂地址:分频电路,⼆分频、三分频和四分频作者:davis⾳箱的⾼中低频主要靠分频器来区分。

分频器按分频频段可分⼆分频、三分频和四分频。

⼆分频是将⾳频信号的整个频带划分为⾼频和低频两个频段;三分频是将整个频带划分成⾼频、中频和低频三个频段;四分频将三分频多划分出⼀个超低频段。

分频点与分频斜率是直接影响分频品质分频频率(交*频率)。

分频点是指两个相邻扬声器(如⼆分频中的⾼⾳与低⾳,三分频中的⾼⾳与中⾳,中⾳与低⾳)的频响曲线在某⼀频率上的相交点,通常为两个扬声器中功率输出的⼀半处(即-3dB点)的频率,要根据⾳箱和每个扬声器的频率特性和失真度等参数决定。

通常⼆分选购上,建议您在购买的时候⼀定要多加⼩⼼,不要盲⽬地听店主的推荐和介绍,买这种东西绝对不可以⼼急。

最好之前楼主多去⼀些⾳响论坛先去具体了解些⾳响知识。

个⼈建议楼主去⾼级别的钻⽯卖家购买,与卖家多聊聊,还可以通过聊天软件向曾经购买者在⼀个扬声器系统⾥,⼈们把箱体、分频电路、扬声器单元称为扬声器系统的三⼤件,⽽分频电路对扬声器系统能否⾼质量地还原电声信号起着极其重要的作⽤。

尤其在中、⾼频部分,分频电路所起到的作⽤就更为明显。

编辑摘要⽬录[隐藏 ]1 作⽤2 分频点3 分频⽅式4 优点5 挑选分频电路 - 作⽤分频电路作⽤如下:1、合理地分割各单元的⼯作频段;2、合理地进⾏各单元功率分配;3、使各单元之间具有恰当的相位关系以减少各单元在⼯作中出现的声⼲涉失真;4、利⽤分频电路的特性以弥补单元在某频段⾥的声缺陷;5、将各频段圆滑平顺地对接起来。

显然,分频电路的这些作⽤已被⼈们所认识和接受。

分频电路 - 分频点脉冲分频电路1·分频点指分频器⾼通、带通和低通滤波器之间的分界点,常⽤频率来表⽰,单位为赫兹。

分频点应根据各频段扬声器单元或⾳箱的频率特性和功率分配来具体确定。

2·分频点的选择:1)、考虑中低单元指向性实⽤边界频率f=345/d(d=单元振膜有效直径)。

班级:08020903 姓名:罗林学号:2009301953实验四触发器及其应用一、实验目的:1)熟悉基本D触发器的功能测试。

2)了解触发器的两种触发方式(脉冲电平触发和脉冲边沿触发)及触发特点。

3)熟悉触发器的实际应用。

二、实验设备:1)数字电路实验箱2)函数信号发生器、数字双踪示波器3)数字万用表4)74LS00、74LS74三、实验原理:触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

在数字系统和计算机中有着广泛的应用。

触发器具有两个稳定状态,即“0”和“1”,,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

触发器有集成触发器和门电路组成的触发器。

触发方式有电平触发和边沿触发两种。

D触发器在时钟脉冲CP的前沿(正跳变0→1)发生翻转,触发器的次态取决于CP的脉冲上升沿到来之前D端的状态,即=D。

因此,它具有置0、置1两种功能。

由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

和分别是决定触发器初始状态的直接置0、置1端。

当不需要强迫置0、置1时,和端都应置高电平(如接+5V电源)。

74LS74,74LS175等均为上升沿触发的边沿触发器。

图一为74LS74的引脚图和逻辑图。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等。

74LS74引脚图和逻辑图四、实验内容1.用D触发器构成4分频器四分频电路图:2.设计电路实现如下波形五、实验结果四分频实验结果波形:2.实验结果波形:。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。