完整版以太网接口分析

- 格式:docx

- 大小:103.26 KB

- 文档页数:7

以太网物理接口介绍一、以太网接口类型以太网接口常用有双绞线接口(俗称电口)和光纤接口(俗称光口)2种。

另外还有早期的同轴电缆接口。

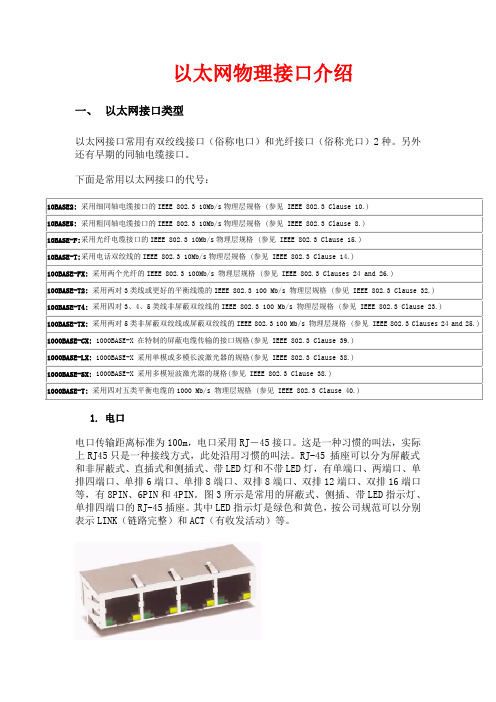

下面是常用以太网接口的代号:10BASE2: 采用细同轴电缆接口的IEEE 802.3 10Mb/s物理层规格 (参见 IEEE 802.3 Clause 10.)10BASE5: 采用粗同轴电缆接口的IEEE 802.3 10Mb/s物理层规格 (参见 IEEE 802.3 Clause 8.)10BASE-F:采用光纤电缆接口的IEEE 802.3 10Mb/s物理层规格 (参见 IEEE 802.3 Clause 15.)10BASE-T:采用电话双绞线的IEEE 802.3 10Mb/s物理层规格 (参见 IEEE 802.3 Clause 14.)100BASE-FX: 采用两个光纤的IEEE 802.3 100Mb/s 物理层规格 (参见 IEEE 802.3 Clauses 24 and 26.)100BASE-T2: 采用两对3类线或更好的平衡线缆的IEEE 802.3 100 Mb/s 物理层规格 (参见 IEEE 802.3 Clause 32.)100BASE-T4: 采用四对3、4、5类线非屏蔽双绞线的IEEE 802.3 100 Mb/s 物理层规格 (参见 IEEE 802.3 Clause 23.)100BASE-TX: 采用两对5类非屏蔽双绞线或屏蔽双绞线的IEEE 802.3 100 Mb/s 物理层规格 (参见 IEEE 802.3 Clauses 24 and 25.) 1000BASE-CX: 1000BASE-X 在特制的屏蔽电缆传输的接口规格(参见 IEEE 802.3 Clause 39.)1000BASE-LX: 1000BASE-X 采用单模或多模长波激光器的规格(参见 IEEE 802.3 Clause 38.)1000BASE-SX: 1000BASE-X 采用多模短波激光器的规格(参见 IEEE 802.3 Clause 38.)1000BASE-T: 采用四对五类平衡电缆的1000 Mb/s 物理层规格 (参见 IEEE 802.3 Clause 40.)1.电口电口传输距离标准为100m,电口采用RJ-45接口。

以太网知识GMII / RGMII接口本文主要分析MII/RMII/SMII,以及GMII/RGMII/SGMII接口的信号定义,及相关知识,同时本文也对RJ-45接口进行了总结,分析了在10/100模式下和1000M模式下的连接方法。

1. GMII 接口分析GMII接口提供了8位数据通道,125MHz的时钟速率,从而1000Mbps的数据传输速率。

下图定义了RS层的输入输出信号以及STA的信号:图18 Reconciliation Sublayer (RS) and STA connections to GMII下面将详细介绍GMII接口的信号定义,时序特性等。

由于GMII接口有MAC和PHY模式,因此,将会根据这两种不同的模式进行分析,同时还会对RGMII/TBI/RTBI接口进行介绍。

4.1 GMII接口信号定义GMII接口可分为MAC模式和PHY模式,一般说来MAC和PHY对接,但是MAC和MAC也是可以对接的。

在GMII接口中,它是用8根数据线来传送数据的,这样在传送1000M数据时,时钟就会125MHz。

GMII接口主要包括四个部分。

一是从MAC层到物理层的发送数据接口,二是从物理层到MAC层的接收数据接口,三是从物理层到MAC层的状态指示信号,四是MAC层和物理层之间传送控制和状态信息的MDIO接口。

GMII接口的MAC模式定义:注意在表7中,信号GTX_CLK对于MAC来说,此时是Output信号,这一点和MII接口中的TX_CLK的Input特性不一致。

GMII接口PHY模式定义:表8注意在表8中,信号GTX_CLK对于PHY来说,此时是Input信号,这一点和MII接口中的TX_CLK的Output特性不一致。

4.2 GMII接口时序特性在GMII接口中,TX通道参考时钟是GTX_CLK,RX通道参考时钟是RX_CLK,802.3-2005定义了它们之间的关系。

图19 GMII signal timing at receiver input由图19可知,Spec只定义了TX通道和RX通道中接收端Setup时间和Hold时间。

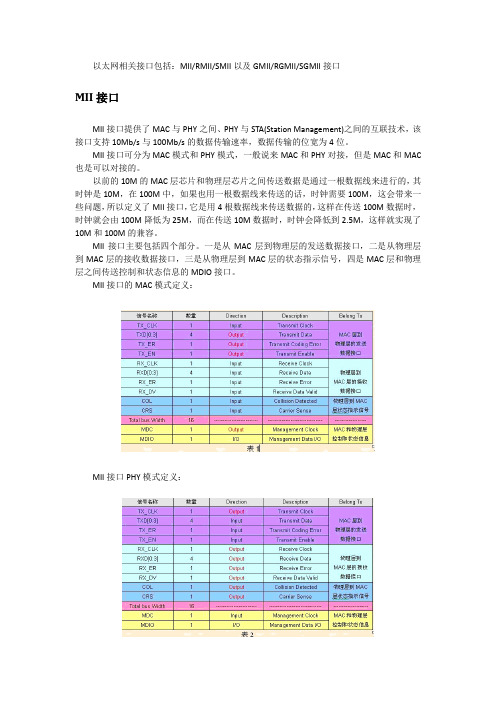

以太网相关接口包括:MII/RMII/SMII以及GMII/RGMII/SGMII接口MII接口MII接口提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术,该接口支持10Mb/s与100Mb/s的数据传输速率,数据传输的位宽为4位。

MII接口可分为MAC模式和PHY模式,一般说来MAC和PHY对接,但是MAC和MAC 也是可以对接的。

以前的10M的MAC层芯片和物理层芯片之间传送数据是通过一根数据线来进行的,其时钟是10M,在100M中,如果也用一根数据线来传送的话,时钟需要100M,这会带来一些问题,所以定义了MII接口,它是用4根数据线来传送数据的,这样在传送100M数据时,时钟就会由100M降低为25M,而在传送10M数据时,时钟会降低到2.5M,这样就实现了10M和100M的兼容。

MII接口主要包括四个部分。

一是从MAC层到物理层的发送数据接口,二是从物理层到MAC层的接收数据接口,三是从物理层到MAC层的状态指示信号,四是MAC层和物理层之间传送控制和状态信息的MDIO接口。

MII接口的MAC模式定义:MII接口PHY模式定义:MDIO接口包括两根信号线:MDC和MDIO,通过它,MAC层芯片(或其它控制芯片)可以访问物理层芯片的寄存器(前面100M物理层芯片中介绍的寄存器组,但不仅限于100M 物理层芯片,10M物理层芯片也可以拥有这些寄存器),并通过这些寄存器来对物理层芯片进行控制和管理。

MDIO管理接口如下:MDC:管理接口的时钟,它是一个非周期信号,信号的最小周期(实际是正电平时间和负电平时间之和)为400ns,最小正电平时间和负电平时间为160ns,最大的正负电平时间无限制。

它与TX_CLK和RX_CLK无任何关系。

MDIO是一根双向的数据线。

用来传送MAC层的控制信息和物理层的状态信息。

RMII接口MII接口也有一些不足之处,主要是其接口信号线很多,发送和接收和指示接口有14根数据线(不包括MDIO接口的信号线,因为其被所有MII接口所共享),当交换芯片的端口数据较多时,会造成芯片的管脚数目很多的问题,这给芯片的设计和单板的设计都带来了一定的问题。

实时嵌入式系统以太网接口及应用网络层次模型以太网层次模型以太网层次功能物理层:物理层:定义了数据传输与接收所需要的光与电信号光与电信号,,线路状态线路状态,,时钟基准时钟基准,,数据编码电路等编码电路等。

并向数据链路层设备提供标准接口准接口。

数据链路层数据链路层::提供寻址机制提供寻址机制,,数据帧的构建,数据差错检查数据差错检查,,传输控制传输控制。

向网络层提供标准的数据接口等功能提供标准的数据接口等功能。

IP 层IP 数据报以太网的MAC 帧格式在帧的前面插入的8 字节中的第一个字段共7 个字节,是前同步码,用来迅速实现MAC 帧的比特同步。

第二个字段是帧开始定界符,表示后面的信息就是MAC 帧。

MAC 帧物理层MAC 层以太网V2MAC 帧目的地址源地址类型数据FCS6624字节46 ~ 150010101010101010 10101010101010101011前同步码帧开始定界符7 字节1 字节…8 字节插入为了达到比特同步,在传输媒体上实际传送的要比MAC 帧还多8 个字节以太网接口的构成从硬件的角度看,从硬件的角度看,以太网接口电路主要由MAC MAC控制器和物理层接口控制器和物理层接口控制器和物理层接口((Physical Layer Physical Layer,,PHY PHY))两大部分构成两大部分构成。

嵌入式网络应用的两种方案处理器加以太网接口芯片处理器加以太网接口芯片。

芯片如芯片如RTL8019RTL8019RTL8019、、RTL8029RTL8029、、RTL8139RTL8139、、CS8900CS8900、、DM9000DM9000等等,其内部结构也主要包含这两部分部结构也主要包含这两部分。

自带自带MAC MAC MAC控制器的处理器加物理层接口芯片控制器的处理器加物理层接口芯片控制器的处理器加物理层接口芯片。

如DP83848DP83848、、BCM5221BCM5221、、ICS1893ICS1893等等。

内部公开▲本文中的所有信息归中兴通讯股份有限公司所有,未经允许,不得外传 第 1 / 9 页以太网接口说明1十兆以太网接口 ..................................................................................................................................... 1 1.1 10BASE-F ................................................................................................................................... 1 1.2 10BASE2 .................................................................................................................................... 1 1.3 10BASE5 .................................................................................................................................... 2 1.4 10BASE-T ................................................................................................................................... 2 2 百兆以太网接口 . (2)2.1 100base-T (3)2.2 100BASE-TX (4)2.3 100BASE-FX (4)2.4 100Base-T4 (4)2.5 100Base-T2 (5)3 千兆以太网接口 (5)3.1 1000BASE-SX (5)3.2 1000BASE-LX (5)3.3 1000BASE-CX (5)3.4 1000BASE-T (5)4 网卡 LED 说明 (8)5 双绞线..................................................................................................................................................... 9 6无屏蔽双绞线类别 (9)1 十兆以太网接口1.1 10BASE-F10base-F ;是使用光缆的以太网,使用双工光缆,一条光缆用于发送数据, 另一条用于接收;使用ST 连接器,星形拓扑结构;网络直径为2500m ,定义了4种不同的规范:10Base-FL ;是10base-F 中使用最多的部分,只有10base-FL 连接时,光缆链路 段的长度可达到2000m ,与FOIRL 设备混用时,混合段的长度可达1000m 。

MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:TXD[3:0]:数据发送信号,共4根信号线;RXD[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类似于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS 就有效,另外,CRS只在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只在半双工模式下有效。

MII接口一共有16根线(TX_CLK, RX_CLK未记入)。

以太网知识(4)-TBI接口-ten bit interface作者:luqiliang 日期:2010-5-14 15:36:41字体大小: 小中大本文主要分析MII/RMII/SMII,以及GMII/RGMII/SGMII接口的信号定义,及相关知识,同时本文也对RJ-45接口进行了总结,分析了在10/100模式下和1000M 模式下的连接方法。

6. TBI接口分析所为TBI,即Ten-Bit interface,10位接口(TBI)从千兆媒体独立接口(GMII)演化而来,它们都是千兆以太网的接口。

TBI与GMII接口的主要区别在于,GMII 接口还包括物理编码子层(PCS)功能,支持TBI接口的器件通常不包含上述功能,如图26中被方框圈起来的部分。

选择TBI还是GMII接口,主要取决于所采用的媒体访问控制器(MAC)以及是否具备必需的PCS功能,或收发器是否需要这些功能。

图26从图26可以看出,千兆以太网协议与10/100Mb/s以太网协议的差别仅仅在于物理层。

图中的PHY表示实现物理层协议的芯片;协调子层(Reconciliation sublayer)用于实现指令转换;MII(介质无关接口)/GMII(吉比特介质无关接口)是物理层芯片与实现上层协议的芯片的接口;MDI(介质相关接口)是物理层芯片与物理介质的接口;PCS、PMA和PMD则分别表示实现物理层协议的各子层。

在实际应用系统中,这些子层的操作细节将全部由PHY芯片实现,只需对MII和MDI接口进行设计与操作即可。

吉比特以太网的物理层接口标准主要有四种:GMII、RGMII(Reduced GMII)、TBI(Ten-Bit Interface)和RTBI(Reduced TBI)。

GMII是标准的吉比特以太网接口,它位于MAC层与物理层之间。

对于TBI接口,图26中PCS子层的功能将由MAC层芯片实现,在降低PHY芯片复杂度的同时,控制线也比GMII接口少。

以太网接口设计技巧1. 满足吞吐量需求:根据实际使用环境和网络负载,选择合适的以太网接口速率和带宽,确保能够满足吞吐量需求。

常见的以太网接口速率包括10Mbps、100Mbps、1Gbps、10Gbps等。

如果需求较高,可以考虑使用双绞线接口、光纤接口或高速以太网接口。

2.网络协议支持:以太网接口设计要考虑支持的网络协议,如IP协议、TCP协议、UDP协议等。

确保以太网接口能够兼容常用的网络协议,并能够进行数据包的正确解析和处理,以保证数据的完整性和可靠性。

3.抗干扰能力:以太网接口设计时要考虑抗干扰能力,避免外部信号对数据传输造成干扰。

可以采用屏蔽接口、差分信号传输和滤波电路等技术手段,提高以太网接口的抗干扰能力。

4.自适应速率:为了适应不同的网络环境和负载需求,以太网接口设计中可以加入自适应速率的功能。

即根据实际网络负载和带宽情况,动态调整以太网接口的速率和带宽,提高网络性能和资源利用率。

5.容错设计:以太网接口设计时要考虑容错能力,避免因单点故障导致整个网络中断。

可以采用网络冗余、链路聚合和设备备份等技术手段,提高以太网接口的容错能力。

6. QoS支持:为了保证网络中关键应用的性能,以太网接口设计中可以支持QoS(Quality of Service)服务。

通过对不同类型的数据包进行优先级处理和调度,保证关键应用的带宽和延迟需求。

7. DMA技术:采用DMA(Direct Memory Access)技术可以提高以太网接口的数据传输效率。

通过直接访问主存储器,减少CPU的参与,加快数据传输速度,并释放CPU资源用于其他计算任务。

8.简化驱动程序:以太网接口设计时要考虑简化驱动程序的开发和维护工作。

可以提供易用的API和标准接口,帮助开发人员快速开发和集成以太网接口驱动程序。

9.功耗优化:以太网接口设计中可以考虑功耗优化,减少不必要的能源消耗。

可以采用低功耗模式、动态功耗管理和智能唤醒等技术手段,降低以太网接口的功耗,延长电池寿命。

MII 接口MII接口提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术,该接口支持10Mb/s与100Mb/s的数据传输速率,数据传输的位宽为4位。

MII接口可分为MAC模式和PHY模式,一般说来MAC和PHY对接,但是MAC和MAC 也是可以对接的。

以前的10M的MAC层芯片和物理层芯片之间传送数据是通过一根数据线来进行的,其时钟是10M,在100M中,如果也用一根数据线来传送的话,时钟需要100M,这会带来一些问题,所以定义了Mil接口,它是用4根数据线来传送数据的,这样在传送100M数据时,时钟就会由100M降低为25M,而在传送10M数据时,时钟会降低到 2.5M,这样就实现了10M和100M 的兼容。

MII接口主要包括四个部分。

一是从MAC层到物理层的发送数据接口,二是从物理层到MAC 层的接收数据接口,三是从物理层到MAC层的状态指示信号,四是MAC层和物理层之间传送控制和状态信息的MDIO接口。

MII接口的MAC模式定义:MII接口PHY模式定义:表上MDIO接口包括两根信号线:MDC和MDIO,通过它,MAC层芯片(或其它控制芯片)可以访问物理层芯片的寄存器(前面100M物理层芯片中介绍的寄存器组,但不仅限于100M 物理层芯片,10M物理层芯片也可以拥有这些寄存器),并通过这些寄存器来对物理层芯片进行控制和管理。

MDIO管理接口如下:MDC:管理接口的时钟,它是一个非周期信号,信号的最小周期(实际是正电平时间和负电平时间之和)为400ns,最小正电平时间和负电平时间为160 ns,最大的正负电平时间无限制。

它与TX_CLK和RX_CLK无任何关系。

MDIO是一根双向的数据线。

用来传送MAC层的控制信息和物理层的状态信息。

RMII 接口MII接口也有一些不足之处,主要是其接口信号线很多,发送和接收和指示接口有14根数据线(不包括MDIO接口的信号线,因为其被所有Mil接口所共享),当交换芯片的端口数据较多时,会造成芯片的管脚数目很多的问题,这给芯片的设计和单板的设计都带来了一定的问题。

为了解决这些问题,人们设计了两种新的Mil接口,它们是RMII接口(Reduced MII 接口)和SMII 接口(StreamMII 接口)。

这两种接口都减少了Mil接口的数据线,不过它们一般只用在以太网交换机的交换MAC 芯片和多口物理层芯片中,而很少用于单口的MAC层芯片和物理层芯片中。

RMII接口和SMII 接口都可以用于10M以太网和100M以太网,但不可能用于1000M以太网,因为此时时钟频率太高,不可能实现。

从图中可以看到,RMII接口相对于Mil接口减少了一半的连接线只有8根接口线。

TXD[1:0]:数据发送信号线,数据位宽为2,是Mil接口的一半;RXD[1:0]:数据接收信号线,数据位宽为2,是Mil接口的一半;TX_EN(Transmit Enable):数据发送使能信号,与Mil接口中的该信号线功能一样;RX_ER(Receive Error)数据接收错误提示信号,与Mil接口中的该信号线功能一样;CLK_REF是由外部时钟源提供的50MHz参考时钟,与Mil接口不同,Mil接口中的接收时钟和发送时钟是分开的,而且都是由PHY芯片提供给MAC芯片的。

这里需要注意的是,由于数据接收时钟是由外部晶振提供而不是由载波信号提取的,所以在PHY层芯片内的数据接收部分需要设计一个FIFO,用来协调两个不同的时钟,在发送接收的数据时提供缓冲。

PHY 层芯片的发送部分则不需要FIFO,它直接将接收到的数据发送到MAC就可以了。

CRS_DV此信号是由Mil接口中的RX_DV和CRS两个信号合并而成。

当介质不空闲时,CRS_DV 和RE_CLK相异步的方式给出。

当CRS比RX_DV早结束时(即载波消失而队列中还有数据要传输时),就会出现CRS_DV在半位元组的边界以25MHz/2.5MHz的频率在0、1之间的来回切换。

因此,MAC能够从CRS_DV中精确的恢复出RX_DV和CRS在100Mbps速率时,TX/RX每个时钟周期采样一个数据;在10Mbps速率时,TX/RX每隔10 个周期采样一个数据,因而TX/RX数据需要在数据线上保留10个周期,相当于一个数据发送10次。

当PHY层芯片收到有效的载波信号后,CRS_DV言号变为有效,此时如果FIF0中还没有数据,则它会发送出全0的数据给MAC,然后当FIFO中填入有效的数据帧,数据帧的开头是“ 101010--- ”交叉的前导码,当数据中出现“ 01”的比特时,代表正式数据传输开始,MAC 芯片检测到这一变化,从而开始接收数据。

当外部载波信号消失后,CRS_DV会变为无效,但如果FIFO中还有数据要发送时,CRS_DV 在下一周期又会变为有效,然后再无效再有效,直到FIFO中数据发送完为止。

在接收过程中如果出现无效的载波信号或者无效的数据编码,则RX_ER会变为有效,表示物理层芯片接收出错。

SMII 接口SMII即Serial Mil,串行Mil的意思,跟RMII相比,连线进一步减少到4根;TXD:发送数据信号,位宽为 1 ;RXD接收数据信号,位宽为 1 ;SYNC收发数据同步信号,每10个时钟周期置1次高电平,指示同步。

CLK_REF所有端口共用的一个参考时钟,频率为125MHz,为什么100Mbps速率要用125MHz时钟?因为在每8位数据中会插入2位控制信号,请看下面介绍。

TXD/RXD以10比特为一组,以SYNC为高电平来指示一组数据的开始,在SYNC变高后的10个时钟周期内,TXD上依次输出的数据是:TXD[7:0]、TX_EN TX_ER控制信号的含义与Mil接口中的相同;RXD上依次输出的数据是:RXD[7:0]、RX_DV CRS RXD[7:0]的含义与RX_DV有关,当RX_DV为有效时(高电平),RXD[7:0]上传输的是物理层接收的数据。

当RX_DV 为无效时(低电平),RXD[7:0]上传输的是物理层的状态信息数据。

GMII 接口与Mil接口相比,GMII的数据宽度由4位变为8 位, GMII接口中的控制信号如TX_ER TX_EN RX_ER RX_DV CRS和COL的作用同Mil接口中的一样,发送参考时钟GTX_CLK和接收参考时钟RX_CLK勺频率均为125MHz(1000Mbps/8=125MHz)。

在这里有一点需要特别说明下,那就是发送参考时钟GTX_CLK它和Mil接口中的TX_CLK是不同的,Mil接口中的TX_CLK是由PHY芯片提供给MAC芯片的,而GMII接口中的GTX_CLK 是由MAC芯片提供给PHY芯片的。

两者方向不一样。

在实际应用中,绝大多数GMII接口都是兼容Mil接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK两者的方向是不一样的,前面已经说过了),在用作Mil 模式时,使用TX_CLK和8根数据线中的4根。

RGMII 接口RGMII即Reduced GMII,是GMII的简化版本,将接口信号线数量从24根减少到14根(COL/CRS端口状态指示信号,这里没有画出),时钟频率仍旧为125MHz , TX/RX数据宽度从8为变为4位,为了保持1000Mbps的传输速率不变,RGMII接口在时钟的上升沿和下降沿都采样数据。

在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送GMII接口中的TXD[7:4]/RXD[7:4] °RGMI同时也兼容100Mbps和10Mbps两种速率,此时参考时钟速率分别为25MHz和2.5MHz。

TX_EN 信号线上传送TX_EN 和TX_ER 两种信息,在TX_CLK 的上升沿发送TX_EN 下降沿发 送TX_ER 同样的,RX_DV 信号线上也传送 RX_DV 和RX_ER 两种信息,在 RX_CLK 勺上升沿 发送RX_DV 下降沿发送RX_ERRXC-VI /<—T_HAV fK___________T HA/ fi1—<>:RXDI&.0]T_SU*VoRX_D^ FXERfi •:'HX.DV*3阿林X RX DVSGMII 接口SGMII 即Serial GMII ,串行GMII ,收发各一对差分信号线,时钟频率 625MHz ,在时钟 信号的上升沿和下降沿均采样,参考时钟 RX_CLK 由 PHY 提供,是可选的,主要用于 MAC 侧没有时钟的情况,一般情况下,RX_CLK 不使用。

收发都可以从数据中恢复出时钟。

在TXD 发送的串行数据中,每 8比特数据会插入 TX_EN/TX_ER 两比特控制信息,同样,在 RXD 接收数据中,每8比特数据会插入 RX_DV/RX_ER 两比特控制信息,所以总的数据速率 为 1.25Gbps=625Mbps*2.其实,大多数MAC 芯片的SGMII 接口都可以配置成 SerDes 接口(在物理上完全兼容,只需配 置寄存器即可),直接外接光模块,而不需要PHY 层芯片,此时时钟速率仍旧是625MHz ,不过此时跟SGMII 接口不同,SGMII 接口速率被提高到1.25Gbps 是因为插入了控制信息, 而SerDes 端口速率被提高是因为进行了 8B/10B 变换,本来8B/10B 变换是PHY 芯片的工作, 在SerDes 接口中,因为外面不接 PHY 芯片,此时8B/10B 变换在MAC 芯片中完成了。

T SETUP f ij ____________________ i M EF—T_MOLD ―1XE-F4]XTXrp-4]>BCD网TM1[7d]£ Txn[i-c (}"T_SETUPV - T _HQLP =TAEM■rJUzHHIXlzM*TXEHHCiT>CI K。