《集成电路设计原理》试卷及答案课件

- 格式:doc

- 大小:770.87 KB

- 文档页数:8

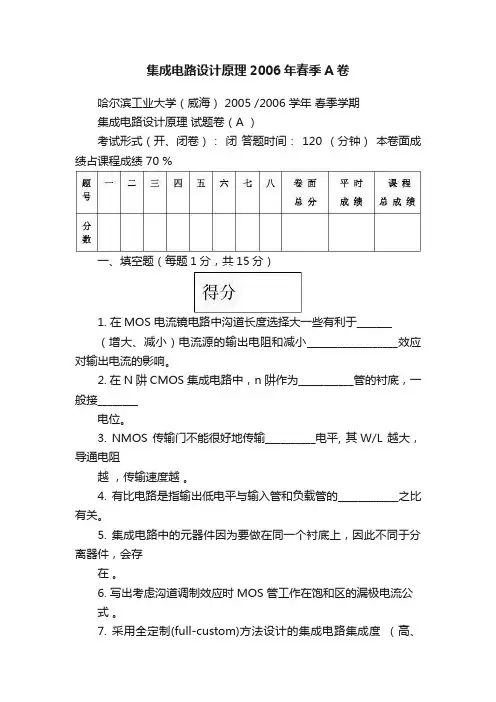

集成电路设计原理2006年春季A卷哈尔滨工业大学(威海) 2005 /2006 学年春季学期集成电路设计原理试题卷(A )考试形式(开、闭卷):闭答题时间: 120 (分钟)本卷面成绩占课程成绩 70 %一、填空题(每题1分,共15分)1. 在MOS 电流镜电路中沟道长度选择大一些有利于_______(增大、减小)电流源的输出电阻和减小__________________效应对输出电流的影响。

2. 在N 阱CMOS 集成电路中,n 阱作为___________管的衬底,一般接________电位。

3. NMOS 传输门不能很好地传输__________电平, 其W/L 越大,导通电阻越,传输速度越。

4. 有比电路是指输出低电平与输入管和负载管的____________之比有关。

5. 集成电路中的元器件因为要做在同一个衬底上,因此不同于分离器件,会存在。

6. 写出考虑沟道调制效应时MOS 管工作在饱和区的漏极电流公式。

7. 采用全定制(full-custom)方法设计的集成电路集成度(高、低),适用于(通用、专用)集成电路芯片的设计。

姓名: 班级:学号:遵守考试纪律注意行为规范8.一个DAc工作时的参考电压为V ref,接收n位的数字信号(b1b2…. b n),最低有效位用LSB表示,则LSB等于,其分辨率为,量化噪声最大为。

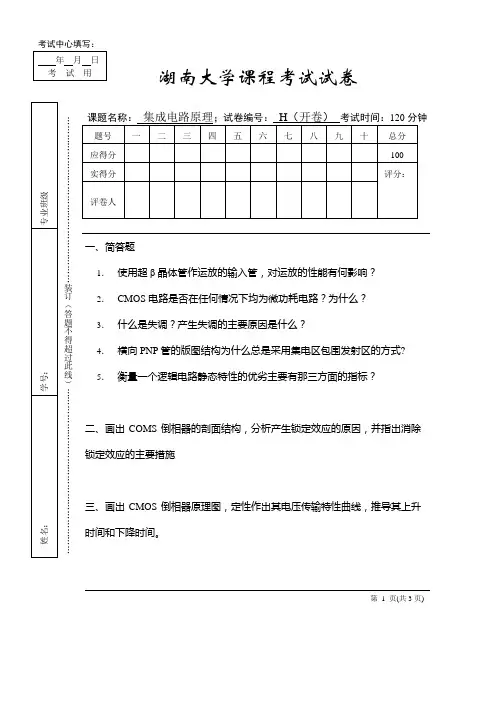

二、(共15分)右图是一N阱CMOS工艺电路的版图。

1.画出对应的电路图(7分);2.分析电路功能,写出逻辑表达式(2分);3.按工艺流程的先后顺序,写图中所用到的光刻掩膜版名称,并在图中选择典型图形标明(6分)。

AFB C三、(共8分)下图中V in为一模拟集成电路的一输入端,为其画出采用MOS 管形式的抗静电保护电路,阐述其工作原理并说明对保护管尺寸有何要求(8分);V SS1.说明TTL电路单管逻辑门级联时的三问题(3分);2.简述ECL电路和I2L电路的特点(4分);3.阐述CMOS电路中抗闩锁设计的重要性(3分)。

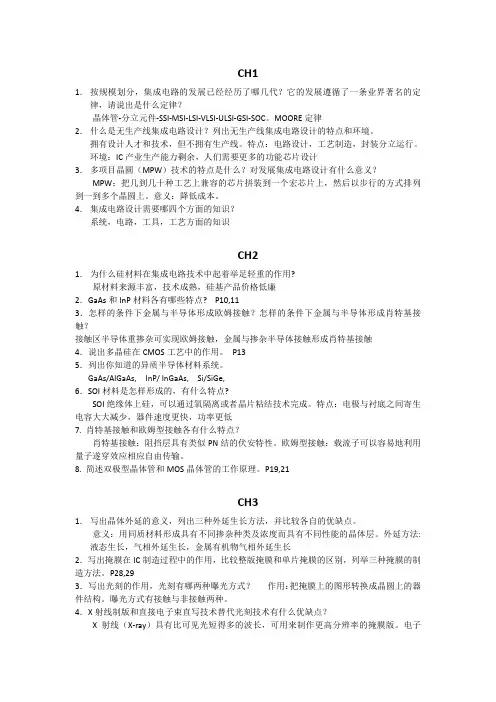

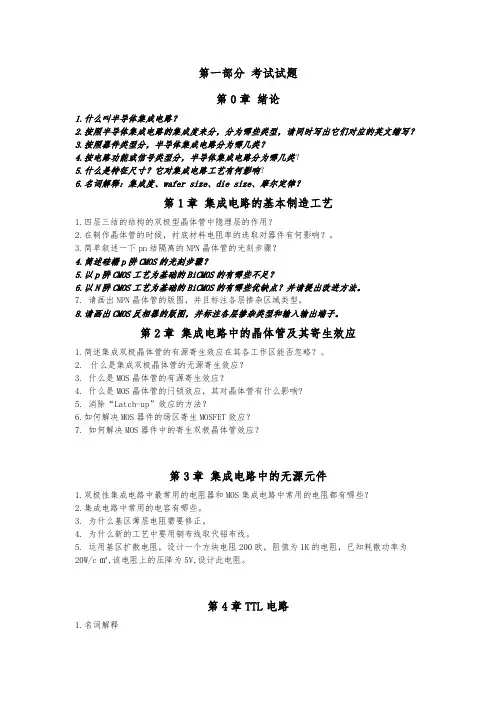

第一部分考试试题第0章绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类?5.什么是特征尺寸?它对集成电路工艺有何影响?6.名词解释:集成度、wafer size、die size、摩尔定律?第1章集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤?4.简述硅栅p阱CMOS的光刻步骤?5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足?6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。

7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。

8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。

第2章集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2.什么是集成双极晶体管的无源寄生效应?3. 什么是MOS晶体管的有源寄生效应?4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up”效应的方法?6.如何解决MOS器件的场区寄生MOSFET效应?7. 如何解决MOS器件中的寄生双极晶体管效应?第3章集成电路中的无源元件1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性 开门/关门电平 逻辑摆幅 过渡区宽度 输入短路电流 输入漏电流静态功耗 瞬态延迟时间 瞬态存储时间 瞬态上升时间 瞬态下降时间瞬时导通时间2. 分析四管标准TTL 与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

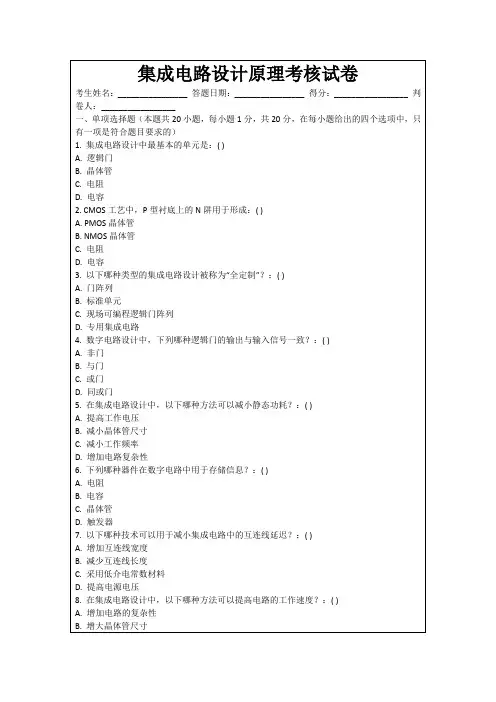

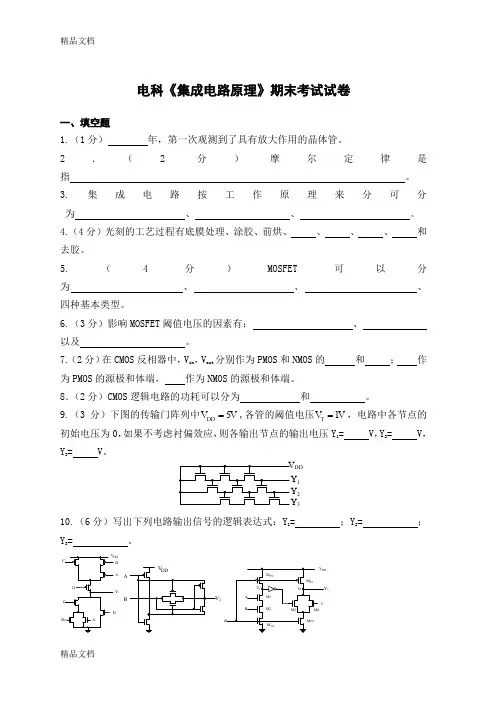

电科《集成电路原理》期末考试试卷一、填空题1.(1分) 年,第一次观测到了具有放大作用的晶体管。

2.(2分)摩尔定律是指 。

3.集成电路按工作原理来分可分为 、 、 。

4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。

5.(4分)MOSFET可以分为 、 、 、 四种基本类型。

6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。

7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 和 ; 作为PMOS 的源极和体端, 作为NMOS 的源极和体端。

8.(2分)CMOS 逻辑电路的功耗可以分为 和 。

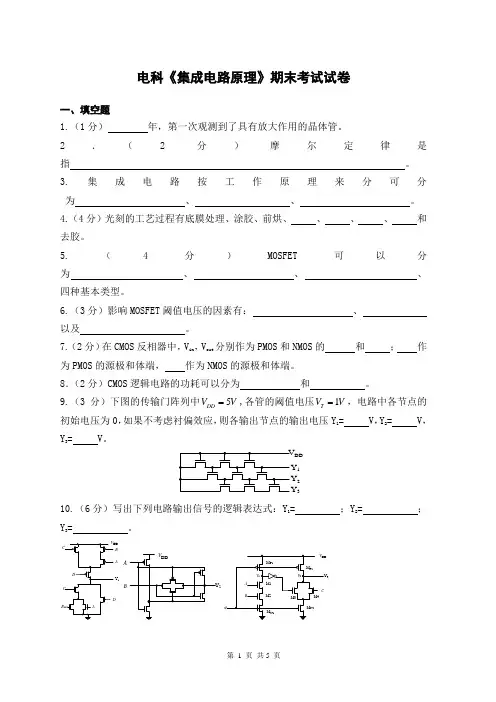

9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= V ,Y 2= V ,Y 3= V 。

DD 13210.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。

AB Y 1AB23二、画图题:(共12分)1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CD=+的电路图,要求使用的MOS管最少。

2.(6分)用动态电路级联实现逻辑功能Y ABC=,画出其相应的电路图。

三、简答题:(每小题5分,共20分)1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么?2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么?3.简述静态CMOS 电路的优点。

4.简述动态电路的优点和存在的问题。

四、分析设计题:(共38分1.(12分)考虑标准0.13m μ CMOS 工艺下NMOS 管,宽长比为W/L=0.26/0.13m m μμ,栅氧厚度为2.6ox t nm =,室温下电子迁移率2220/n cm V s μ=,阈值电压T V =0.3V,计算 1.0GS V =V 、0.3DS V =V 和0.9V 时D I 的大小。

电科《集成电路原理》期末考试试卷一、填空题1.(1分) 年,第一次观测到了具有放大作用的晶体管。

2.(2分)摩尔定律是指 。

3.集成电路按工作原理来分可分为 、 、 。

4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。

5.(4分)MOSFET可以分为 、 、 、 四种基本类型。

6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。

7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 和 ; 作为PMOS 的源极和体端, 作为NMOS 的源极和体端。

8.(2分)CMOS 逻辑电路的功耗可以分为 和 。

9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= V ,Y 2= V ,Y 3= V 。

DD 13210.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。

AB Y 1AB23二、画图题:(共12分)=+的电路图,要求使用的1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CDMOS管最少。

2.(6分)用动态电路级联实现逻辑功能Y ABC=,画出其相应的电路图。

三、简答题:(每小题5分,共20分)1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么?2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么?3.简述静态CMOS 电路的优点。

4.简述动态电路的优点和存在的问题。

四、分析设计题:(共38分1.(12分)考虑标准0.13m μ CMOS 工艺下NMOS 管,宽长比为W/L=0.26/0.13m m μμ,栅氧厚度为2.6ox t nm =,室温下电子迁移率2220/n cm V s μ=,阈值电压T V =0.3V,计算 1.0GS V =V 、0.3DS V =V 和0.9V 时D I 的大小。

《软件工程基础训练》实训报告在倒入酒的方法中,首先判断当前酒量是否已经达到酒杯的容量。

如果是,则提示酒杯已满;如果不是,则将倒入的酒量加到当前酒量上。

实现一个方法,用于从酒杯中倒出酒。

该方法接受一个参数,表示要倒出的酒量。

在倒出酒的方法中,首先判断当前酒量是否大于等于要倒出的酒量。

如果是,则将当前酒量减去要倒出的酒量;如果不是,则提示酒量不足。

实现一个方法,用于获取当前酒量。

在获取酒量的方法中,直接返回当前酒量的值。

2.1.3程序流程图图 12.1.4设计代码package wmx;import java.io.BufferedReader;import java.io.IOException;import java.io.InputStreamReader;import java.util.StringTokenizer;public class Main1 {}}}}2.1.5代码运行截图图 22.2第二阶段2.2.1需求分析明确问题定义:首先需要明确问题的背景和涉及的实体,例如旅行者、手电筒、桥等。

同时,需要确定问题的目标,即如何让所有人尽快过桥。

确定约束条件:根据问题的描述,我们知道有一些约束条件,例如每个人过桥的速度不同,手电筒不能扔掉,只能两个人同时过桥等。

这些约束条件将影响解决方案的设计。

分析时间需求:由于目标是尽快让所有人过桥,因此需要分析每个人过桥所需的时间。

这将影响如何分配手电筒和如何安排过桥的顺序。

制定策略:基于上述分析,需要制定一个有效的策略来最大化过桥的速度。

这可能涉及到如何分配手电筒,如何安排过桥的顺序,以及如何返回等。

评估和优化:最后,需要对所制定的策略进行评估和优化。

这可能涉及到对策略的模拟、测试和比较,以便找到最优的解决方案。

2.2.2设计思路这是一个经典的过桥问题,通常称为“蒙提霍尔问题”。

在这个问题中,目标是让所有人尽快过桥。

根据题目的条件,每个人单独过桥的时间是已知的,但是两个人一起过桥的时间是较慢的那个人所需的时间。

集成电路原理答案1. CMOS工艺是目前集成电路制造中使用广泛的一种工艺。

CMOS是互补型金属氧化物半导体的缩写,它由P型和N型晶体管组成。

P型晶体管通过控制基极电压进行工作,而N型晶体管则通过控制栅极电压进行工作。

CMOS工艺具有低功耗、高浮点性能和抗干扰等优点。

2. 集成电路的制造过程通常包括晶片制备、晶圆切割、芯片封装和测试等环节。

晶片制备是指将半导体材料(通常是硅)加工成具有特定功能的晶片。

晶圆切割是将大片的晶圆切割成一颗颗独立的芯片。

芯片封装是将芯片封装在塑料或陶瓷封装体中,以便安装在电路板上。

测试是对芯片进行功能和质量的检测,确保芯片能正常工作。

3. 集成电路的原理是基于电子器件的原理。

常见的电子器件包括二极管、三极管和晶体管等。

二极管是一种具有两个电极的电子器件,它能够只允许电流在一个方向上通过。

三极管是一种具有三个电极的电子器件,由两个PN结构组成。

晶体管是一种能够控制电流的电子器件,它通过调节输入电压来改变输出电流的大小。

4. 集成电路的设计中,逻辑门是最基本的组成单元。

逻辑门用于实现不同的逻辑功能,如与门、或门和非门等。

与门输出只有在所有输入都为高电平时才为高电平,或门输出只要有一个输入为高电平就为高电平,非门的输出与输入相反。

通过逻辑门的组合,可以构建复杂的电路功能,如加法器、多路选择器和计数器等。

5. 集成电路的应用非常广泛,涵盖了电子设备的各个领域。

常见的应用包括计算机、通信、医疗设备、汽车电子和消费电子等。

计算机中的处理器、存储器和各种接口芯片都是集成电路的应用。

在通信领域,集成电路用于实现无线通信、数据传输和网络设备等。

医疗设备中的心脏起搏器、血压计和体温计等也需要集成电路来完成各种功能。

6. 集成电路技术的发展是随着摩尔定律的提出而加速的。

摩尔定律指出,集成电路中的晶体管数量将每隔18-24个月翻一番,而成本将减少一半。

摩尔定律的实现需要不断提升晶体管的集成度和性能,以及改进制造工艺和材料。

1、MOS集成电路的加工包括哪些基本工艺?各有哪些方法和工序?答:(1)热氧化工艺:包括干氧化法和湿氧化法;(2)扩散工艺:包括扩散法和离子注入法;(3)淀积工艺:化学淀积方法:1 外延生长法;2 热CVD法;3 等离子CVD 法;物理淀积方法:1 溅射法;2 真空蒸发法(4)光刻工艺:工序包括:1 涂光刻胶;2 预烘干;3 掩膜对准;4 曝光;5 显影;6 后烘干;7 腐蚀;8 去胶。

2、简述光刻工艺过程及作用。

答:(1)涂光刻胶:为了增加光刻胶和硅片之间的粘附性,防止显影时光刻胶的脱落,以及防止湿法腐蚀产生侧向腐蚀;(2)预烘干:以便除去光刻胶中的溶剂;(3)掩膜对准:以保证掩模板上的图形与硅片上已加工的各层图形套准;(4)曝光:使光刻胶获得与掩模图形相同的感光图片;(5)显影:将曝光后的硅片浸泡在显影液中,使正光刻胶的曝光部分和负光刻胶的未曝光部分被溶解掉;(6)后烘干:使残留在光刻胶中的有机溶剂完全挥发掉,提高光刻胶和硅片的粘接性及光刻胶的耐腐蚀性;(7)腐蚀:以复制在光刻胶上图形作为掩膜,对下层材料进行腐蚀,将图形复制到下层材料中;(8)去胶:除去光刻胶。

3、说明MOS晶体管的工作原理答:MOS晶体管有四种工作状态:(1)截止状态:即源漏之间不加电压时,沟道各电场强度相等,沟道厚度均匀,S、D之间没有电流I ds=0;(2)线性工作状态:漏源之间加电压Vds时,漏端接正,源端接负,沟道厚度不再均匀,在D端电位升为V d,栅漏极电位差为Vgs-Vtn,电场强度变弱,反型层变薄,并在沟道上产生由D到S的电场E ds,使得多数载流子由S端流向D端形成电流I ds,它与V ds变化呈线性关系:I ds=βn[(V gs-V tn)-V ds/2]V ds(3)饱和工作状态:Vs继续增大到V gs-V tn时,D端栅极与衬底不足以形成反型层,出现沟道夹断,电子运动到夹断点V gs-V ds=V tn时,便进入耗尽区,在漂移作用下,电子被漏极高电位吸引过去,便形成饱和电流,沟道夹断后,(V gs-V tn)不变,I ds 也不变,即MOS工作进入饱和状态,I ds=V gs-V tn/R c(4)击穿状态:当Vds增加到一定极限时,由于电压过高,晶体管D端得PN结发生雪崩击穿,电流急剧增加,晶体管不能正常工作。

北京大学信息学院考试试卷装订线内请勿答题考试科目:模拟集成电路原理与设计 考试时间:专业级班主讲教师___________姓名学号________________题号一 二 三 四 五 六 七 总分得分说明:各MOSFET均工作在饱和区,除非另做说明。

1、电路如图1所示,图中各晶体管均工作于饱和区。

使用各晶体管的g m、r o(如M1的g m、r o表示为g m1、r o1)表示电路的R out。

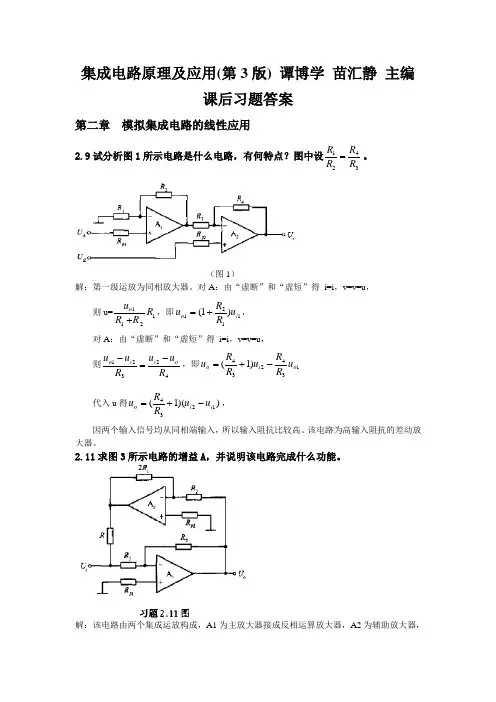

(10分)图1解:133o o m OUT r r g A R ⋅⋅≈而A 即为点X 到点P 的增益:15OUT m R g A ⋅=很容易求得此折叠共源共栅放大器(辅助放大器)的输出阻抗为:()()[]95771311111||||o o o m o o m OUT r r r g r r g R ⋅⋅≈最终总的输出阻抗等于:()([]{}95771311115133133||||o o o m o o m m o o m o o m OUT r r r g r r g g r r g r r g A R ⋅⋅⋅⋅=)⋅⋅=2、 计算如图2电路的增益。

(15分)图2解:此电路当中,电阻Rf 检测输出电压并向X 节点返回一个逾七成正比的电流,因此这种反馈可以看作是电压—电流型。

通过诺顿等效来代替Vin 和Rs 如下图左,并把Rs 看作是主放大器的输入电阻,断开环路如下图右,忽略沟道长度调制效应的影响,则开环增益为:()(F D m F S openINOUTOPEN O R R g R R I V R ||||,⋅⋅−==)这里S IN IN R V I ⋅=,电路的环路增益为。

且由于反馈网络仅由Rf 组成,OPEN O R Y ,21FR Y 121−=。

因此,电路的电压增益等于:()()()()F S S m F D F D m F S F IN OUT R R R g R R R R g R R R V V +⋅⋅+⋅⋅⋅−=/||1||||13、 某电路的传输函数如下式所示,其中21p p ωω<<。

目录一、填空题(每空1分,共24分) (1)二、判断题(每小题1.5分,共9分) (1)三、简答题(每小题4分,共28分) (2)四、计算题(每小题5分,共10分) (4)五、综合题(共9分) (5)一、填空题(每空1分,共24分)1.制作电阻分压器共需要三次光刻,分别是电阻薄膜层光刻、高层绝缘层光刻和互连金属层光刻。

2.集成电路制作工艺大体上可以分成三类,包括图形转化技术、薄膜制备技术、掺杂技术。

3.晶体中的缺陷包括点缺陷、线缺陷、面缺陷、体缺陷等四种。

4.高纯硅制备过程为氧化硅→粗硅→ 低纯四氯化硅→ 高纯四氯化硅→ 高纯硅。

5.直拉法单晶生长过程包括下种、收颈、放肩、等径生长、收尾等步骤。

6.提拉出合格的单晶硅棒后,还要经过切片、研磨、抛光等工序过程方可制备出符合集成电路制造要求的硅衬底片。

7.常规的硅材料抛光方式有:机械抛光,化学抛光,机械化学抛光等。

8.热氧化制备SiO2的方法可分为四种,包括干氧氧化、水蒸汽氧化、湿氧氧化、氢氧合成氧化。

9.硅平面工艺中高温氧化生成的非本征无定性二氧化硅对硼、磷、砷(As)、锑(Sb)等元素具有掩蔽作用。

10.在SiO2内和Si- SiO2界面存在有可动离子电荷、氧化层固定电荷、界面陷阱电荷、氧化层陷阱等电荷。

11.制备SiO2的方法有溅射法、真空蒸发法、阳极氧化法、热氧化法、热分解淀积法等。

12.常规平面工艺扩散工序中的恒定表面源扩散过程中,杂质在体内满足余误差函数分布。

常规平面工艺扩散工序中的有限表面源扩散过程中,杂质在体内满足高斯分布函数分布。

13.离子注入在衬底中产生的损伤主要有点缺陷、非晶区、非晶层等三种。

14.离子注入系统结构一般包括离子源、磁分析器、加速管、聚焦和扫描系统、靶室等部分。

15.真空蒸发的蒸发源有电阻加热源、电子束加热源、激光加热源、高频感应加热蒸发源等。

16.真空蒸发设备由三大部分组成,分别是真空系统、蒸发系统、基板及加热系统。

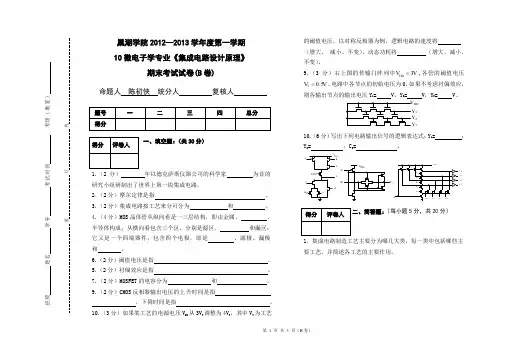

电科《集成电路原理》期末考试试卷一、填空题1.(1分) 年,第一次观测到了具有放大作用的晶体管。

2.(2分)摩尔定律是指 。

3.集成电路按工作原理来分可分为 、 、 。

4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。

5.(4分)MOSFET 可以分为 增强型NMOS ,耗尽型NMOS ,增强型PMOS ,耗尽型PMOS___四种基本类型。

6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。

7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 栅极, 和 漏极 ; VDD , 作为PMOS 的源极和体端, ,GND 作为NMOS 的源极和体端。

8.(2分)CMOS 逻辑电路的功耗可以分为 和 。

9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= 4 V ,Y 2= 3 V ,Y 3= 3 V 。

DD 13210.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。

AB Y 1AB23二、画图题:(共12分)1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CD=+的电路图,要求使用的MOS管最少。

2.(6分)用动态电路级联实现逻辑功能Y ABC=,画出其相应的电路图。

三、简答题:(每小题5分,共20分)1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么?2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么?3.简述静态CMOS电路的优点。

4.简述动态电路的优点和存在的问题。

四、分析设计题:(共38分1.(12分)考虑标准0.13m μ CMOS 工艺下NMOS 管,宽长比为W/L=0.26/0.13m m μμ,栅氧厚度为2.6ox t nm =,室温下电子迁移率2220/n cm V s μ=,阈值电压T V =0.3V,计算 1.0GS V =V 、0.3DS V =V 和0.9V 时D I 的大小。

已知:148.8510/o F cm ε-=⨯, 3.9ox ε=。

2.(12分)如图所示,M1和M2两管串联,且B G T A V V V V <-<,请问: 1) 若都是NMOS ,它们各工作在什么状态? 2) 若都是PMOS ,它们各工作在什么状态?3) 证明两管串联的等效导电因子是eff K =1212/()K K K K +。

3.(14分)设计一个CMOS 反相器,要求在驱动10fF 外部负载电容的情况下,输出上升时间和下降时间都不能大于40ps ,并要求最大噪声容限不小于0.55V 。

针对0.13m μ工艺,已知:0.30TN V V =,0.28TP V V =-,2220/n cm V s μ=,276/p cm V s μ=, 2.6ox t nm =,148.8510/o F cm ε-=⨯, 3.9ox ε=, 1.2DD V V =,ln14.33=2.66,ln14=2.64。

《集成电路原理》期末考试试卷 参考答案一、填空题:(共30分)1.(1分)1947 2.(2分)集成电路中的晶体管数目(也就是集成度)大约每18个月翻一番 3.(3分)数字集成电路,模拟集成电路,数模混合集成电路 4.(4分)曝光,显影,坚膜,刻蚀 5.(4分)增强型NMOS ,耗尽型NMOS ,增强型PMOS ,耗尽型PMOS 6.(3分)栅电极材料,栅氧化层的质量和厚度,衬底掺杂浓度 7.(2分)栅极,漏极,VDD ,GND 8.(2分)动态功耗,静态功耗 9.(3分)4,3,2 10.(6分)()A B C D ++,AB AB +,AB C +二、画图题:(共12分)1.(6分) 2.(6分)Y3三、简答题:(每小题5分,共20分)1.答:n 阱CMOS 的制作工艺流程:1.准备硅片材料;2.形成n 阱;3.场区隔离;4.形成多晶硅栅;5.源漏区n+/p+注入;6.形成接触孔;7.形成金属互连;8.形成钝化层。

n 阱的作用:作为PMOS 管的衬底,把PMOS 管做在n 阱里。

2.答:场区氧化的作用:隔离MOS 晶体管。

LOCOS 工艺的缺点:会形成鸟嘴,使有源区面积比版图设计的小。

更好的隔离方法:浅槽隔离技术。

3.答:1.是一无比电路,具有最大的逻辑摆幅;2.在低电平状态不存在直流导通电流;3.静态功耗低;4.直流噪声容限大;5.采用对称设计获得最佳性能。

4.答:动态电路的优点:1.减少了MOS 管数目,有利于减小面积;2.减小了电容,有利于提高速度;3.保持了无比电路的特点。

动态电路存在的问题:1.靠电荷存储效应保存信息,影响电路的可靠性;2.存在电荷分享、级联、电荷泄漏等问题;3.需要时钟信号控制,增加设计复杂性。

四、分析设计题:(共38分)1.(12分)解:计算MOSFET 导电因子β:142073.98.85100.26()()220584.1()2.6100.13ox n ox n ox W W C A V L t L εεβμμμ---⨯⨯===⨯⨯=⨯ 4分 当 1.0GS V =V(>T V =0.3V)、0.3DS V =V(<0.7GS T V V V -=)时,NMOS 管处于线性区,线性区电流为:21[()]96.3765()2D GS T DS DS I V V V V A βμ=--= 4分当 1.0GS V =V(>T V =0.3V)、0.9DS V =V(>0.7GS T V V V -=)时,NMOS 管处于饱和区,饱和区电流为:2()143.1045()2D GS T I V V A βμ=-= 4分2.(12分)解:1) 设中间节点为C 。

分析知当电压满足V B < V G - V T < V A 时,在电路达到稳态之后,M1和M2都导通。

于是对M1而言,有GS V 0T V ->,即 Vc < V G -V T 。

又V G - V T < V A ,即GS V DS T V V >-,故M1工作于饱和区。

而对M2而言,有GS V T DS V V ->,故M2工作于线性区。

3分 2) 依据NMOSFET 和PMOSFET 的电压反转对称性知,若两管都是PMOSFET ,则M1工作于线性区,M2工作于饱和区。

3分3) 取一例证明。

以此题中的NMOSFET 和给定的偏压为例,两个NMOS 管等效为一个NMOS 管后,依V B < V G - V T < V A 知该等效管应工作于饱和区。

故对M1、M2和等效管Meff 有:21122222()[()()]()D G T C D G T B G T C Deff eff G T B I K V V V I K V V V V V V I K V V V ⎧=--⎪=-----⎨⎪=--⎩则有1212DeffD D effI I I K K K +=由1D I =2D I =Deff I 知: 12111eff K K K += 即K eff = K 1 K 2 / (K 1 + K 2) 6分3.(14分)解:先考虑瞬态特性要求:由()20.1 1.9212(1)0.1(1)0.280.2331.2ln TPPDDPPPPLP DDr r C r K V V V t αααααττ----=-=+===⎧⎡⎤⎪⎣⎦⎪⎪⎨⎪⎪⎪⎩()20.1 1.9212(1)0.1(1)0.30.251.2ln TNNDDNNNNLN DDf f C f K VV V t αααααττ----=-=+===⎧⎡⎤⎪⎣⎦⎪⎪⎨⎪⎪⎪⎩(4分)得424.0810/PKA V-=⨯,424.2210/NKA V-=⨯ (2分)而0OXOX11()()2211()()22OXPPPPPOXOXNNnNnOXWWK C LL tWWK C LL tεεμμεεμμ====⎧⎪⎪⎨⎪⎪⎩(2分)代入相关参数可得()8.09() 2.89PNW LW L==⎧⎪⎨⎪⎩,即{1.0520.376PNm mWWμμ== (2分)考察噪声容限:由it0.607V V == (2分)得:{0.6070.550.5930.55NLMitNLMDDitVV V VVV V V V==>=-=> (2分)所以所设计的CMOS 反相器符合题意要求,即{1.0520.376PNm mWWμμ==。