版图技术——CMOS集成电路版图设计

- 格式:ppt

- 大小:811.50 KB

- 文档页数:58

CMOS数字集成电路设计流程一、介绍CMOS数字集成电路设计是现代电子工程中的重要分支之一,涉及到数字逻辑、电子设计自动化、半导体器件物理和工艺等多个领域。

在数字集成电路的设计流程中,工程师需要进行功能分析、设计规划、逻辑综合、电路布局、版图设计、物理验证和后仿真等多个环节。

本文将就CMOS数字集成电路设计流程的各个环节进行详细介绍。

二、功能分析在进行CMOS数字集成电路设计之前,工程师需要首先完成功能分析。

在功能分析阶段,工程师需要明确电路的功能需求,包括各种逻辑门、寄存器、存储器等组件的功能与接口要求。

还需要对设计的电路进行规模估计,明确设计的规模和复杂度,为后续的设计规划和逻辑综合提供依据。

三、设计规划在完成功能分析之后,工程师需要进行设计规划。

设计规划阶段需要明确设计的总体结构、数据传输路径、时钟和控制信号的分配等。

还需要进行功耗和面积的预估,并确定设计的性能指标和约束条件等。

四、逻辑综合逻辑综合是数字集成电路设计的重要环节之一。

在逻辑综合过程中,工程师需要将设计的功能描述转换为门级网表,然后进行优化,包括面积优化、功耗优化、时序优化等。

逻辑综合的结果将是门级网表,为后续的电路布局和版图设计提供基础。

五、电路布局电路布局是数字集成电路设计的关键环节之一。

在电路布局过程中,工程师需要将逻辑综合的门级网表映射到物理结构上,并进行布线和布局设计。

电路布局需要考虑电路的面积、功耗、时序等多个方面的优化,并确保电路的稳定性和可靠性。

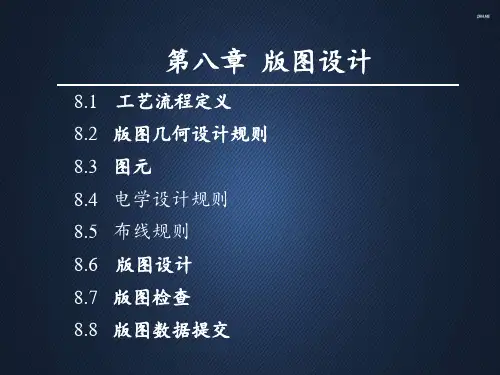

六、版图设计版图设计是数字集成电路设计中的重要环节之一。

在版图设计过程中,工程师需要将电路布局转换为实际的版图,并进行细化设计,包括晶体管布局、金属线路设计、接口电路设计等。

版图设计需要满足工艺规则和制约条件,确保设计的可制造性和可测试性。

七、物理验证物理验证是数字集成电路设计中不可或缺的一环。

在物理验证过程中,工程师需要进行电路的各种仿真和验证工作,包括静态时序分析、动态时序分析、功耗分析、布局抽取等。

第5章CMOS版图设计5.1 版图设计基本概念5.2 设计规则5.3 基本工艺层版图5.4 FET版图尺寸的确定5.5 逻辑门的版图设计5.6标准单元版图5.7 设计层次化2/783/785.1 版图设计基本概念⏹什么是版图设计?☐Layout design :定义各工艺层图形的形状、尺寸以及不同工艺层的相对位置。

⏹版图设计的内容☐布局:就是将组成集成电路的各部分合理地布置在芯片上。

安排各个晶体管、基本单元、复杂单元在芯片上的位置。

☐布线:就是按电路图给出的连接关系,在版图上布置元器件之间、各部分之间的连接。

设计走线,实现管间、门间、单元间的互连。

☐尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(宽度)以及晶体管与互连之间的相对尺寸等。

4/78⏹版图设计的目标☐满足电路功能、性能指标、质量要求☐尽可能节省面积,以提高集成度,降低成本☐尽可能缩短连线,以减少复杂度,缩短延时、改善可靠性5/78EDA工具的作用(EDA: Electronic Design Automation)⏹版图编辑☐规定各个工艺层上图形的形状、尺寸、位置(Layout Editor)⏹规则检查☐版图与电路图一致性检查(LVS,Layout VersusSchematic)☐设计规则检查(DRC,Design Rule Checker)☐电气规则检查(ERC,Electrical Rule Checker)⏹布局布线☐Place and route,自动给出版图布局与布线6/787/78电路图与版图一致性检查(LVS )从版图中提取的电路同原电路相比较,其方法通常是将两者的网表进行对比。

比较的结果,可以是完全一致或两者不全一致,设计者应对所示的错误进行必要的版图修改。

电路图与版图一致性检查(LVS: Layout Versus Schematic )设计规则检验(DRC:Design Rule Check)设计规则检查是一个运用版图数据库检查在版图上涉及的每条设计规则的程序。

![毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]](https://uimg.taocdn.com/15f996a177232f60dccca185.webp)

目录摘要 (3)第一章引言 (3)§ (3)§ CMOS 电路的发展和特点 (5)第二章CMOS运算放大器电路图 (8)§Pspice软件介绍 (8)Pspice运行环境 (12)Pspice功能简介 (12)§CMOS运算放大器电路图的制作 (14)§小结 (20)第三章版图设计 (20)§L-EDIT软件介绍 (20)§设计规则 (21)§集成电路版图设计 (24)PMOS版图设计 (24)NMOS版图设计 (27)CMOS运算放大器版图设计 (27)优化设计 (32)第四章仿真 (40)§DRC仿真 (41)§LVS 对照 (42)第五章总结 (48)附录 (50)参考文献 (52)致谢 (53)摘要介绍了CMOS运算放大电路的版图设计。

并对PMOS、NMOS、CMOS运算放大器版图、设计规则做了详细的分析。

通过设计规则检查(DRC)和版图与原理图对照(LVS)表明,此方案已基本达到了集成电路工艺的要求。

关键词:CMOS 放大器 NMOS PMOS 设计规则检查版图与原理图的对照AbstractThe layout desigen of CMOS operation amplifer is presented in this the layouts and design rules of PMOS,NMOS, and CMOS operation amplifer. The results of design rule check(DRC)and layout verification schmatic(LVS) shown that the project have already met to the needs of IC fabricated processing. Keywords: CMOS Amplifer NMOS PMOS DRC LVS第一章引言1.1 集成电路版图设计的发展现状和趋势集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

CMOS模拟集成电路版图设计课程大纲第一讲CMOS模拟集成电路版图基础⏹CMOS模拟版图概述⏹CMOS模拟集成电路版图的定义⏹CMOS模拟集成电路版图设计流程❑版图规划❑版图设计实现❑版图验证❑版图完成⏹CMOS模拟集成电路版图设计工具第二讲模拟集成电路版图器件与互连⏹概述⏹器件❑MOS管❑电阻❑电容❑电感❑三极管⏹互连❑金属(第一层金属,第二层金属……)❑通孔第三讲寄生参数⏹概述⏹寄生电容⏹线电阻压降(IR drop)⏹寄生电感⏹连线寄生模型⏹MOS管寄生效应第四讲器件匹配⏹概述⏹指状交叉法线⏹共质心法⏹虚拟器件⏹MOS晶体管匹配⏹电阻匹配⏹电容匹配⏹差分线布线⏹器件匹配总则第五讲设计规则⏹概述⏹工艺库中各类器件的层信息⏹设计规则细则⏹工业标准的基本数据格式第六讲验证⏹设计规则检查(DRC)Design Rule Check⏹版图与电路图的对照(LVS)Layout Versus Schematic⏹电气规则检查(ERC)Electrical Rule Check⏹天线规则检查(ANT)⏹静电放电检查(ESD)第七讲可靠性设计⏹天线效应⏹闩锁效应⏹静电放电保护(Electro-Static Discharge ,ESD)⏹数模混合集成电路版图设计第八讲工艺设计工具包(PDK)⏹ 1.PDK名称的涵义⏹ 2.PDK中包含的内容● 2.1 IO lib2.1.1 GDS文件的导入操作2.1.2 网表导入2.1.3 IO使用文档介绍● 2.2 SMIC_13_PDK_v2.6_20142.2.1 Smic13mmrf_1233文件夹2.2.2 model 文件夹2.2.3 Calibre 文件夹● 2.3 SMIC_13_TF_LG_LIST_2014122.3.1 Standard cell Timing lib2.3.2 Calview.cellmap2.3.3 Standard cell netlist及网表导入操作2.3.4 Ant rule (天线规则)第九讲Cadence spectre概述与操作界面⏹Cadence spectre 概述⏹Cadence spectre的特点⏹Cadence spectre的仿真设计方法⏹Cadence spectre与其他EDA软件的连接⏹Cadence spectre的基本操作第十讲Spectre窗口和库元件⏹模拟设计环境(Analog Design Environment)⏹波形显示窗口(Waveform)⏹波形计算器(Waveform Calculator)⏹Spectre库中的基本器件第十讲Cadence Virtuoso版图设计工具⏹Cadence Virtuoso概述⏹Virtuoso 界面介绍⏹Virtuoso 基本操作第十一讲Mentor Calibre版图验证工具⏹Mentor Calibre版图验证工具概述⏹Mentor Calibre版图验证工具调用⏹Mentor Calibre DRC验证⏹Mentor Calibre LVS验证⏹Mentor Calibre寄生参数提取(PEX)第十二讲版图设计与验证流程实例⏹设计环境准备⏹反相器链电路的建立和前仿真⏹反相器链版图设计⏹反相器链版图验证与参数提取⏹反相器链电路后仿真⏹输入输出单元环设计⏹主体电路版图与输入输出单元环的连接⏹导出GDSII文件。

目录摘要 (3)绪论 (5)1软件介绍及电路原理 (6)1.1软件介绍 (6)1.2电路原理 (6)2原理图绘制 (8)3电路仿真 (10)3.1瞬态仿真 (10)3.2直流仿真 (11)4版图设计及验证 (12)4.1绘制反相器版图的前期设置 (12)4.2绘制反相器版图 (13)4.3 DRC验证 (15)结束语 (17)参考文献 (18)摘要CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

本文将简单的介绍基于ORCAD和L-EDIT的CMOS反相器的电路仿真和版图设计,通过CMOS反相器的电路设计及版图设计过程,我们将了解并熟悉集成电路CAD的一种基本方法和操作过程。

关键词:CMOS反相器ORCAD L-EDIT版图设计AbstractThe huge development potential of CMOS technology itself is the foundation of sustainable development of IC high speed. The manufacturing level of development of the integrated circuit to the deep sub micron technology, CMOS low power consumption, high speed and high integration have been fully reflected. In this paper, the circuit simulation and layout design of ORCAD and L-EDIT CMOS inverter based on simple introduction, through the circuit design and layout design process of CMOS inverter, we will understand and a basic method and operation process, familiar with IC CAD.Keywords: CMOS inverter layout ORCAD L-EDIT绪论20世纪是IC迅速发展的时代。