Quartus II 时钟约束概念

- 格式:doc

- 大小:182.00 KB

- 文档页数:16

Quartus II 学习笔记时钟部分:1.clock skew时钟偏斜,指同一个时钟源到达不同寄存器时钟端的时间的差别。

主要原因在于时钟路径到达不同的寄存器的长度不同。

FPGA有全铜层的全局时钟网络驱动,全局时钟的CLOCK SKEW很小。

2. 全局时钟设置:Assignments---setting---Analysis&Synthesis Setting的Fitter Setting的More setting 里AUTO Global Clock.选中的话会在布线时,自动把一些高扇出的时钟信号走到全局网络上,则可以显著提高这些扇出结点的性能,同时也节省了普通的布线资。

“AUTO Global Register Control Signals”选项打开,那么会把高扇出的寄存器控制信号走到全局网络上,包括请零和复位和时钟使能等。

用户可以通过QUARTUS 的Assignments ---setting来对内部走线进行增加约束,决定是否让其走到全局网络上,详细部分参考《ALTERA FPGA/CPLD设计(高级篇)》的第2章的时序问题。

3. 当我在这些寄存器间再添加一级寄存器做流水线优化,并且需要在Quartus II 的Synthesis Netlist Optimizations设置选项中,使能PeRForm gate-level register retiming;同时在Quartus II的Physical Synthesis Optimizations设置选项中,使能Perform register duplication和Perform register retiming两个选项,Quartus会自动优化寄存器间的组合逻辑。

语法部分:signal state:integer range 0 to 4;q <= (others => 0) :把信号q所有的位赋值library ieee;use ieee.std_logic_1164.all;use ieee.std_unsigned.all;use ieee.std_numeric.all;实现+和-的操作在vhdl语句中,如果if 语句包含对两个时钟上升沿的检测,比如说底下p1 程序中clk1,clk2的情况.那么quartusii软件是无法综合该语句的。

Quartus使用问题及解决方法总结(转载)在QuartusII下进行编译和仿真的时候,会出现一堆warning,有的可以忽略,有的却需要注意,虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚,大家群策群力,把自己知道和了解的一些关于警告的问题都说出来讨论一下,免得后来的人走弯路.下面是我收集整理的一些,有些是自己的经验,有些是网友的,希望能给大家一点帮助,如有不对的地方,请指正,如果觉得好,请版主给点威望吧,谢谢1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated value with size <number> to match size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

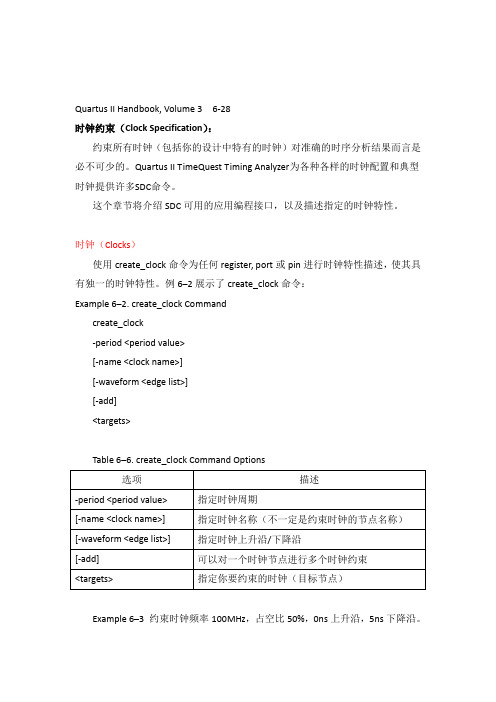

Quartus II Handbook, Volume 3 6-28时钟约束(Clock Specification):约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。

Quartus II TimeQuest Timing Analyzer为各种各样的时钟配置和典型时钟提供许多SDC命令。

这个章节将介绍SDC可用的应用编程接口,以及描述指定的时钟特性。

时钟(Clocks)使用create_clock命令为任何register, port或pin进行时钟特性描述,使其具有独一的时钟特性。

例6–2展示了create_clock命令:Example 6–2. create_clock Commandcreate_clock-period <period value>[-name <clock name>][-waveform <edge list>][-add]<targets>Table 6–6. create_clock Command OptionsExample 6–3 约束时钟频率100MHz,占空比50%,0ns上升沿,5ns下降沿。

Example 6–3. 100MHz Clock Creationcreate_clock –period 10 –waveform { 0 5 } clkExample 6–4和上例相差90度的相位。

Example 6–4. 100MHz Shifted by 90 Degrees Clock Creationcreate_clock –period 10 –waveform { 2.5 7.5 } clk_sys使用create_clock命令约束时钟缺省的source Latency值为0。

Quartus II TimeQuest Timing Analyzer自动为非虚拟时钟(non-virtual clocks)计算时钟网络延时(clock’s network latency)。

QuartusII 中Tsu/Tco 的约束方法

Tsu/Tco 在Quartus II 的报告中有两种不同含义.

1. 片内的Tsu/Tco 是指前级触发器的Tco 和后级触发器的Tsu, 一般来说都是几百ps 级别的. 可以通过List Paths 命令查看。

这里的Tsu/Tco 主要由器件工艺决定, 工作时在受到温度,电压的影响略有变化.(如下图所示)

2. 管脚上的Tsu/Tco 它是保证系统Famx 重要的TIming 元素(如下图示). 比如: 两个芯片之间工作在100MHZ, 因为100M 的周期为10ns, (现忽略PCB 走线的延迟), 如果某信号对FPGA 来说是输入, 那幺前级芯片的Tco 加上FPGA 的Tsu 就不能够超过10ns. 如果某信号对于FPGA 来说是输出,那幺FPGA 的Tco 加上后级芯片的Tsu 也不能够超过10ns. 只有这样,。

quaruts 时序约束English Answer:Quarts Timing Constraints.Quartus Prime timing constraints drive the Quartus Prime timing analyzer engine to achieve fast and accurate timing analysis results. Timing constraints specify the timing relationships and requirements between different parts of the design. These constraints can be applied to clocks, registers, I/O ports, and other design components.Quartus Prime supports two main types of timing constraints:Static timing constraints (STCs) specify absolute timing relationships between two points in the design. For example, you can use STCs to specify the maximum or minimum time between a clock edge and a register setup time.Dynamic timing constraints (DTCs) specify timing relationships between two points in the design that may change over time. For example, you can use DTCs to specify the maximum or minimum time between a clock edge and a register setup time when the clock frequency is changing.Quartus Prime Timing Constraints Syntax.The syntax for timing constraints in Quartus Prime isas follows:<constraint_type> <constraint_name> <constraint_value>。

关于quartus ii时序约束(1)2012-06-17 09:46:07| 分类:默认分类|举报|字号订阅一直以来都只是简单地理解了一下关于时序约束的内容,而工具也有默认classic的约束,加上目前的设计对时序没有很高的要求,所以就一直都没真正地自己做过一次约束,但是我知道,这部分是不可以跳过的,这部分也算是搞FPGA必须掌握的内容。

今天下午对这部分进行了初次探究,收获有如下:常用的约束有三种:1.时序约束2.区域约束3.位置约束时序约束的作用有:1.提高设计的工作频率2.获得正确的时序分析报告需要复习前面博文《FPGA学习之时序分析基础(7)》记住,堵塞原则是HDL语言的精髓,也就是说触发器是有延时作用的,虽然两个触发器使用的是同一个时钟,但是当第二个触发器接收第一帧数据的时候第一个触发器在发第二帧数据,而当第二个触发器接收第二帧数据的时候第一个触发器在发第三帧数据,依此类推,也就是说每一帧数据在两个触发器之间都有一个clk的时间前进,如果前进的时间太长,也即是系统给的时钟太快,就会出现无法满足第二个触发器setup的时间。

setup time 就是第二个触发器在接收到由第一个触发器上一个时钟发送的数据之前应空闲的时间。

公式:CLK+TCLK2-Tsu > Tclk1 + Tcd + Tdata所以系统CLK是和Tsu息息相关的,所以看时序报告的时候也是从Clock Setup‘clk’看最差路径等信息。

在FPGA设计工具中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑。

通常,需要对这几种路径分别进行约束,以便使设计工具能够得到最优化的结果。

下面对这几种路径分别进行讨论。

1. 从输入端口到寄存器:这种路径的约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。

Quartus II Handbook, Volume 3 6-28时钟约束(Clock Specification):约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。

Quartus II TimeQuest Timing Analyzer为各种各样的时钟配置和典型时钟提供许多SDC命令。

这个章节将介绍SDC可用的应用编程接口,以及描述指定的时钟特性。

时钟(Clocks)使用create_clock命令为任何register, port或pin进行时钟特性描述,使其具有独一的时钟特性。

例6–2展示了create_clock命令:Example 6–2. create_clock Commandcreate_clock-period <period value>[-name <clock name>][-waveform <edge list>][-add]<targets>Table 6–6. create_clock Command OptionsExample 6–3 约束时钟频率100MHz,占空比50%,0ns上升沿,5ns下降沿。

Example 6–3. 100MHz Clock Creationcreate_clock –period 10 –waveform { 0 5 } clkExample 6–4和上例相差90度的相位。

Example 6–4. 100MHz Shifted by 90 Degrees Clock Creationcreate_clock –period 10 –waveform { 2.5 7.5 } clk_sys使用create_clock命令约束时钟缺省的source Latency值为0。

Quartus II TimeQuest Timing Analyzer自动为非虚拟时钟(non-virtual clocks)计算时钟网络延时(clock’s network latency)。

Quartus II Handbook, Volume 3 6-29生成时钟(Generated Clocks)Quartus II TimeQuest Timing Analyzer可以把修改或改变主时钟(或者引入时钟)特性的分频时钟、波纹时钟和电路作为生成时钟。

你可以定义这些电路的输出作为生成时钟。

这些定义可以让Quartus II TimeQuest Timing Analyzer分析这些时钟以及关联的时钟网络延时(network latency)。

使用create_generated_clock命令定义生成时钟。

Example 6–5. create_generated_clock Commandcreate_generated_clock[-name <clock name>]-source <master pin>[-edges <edge list>][-edge_shift <shift list>][-divide_by <factor>][-multiply_by <factor>][-duty_cycle <percent>][-add][-invert][-master_clock <clock>][-phase <phase>][-offset <offset>]<targets>Table 6–7. create_generated_clock Command Options源延时是由于从主时钟(不一定是主管脚)开始的时钟网络延时所致。

你可以使用set_clock_latency –source命令约束源延时。

Figure 6–17 展示了如何产生一个基于10ns时钟的反向生成时钟:Figure 6–17. Generating an Inverted Clockcreate_clock -period 10 [get_ports clk]create_generated_clock -divide_by 1 -invert -source [get_registers clk] \[get_registers gen|clkreg]Figure 6–18 展示了如何使用-edges和-edge_shift选项以改变生成时钟。

Figure 6–18. Edges and Edge Shifting a Generated Clockcreate_clock -period 10 -waveform { 0 5} [get_ports clk]# Creates a divide-by-t clockcreate_generated_clock -source [get_ports clk] -edges {1 3 5 } [get_registers \ clkdivA|clkreg]# Creates a divide-by-2 clock independent of the master clocks’ duty cycle (now 50%)create_generated_clock -source [get_ports clk] -edges {1 1 5} -edge_shift { 0 2.5 0 } \Figure 6–19 展示了-multiply_by选项对生成时钟的影响。

Figure 6–19. Multiplying a Generated Clockcreate_clock -period 10 -waveform { 0 5 } [get_ports clk]# Creates a multiply-by-2 clockcreate_generated_clock -source [get_ports clk] -multiply_by 2 [get_registers \Quartus II Handbook, Volume 3 6-32虚拟时钟Virtual Clocks虚拟时钟是一个在设计中没有真正源或者说与设计没有直接关系的一个时钟。

例如,如果一个时钟不是设计中的时钟,而仅仅作为一个外部器件的时钟源,并且外部器件和该设计有输入或者输出的管脚,那么就认为这个时钟是虚拟时钟。

使用create_clock命令创造一个虚拟时钟,对源选项没有指定值。

你可以使用set_input_delay和set_output_delay约束虚拟时钟。

Figure 6–20展示了Quartus II TimeQuest Timing Analyzer若要正确的分析外部寄存器和内部设计逻辑之间的关系,在何处需要设置虚拟时钟的实例。

虽然名为virt_clk的晶振没有和Altera器件直接相互作用,但是担当起了外部寄存器的源时钟的角色,所以时钟virt_clk必须申明。

Example 6–6 展示了定义一个周期10ns,名为virt_clk,50%占空比,上升沿在0ns的虚拟时钟的命令。

虚拟时钟用于作为输出延时约束的时钟源。

在你产生虚拟时钟之后,你可以执行register-to-register的分析报告(在Altera 器件和外部器件的寄存器之间)。

Example 6–6. 虚拟时钟Example 1#create base clock for the designcreate_clock -period 5 [get_ports system_clk]#create the virtual clock for the external registercreate_clock -period 10 -name virt_clk -waveform { 0 5 }#set the output delay referencing the virtual clockset_output_delay -clock virt_clk -max 1.5 [get_ports dataout]Example 6–7 展示了产生一个周期为10ns,占空比为50%,相移90度虚拟时钟的命令。

Example 6–7. Virtual Clock Example 2create_clock -name virt_clk –period 10 –waveform { 2.5 7.5 }Quartus II Handbook, Volume 3 6-33多频时钟Multi-Frequency Clocks某些情况下在设计中会有很多个时钟源提供时钟信号。

增加的时钟也许扮演一个低频率低功耗时钟的角色。

在分析这种设计时,create_clock命令提供了–add 选项让你添加多个时钟节点。

Example 6–8展示了时钟周期为10ns的节点clk,然后对同一个节点添加时钟周期为15ns的时钟。

Quartus II TimeQuest Timing Analyzer在执行时序分析时两个时钟都用到了。

Example 6–8. Multi-Frequency Examplecreate_clock –period 10 –name clock_primary –waveform { 0 5 } [get_ports clk] create_clock –period 15 –name clock_secondary –waveform { 0 7.5 } [get_ports clk] -addQuartus II Handbook, Volume 3 6-34自动时钟检测Automatic Clock Detection想要为你的设计中所有的时钟节点自动添加时钟约束,那么就使用derive_clocks命令。

这个命令从管脚或者寄存器生成时钟以确保设计中的每个寄存器都有时钟。

Example 6–9 展示了derive_clocks命令选项。

Example 6–9. derive_clocks Commandderive_clocks[-period <period value>][-waveform <edge list>]Table 6–8 describes the options for the derive_clocks command.derive_clocks命令不能为PLLs输出时钟进行约束。

derive_clocks命令相当于使用create_clock命令为每个寄存器或者管脚产生时钟。