一种高速数据采集系统的研究

- 格式:pdf

- 大小:195.37 KB

- 文档页数:3

一种有效的高速数据采集方式郑利君【摘要】随着电子技术的发展,在智能化系统中要求传送的数据量愈来愈大,速度愈来愈快,所以设计性能优良的高速数据采集电路一直是电子设计中的一个关键技术.给出了利用FPGA实现DMA方式的高速数据采集电路的设计思想,工作原理和实施方案.把FPGA用作DMA控制器、采集控制器和总线控制器.该设计有效地解决了单片机应用领域中速度较慢的CPU和高速的A/D转换器之间的速度配合问题,具有电路设计简单、可靠性高、传输速度快等特点,而且特别适用于采集大量数据的情况.时序仿真和实际应用都证明了设计的正确性,从而解决了在单片机系统中较难解决的问题.【期刊名称】《现代电子技术》【年(卷),期】2006(029)016【总页数】3页(P139-140,144)【关键词】高速数据采集;FPGA;DMA;自动化系统【作者】郑利君【作者单位】浙江工业大学,之江学院,浙江,杭州,310024;浙江理工大学,机控学院,浙江,杭州,310017【正文语种】中文【中图分类】TP272随着电子技术的发展,设计性能优良的高速数据采集电路是电子设计中的一个关键技术。

在高速数据采集系统中,采用指令方式控制A/D转换,或采用直接存储器存取,即DMA(Direct Memory Access)传送方式,或用可编程逻辑阵件FPGA(Field Programmable Gate Array)作为高速数据采集控制器,并将采集的数据存入FPGA内的RAM中,他们都不能解决大量数据的高速数据采集问题。

本文给出一种设计方案,也是利用FPGA作为DMA控制器,采集控制器和总线控制器。

该设计方案不仅在单片机系统中实现了高速数据采集,而且特别适用于采集大量数据的情况,从而解决了在单片机系统中较难解决的问题。

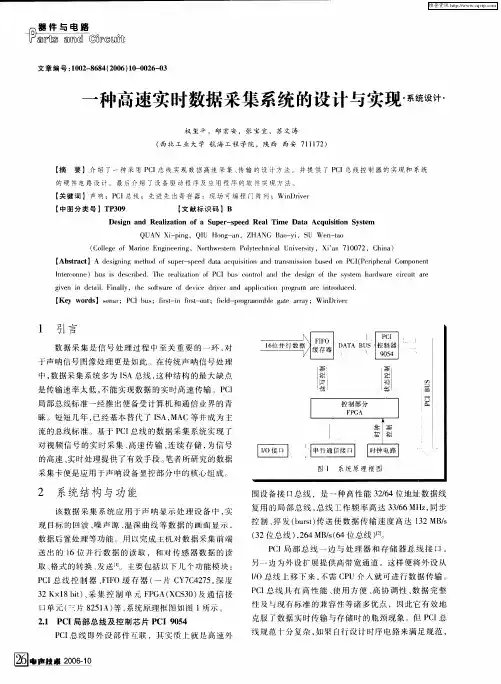

系统总体设计方案如图1所示。

该系统由单片机89C55,FPGA,RAM以及A/D转换器组成(其他外围接口及FPGA重载电路不做分析)。

基于FPGA的高速数据采集系统设计随着科学技术的不断进步,数据采集系统在许多领域都发挥着重要作用。

为了满足高速数据采集的需求,基于现场可编程门阵列(FPGA)的高速数据采集系统设计应运而生。

本文将介绍这一系统的设计原理和关键技术。

首先,我们需要了解FPGA的基本原理。

FPGA是一种可编程的硬件设备,可以根据需要重新配置其内部逻辑电路。

这使得FPGA在数据采集系统中具有极大的灵活性和可扩展性。

与传统的数据采集系统相比,基于FPGA的系统可以实现更高的采样率和更低的延迟。

基于FPGA的高速数据采集系统设计主要包括以下几个关键技术。

首先是模数转换(ADC)技术。

ADC是将连续的模拟信号转换为数字信号的关键环节。

在高速数据采集系统中,需要使用高速、高精度的ADC来保证数据的准确性和完整性。

其次是FPGA内部逻辑电路的设计。

为了实现高速数据采集,需要设计高效的数据处理逻辑电路。

这些电路可以实现数据的实时处理、存储和传输等功能。

同时,还需要考虑电路的时序约束和资源分配等问题,以确保系统的稳定性和可靠性。

另外,时钟同步技术也是高速数据采集系统设计的重要内容。

在高速数据采集过程中,各个模块需要保持同步,以确保数据的准确性。

因此,需要设计合理的时钟同步方案,保证各个模块在同一个时钟周期内完成数据的采样和处理。

最后,还需要考虑系统的接口和通信问题。

基于FPGA的高速数据采集系统通常需要与其他设备进行数据交互,如计算机、存储设备等。

因此,需要设计合适的接口和通信协议,实现数据的传输和存储。

综上所述,基于FPGA的高速数据采集系统设计涉及多个关键技术,包括ADC技术、FPGA内部逻辑电路设计、时钟同步技术以及接口和通信问题。

通过合理的设计和优化,可以实现高速、高精度的数据采集,满足现代科学研究和工程应用的需求。

这将为各个领域的数据采集工作带来巨大的便利和发展空间。

高速公路智能交通系统中的数据采集与处理技术研究高速公路是现代交通体系不可或缺的一环。

而高速公路智能交通系统更是保障公路安全、优化公路运输效率、减少车辆拥堵的重要手段。

其中,数据采集与处理技术是智能交通系统中最为基础和关键的环节。

一、智能交通系统的数据采集智能交通系统中数据的采集,一般采用传感器等设备对公路上的运行情况和车辆信息等进行实时监控和采集。

1.车辆感知系统车辆感知系统分为视觉感知和雷达感知两种。

其中视觉感知采用摄像头对车辆进行捕捉和识别等操作,而雷达感知通过雷达的发射和接收来获取车辆的运行和位置信息。

2.气象感知系统气象感知系统主要采用气象传感器测量空气温度、湿度、风速、雨量等指标,并将其转换为电子信号,经过数据传输传到监控中心,以便及时采取相应措施。

3.路面感知系统路面感知系统主要包括车辙检测装置、光纤传感器等,可以依据车辆在路面上的行驶情况以及路面结构如波动等因素来掌握公路的实时状态,从而及时进行维护和管理。

二、智能交通系统中的数据处理通过采集车辆的行驶信息和公路的实时状况,智能交通系统可以进行精细化的地图标记和车辆调度,大幅度降低路面拥堵率并提高出行效率。

1.智能化的数据分析智能化的数据分析技术一般采用机器学习、深度学习等人工智能技术,对采集到的数据进行预处理、清洗、分类等操作,并将结果给出反馈,进而进行下一步分析和应用。

2.智能化的路径规划基于采集的数据,智能交通系统应用路径规划算法,选择最优的出行方案,包括时间、距离、车流量等多维因素综合考虑,从而使行车过程更加平稳、高效。

三、智能交通系统中的若干研究方向1.数据的运用和分析方法研究如何更好地使用机器学习、人工智能等技术,以及更准确和可视化的数据分析方法等,都需要各领域专业研究人员深度探讨。

2.多源数据融合规划通过路况感知、路面感知、车辆感知等多来源数据的采集和融合,精确刻画公路的运行状态,为路况分析、车辆调度和路径规划等提供更加准确的基础数据。

高速公路交通信息采集系统设计随着社会经济的快速发展和人们生活水平的不断提高,交通问题逐渐成为制约国家发展的重要因素之一。

在现代城市中,交通拥堵已经成为了人们生活中的一大烦恼,而高速公路交通信息采集系统的设计,就是为了解决这个问题。

本文将从设计的背景、设计的目标和设计的方案等方面,对高速公路交通信息采集系统进行探讨。

一、设计的背景随着城市化进程的加速,人口的大规模流动和车辆的快速增加,交通拥堵的问题越来越严重。

高速公路作为重要的交通设施,承载着大量的车流和人流,但是由于车辆数量的增加,导致高速公路的交通流量越来越大,交通拥堵问题日益严重。

同时,传统的高速公路交通管理方法已经不能很好地处理复杂的交通环境,迫切需要一种新的高效交通信息处理系统来更好地管理高速公路交通。

二、设计的目标高速公路交通信息采集系统的设计的目标,是帮助交通管理部门更好地处理交通信息,实现道路交通的科学管理。

具体地说,它可以实现以下几个方面的目标:1. 实现高速公路实时监控。

利用高精度跟踪技术,通过自动化的摄像头系统,实现对道路上的行车情况进行实时监测,为交通管理者提供实时的路况数据。

2. 提高交通安全水平。

通过对道路上的交通信息进行采集和处理,及时发现各种交通违规行为,并及时进行处理,提高交通规范度和安全水平。

3. 降低耗时和物力成本。

通过智能化的高速公路交通信息采集系统,自动化的完成各种交通信息的收集和处理,降低人力资源和物资投入成本,提高道路交通的效率。

4. 实现路况预测功能。

通过对历史数据和实时采集的数据进行分析,对未来的交通情况进行预测。

为交通部门提供预测数据,帮助其更好地制定管理决策。

三、设计方案高速公路交通信息采集系统的设计中,需要解决以下几个重点问题:1. 数据采集和处理高速公路交通信息的采集和处理,是系统设计的核心和难点。

通过高精度的摄像头和相关传感器,对道路上的车辆行驶情况进行实时监测,并通过智能化算法对各种信息(如车辆数量、速度、车型、车牌等)进行采集和处理,通过智能分析技术和大数据处理技术,对采集的数据进行分析和处理,生成管理人员所需要的各类报表和图表,达到及时监管和迅速反应的目的。

高速数据采集与处理系统设计与验证研究摘要:高速数据采集与处理系统在许多领域中具有重要的应用,如通讯、工业控制、医疗诊断等。

本文旨在通过设计与验证研究,探讨高速数据采集与处理系统的各个组成部分及其相互之间的关系,以及如何优化系统性能。

该研究可为高速数据采集与处理系统的设计与应用提供理论依据和实践指导。

1. 引言高速数据采集与处理系统是指能够以高速率采集大量数据并进行实时处理的系统。

在许多领域中,如科学研究、工业控制、医疗诊断等,高速数据采集与处理系统都起着关键作用。

然而,由于数据量大、采样频率高,对系统的设计与验证提出了很大的挑战。

2. 高速数据采集系统设计高速数据采集系统的设计包括硬件和软件两个方面。

硬件方面主要包括采集设备的选择和配置、模拟电路设计、高速采样模块的设计等。

软件方面主要包括数据采集控制程序的设计和开发、数据传输协议的制定等。

2.1 采集设备的选择和配置在设计高速数据采集系统时,首先需要选择合适的采集设备。

常见的采集设备有采集卡、采集模块和数据采集仪器等。

根据实际需求,选择具有高采样率、高精度和稳定性的采集设备。

2.2 模拟电路设计模拟电路设计是高速数据采集系统设计的重要组成部分。

通过合理设计模拟电路,可以保证从传感器或信号源输入到采集设备的信号质量。

常见的模拟电路设计技术包括放大器设计、滤波器设计和抗干扰设计等。

2.3 高速采样模块的设计高速采样模块是高速数据采集系统中的核心部分,它负责将模拟输入信号转换为数字信号,并通过总线接口传输给处理部分。

高速采样模块的设计需要考虑采样率、分辨率、存储容量等因素,并采用合适的数模转换器和存储器。

3. 高速数据处理系统设计高速数据处理系统设计主要包括数据接收、数据处理和数据存储三个环节。

3.1 数据接收数据接收是指将高速采样模块采集到的数据传输到数据处理部分。

在数据接收过程中,需要考虑数据传输速率、数据稳定性和数据完整性等问题。

常见的数据传输技术有PCIe、USB和以太网等。

高速公路信息采集与处理技术研究随着社会和经济的发展,交通路网的建设不断扩大和提升。

其中高速公路的建设已经成为现代化交通网络建设的重要组成部分。

高速公路具有安全、快速、舒适等优点,是人们出行的首选交通方式。

为了满足人们对于高速公路行车安全与畅通的需求,信息技术在高速公路信息采集与处理方面的应用也不断推进,其意义重大。

一、高速公路信息采集技术信息采集是高速公路收集车辆运行状态和交通情况的基础,是智能交通系统运作的核心。

在高速公路上,信息采集技术应包括实时车流数采集、车速和密度采集、重载运输车辆数量采集、爆胎和撞击事故采集、违法行为采集等。

1.实时车流数采集技术实时车流数采集技术是通过调配采集设备,对车道内车辆进行实时车流数采集,以实现车流数实时监测和车辆通行速度、拥堵情况信息的采集。

车流量监测系统主要利用车流量检测器、地磁线圈、光电传感器和微波探测等技术手段,通过非接触、无感、无损和高精度等采集车辆数目和位置信息,可实现对车道内车辆进行实时的监测和计算。

2.车速和密度采集技术车速和密度采集技术是在实时车流数采集技术的基础上,衍生出的一种车辆信息采集技术,用于采集车辆通行速度和密度信息,并对车载GPS导航进行升级,利用手机APP等方式,提供车辆通行状态、路段拥堵情况和预测等信息。

3.重载运输车辆数量采集技术重载运输车辆数量采集技术是一种针对国道公路、高速公路等重载运输车辆密集路段的信息采集技术,可直观地为过路车辆提供当前高速公路通行情况。

采集技术一般采用图像识别、车牌识别技术、视频监控技术等,其数据可具有自动上传、存储、显示等功能。

4.爆胎、撞击事故信息采集技术爆胎和撞击事故信息采集技术主要是针对高速公路上由于轮胎爆炸、疲劳驾驶、刹车故障、侧翻等原因导致的路面事故进行信息采集和传递,信息采集技术一般为图像识别技术和视频监控技术。

5.违法行为信息采集技术违法行为信息采集技术是指利用卡口、视频监控、电子警察等黑科技手段,对高速公路上不遵守交通规则行为的车辆、驾驶人员等信息进行采集,以保证道路交通安全。

基于FPGA的高速数据采集与处理系统研究近年来,随着科技的不断发展和进步,以及信息化时代的到来,传统的数据采集与处理方式已经无法满足日益增长的数据处理需求,而基于FPGA的高速数据采集与处理系统成为了一种重要的选择。

本文将从以下几个方面探讨基于FPGA的高速数据采集与处理系统的研究。

一、FPGA的基本概念与特点FPGA全称为Field Programmable Gate Array,即现场可编程门阵列。

它是一种可编程逻辑器件,具有灵活性高、可重复编程、性能优异等特点。

FPGA的基本结构由可编程逻辑单元、可编程连线资源和I/O单元组成。

其中,可编程逻辑单元用于实现逻辑运算,可编程连线资源用于连接不同逻辑单元,I/O单元则用于与外部设备进行数据交互。

FPGA的工作原理是通过将Verilog或VHDL等高级语言代码编译成二进制文件,然后通过下载到FPGA芯片中实现功能。

FPGA具有灵活性高、可重复编程、性能优异等特点,如在数据采集和处理中,由于采集数据来源的差异性和复杂性,需要对采集和处理过程进行实时控制,使用FPGA可实现强大的实时控制能力,能够将数据采集与处理相结合,达到高效、稳定和可靠的数据处理效果。

二、基于FPGA的高速数据采集采集数据是数据处理的第一步,准确且高效的数据采集对于后续的数据处理具有至关重要的意义。

在基于FPGA的高速数据采集系统中,通常采用DMA(Direct Memory Access)方式实现高速数据传输,以便实现高效的数据采集。

DMA是一种数据传输方式,其不需要CPU的介入,直接将数据从外部设备读写到内存中,从而有效提高数据采集速度和效率。

在基于FPGA的数据采集系统中,通常在FPGA外加一块高速缓存,通过DMA方式,在缓存区内进行前端数据的处理和分包,然后再通过FPGA与下一段处理单元进行数据交互。

三、基于FPGA的高速数据处理基于FPGA的高速数据处理是本文的重点。

数据处理是对采集到的数据进行计算、分类、过滤、压缩等处理操作,直接决定了数据处理的质量和效率。

基于DSP的高速多通道同步数据采集系统摘要:本文介绍了一种基于DSP的高速多通道同步数据采集系统。

该系统采用高精度的ADC和FPGA作为数据采集和处理的核心部件,通过DMA传输实现了多通道同步数据采集,并可以通过网络接口将采集的数据实时传输到上位机。

实验结果表明,该系统具有高精度、高速率和高可靠性等优点,可以满足对多通道同步数据采集的高要求。

关键词:DSP;高速多通道;同步数据采集;DMA传输;网络接口1. 引言在科学研究、医学诊断、工业控制等领域中,对数据采集系统的要求越来越高。

随着科学技术的不断发展,现代数据采集系统的要求也变得越来越高。

要求数据采集速度快、采集精度高、可靠性强、系统稳定性好。

因此,如何设计一种高速、高精度、高可靠性的多通道同步数据采集系统成为研究的热点之一。

2. 系统框架基于上述需求,本文设计了一种基于DSP的高速多通道同步数据采集系统。

该系统的部件结构如下图所示:其中,ADC为数据采集部分,FPGA为数据处理部分,DSP为数据管理和传输部分。

3. 数据采集部分数据采集部分采用高精度的ADC为核心部件。

该ADC采用的是16位的Sigma-Delta型ADC,采样率可达到100kSPS,可以满足多通道高速同步采集的要求。

为了实现多通道同步采集,采集部分还需要将多个通道的信号进行采集,并进行同步处理。

实现该功能需要向FPGA发送同步信号。

为了避免信号在传输过程中的延迟造成的误差,我们使用了双向同步FIFO,并设置了一些额外的同步逻辑来确保采集的信号可以达到很高的同步精度。

4. 数据处理部分数据处理部分采用FPGA作为核心部件。

该FPGA可以对采集到的数据进行在线实时处理。

在此过程中,FPGA实现了信号滤波、频率分析、功率谱分析、时域分析等多种功能。

这些功能可以满足不同领域的数据处理要求。

5. 数据管理和传输部分数据管理和传输部分采用DSP作为核心部件。

DSP主要负责管理数据的存储和传输。

技术创新《微计算机信息》2012年第28卷第10期120元/年邮局订阅号:82-946《现场总线技术应用200例》嵌入式与SOC一种便携式高速数据采集器的研究实现Realization of a portable High-speed Test Device(中储发展股份有限公司)张珂ZHANG Ke摘要:文中阐述了一种新的数据采集设备的设计实现方案,该方案基于热插拔技术和可编程设计理念,可通过参数的在线配置满足不同应用场合的测试需求,满足在系统可靠性,易用性,通用性和可移植性方面的要求。

关健字:FPGA;USB;FIFO;控制器中图分类号:TP 275文献标识码:AAbstract:The paper raised a novelty scheme to realize a new data test device.Based on USB and FPGA technique,The system could adjust to various testing needs via parameter configured on software.The scheme utilized module method and did a lot of study to make the system reliable,friendly,adjustable and transplantable.Key Words:FPGA;USB;FIFO;controller文章编号:1008-0570(2012)10-0212-021引言生产实践中往往需要掌握生产环节的参数,如储运企业需要对储运现场中的物资品种、类型、型号、等级、数量等数据进行动态地跟踪采集。

运用测量技术对有关参数进行实时采集、自动存储、即时显示、即时反馈、自动处理、自动传输等可以保证现场采集数据的真实、有效、实时、可用,缩短盘点周期和盘点时间,实现不停业盘点,减少现场操作失误。

PCIE高速数据采集系统的驱动及上位机软件开发的开题报告1. 研究背景随着科学技术的不断进步,数据采集系统在实际应用中发挥着越来越重要的作用,其中PCIE高速数据采集系统是目前应用广泛的一种数据采集系统。

它能够实现数据的快速、高效采集,并可以通过PC机进行数据处理和分析,被广泛应用于医学、工业生产、科学研究等领域。

本课题的研究目的就是开发一套高效稳定的PCIE高速数据采集系统的驱动及上位机软件,以满足实际应用的需求。

2. 研究内容本课题将主要涉及PCIE高速数据采集系统的驱动及上位机软件开发。

具体研究内容包括以下几个方面:(1)PCIE高速数据采集卡的驱动程序开发。

该部分将包括PCIE高速数据采集卡的硬件环境和软件环境的搭建,驱动程序的调试和优化等工作,以保证数据采集的高效稳定。

(2)上位机软件的设计与开发。

该部分将包括上位机软件的界面设计、数据处理算法的设计与实现、数据导出文件格式的定义等工作,以满足实际应用的需求。

(3)系统测试与优化。

该部分将对整个系统进行测试和性能优化,以进一步提高系统的稳定性和性能。

3. 研究方法本课题将采用软硬件相结合的开发模式,具体方法如下:(1)硬件方面,本课题将使用常见的PCIE高速数据采集卡作为数据采集的硬件平台,利用VHDL语言对硬件进行设计和开发。

(2)软件方面,本课题将采用C++语言编写PCIE高速数据采集卡的驱动程序,并在此基础上开发上位机软件。

(3)测试与优化方面,本课题将采用逐步测试和优化的方法,确定优化的方向和重点,并不断进行测试和调整,以达到系统的最优性能。

4. 预期成果完成本课题后,将实现以下预期成果:(1)PCIE高速数据采集卡的驱动程序的开发与调试,实现高效稳定的数据采集功能。

(2)上位机软件的设计与开发,实现友好的界面、高效的数据处理算法和数据导出功能。

(3)系统的测试与性能优化,实现系统的高效稳定运行。

5. 研究意义本课题的研究意义主要体现在以下几个方面:(1)本课题将提高PCIE高速数据采集系统的稳定性和性能,满足实际应用中的数据采集需求。

第31卷第5期 唐山师范学院学报 2009年9月 Vol. 31 No. 5 Journal of Tangshan Teachers College Sep. 2009────────── 收稿日期:2008-12-12 作者简介:李洋(1982-),男,河北衡水人,唐山师范学院基础教育部教师。

-66-一种高速数据采集系统的研究李 洋,郭小松(唐山师范学院 基础教育部,河北 唐山 063000)摘 要:由于高速数据采集对信号完整性、信号干扰、高速布线及数据处理和高速实时存储要求极高,而其应用环境又往往非常复杂,所以在目前的实际应用中,很难实现一种既能进行长时间高速数据采集、又能进行大容量存储的数据采集系统。

在此背景下,提出了一种高速数据采集及存储的解决方案,采用高速FPGA 加嵌入式微处理器作为中央处理器来进行高速数据传输和磁盘阵列数据存储,实现高速数据采集及大容量实时存储。

关键词:数据采集;模数转换;海量存储;RAID0 中图分类号: T N919.5文献标识码:A文章编号:1009-9115(2009)05-0066-03Study of High-Speed Data Acquisition and Storage SystemLI Yang, GUO Xiao-song(Department of Foundation Education, Tangshan Teachers College, Tangshan Hebei 063000, China)Abstract: Because of the extreme requirements of signal integrity, noise jamming, high-speed layout, high-speed real-time storage and the complex application environments, it is very difficult to realize a high-speed data acquisition system which is suitable for long-time data acquisition and mass storage. Against this background, a solution of high-speed data acquisition and storage system is introduced in this thesis, which is using of high-speed FPGA and embedded microprocessors as the central processing device for high-speed data transfer and data storage of redundant array of inexpensive disks , realized on-time data acquisition and mass storage.Key words: data acquisition; A/D convert; mass storage; RAID现代工业生产和科学研究对数据采集的要求日益提高,在雷达、声纳、软件无线电、瞬态信号测量等一些高速、高精度的测量中,需要进行高速数据采集。

目前,数据采集系统在高速A/D 、D/A 器件发展的带动下,采集带宽在稳步提高,具有100MSPS 采集能力以上的高速数据采集系统产品己较成熟。

然而国外厂商的高速采集系统往往都价格不菲,而且由于高速数据采集对信号完整性、信号干扰、高速布线及数据处理和高速实时存储要求极高,国内完全掌握这个技术的厂商并不多,所以在实际应用中,很难找到一种满足需要的高速采集系统。

这种情况长期限制了高速数据采集技术在我国工业生产和科学研究中的应用。

在这样的背景下,本文提出一种高速数据采集与实时存储系统的解决方案,解决以往在高速技术、数据存储与传输技术等方面的几个技术难点,采用FPGA 作为核心器件,集成中央逻辑控制及硬盘接口,直接将高速数据存入有多块硬盘组成的实时RAID 存储系统中,实现了高速采集和实时存储,并可脱机运行。

这种方案成本低廉,能提高采集速度,增加系统可靠性,并大大提高可持续采集时间,具有较大的灵活性。

1 总体系统方案硬件设计高速数据采集系统的主要目的是把采集到的模拟信号转化为数字信号,所以模拟信号进入数据采集系统的第一步就是通过AD 采集电路进行模数转换;采集到的数据为了以后研究调用,就需要存储到存储器中,所以系统的最后一步是使用高速海量存储器对数据进行存储;系统的启动、停止和数据传输的方式还需要使用中央逻辑控制电路,所以在AD 采集电路与高速海量存储器之间增加中央逻辑控制电路来作为AD 采集电路与高速海量存储器之间的桥梁;系统通过人机接口与PC 机连接,可以对数据采集系统进行调试,还方便调用存储数据进行研究测试,并实现李 洋,等:一种高速数据采集系统的研究-67-系统的脱机运行。

通过上面介绍表明,制约高速数据采集系统性能的关键为高速ADC 技术和数据实时存储技术,其中AD 采集电路为高速ADC 技术部分,中央逻辑控制和高速海量存储器是数据存储技术部分。

下面,我们分别讲述这两大技术部分在本系统中的总体设计实现。

2 高速AD 采集电路设计高速AD 采集电路设计主要包括三个部分:模拟信号输入部分、模数转换电路部分和数字信号输出部分。

AD 转换器对输入的模拟信号有两点要求:一是输入信号的带宽要在AD 转换器允许输入的范围内。

由于从外界采集来的模拟信号多种多样,其信号带宽范围很大,有些信号达不到AD 转换器输入带宽的要求,所以要在模拟信号进入AD 转换器之前对信号的带宽进行放大或衰减。

二是输入信号必须为差分信号。

但是外界输入的模拟信号为单端信号,所以要在信号进入AD 转换器之前对单端信号进行差分变换。

根据以上两点要求,要在AD 转换电路之前增加一个差分放大电路。

为了实现差分放大功能,并且引入尽量少的噪声信号,采用集成信号调理芯片是一个不错的选择。

AD8131是AD 公司生产的低损耗高速差分放大器,该放大器具有较宽的模拟带宽(400MHz 、-3DB ),其固定增益为2。

AD8131有其独特的内部反馈功能,可减少辐射电磁干扰和抑制谐波。

信号采集的核心是模数转换技术。

模数转换(AD )是将模拟输入信号转换为N 位二进制数字输出信号的技术。

模数转换包括采样、保持、量化和编码四个过程。

常用的AD 转换器有积分型模数转换器、逐次逼近型模数转换器、闪烁型模数转换器、Σ-Δ型模数转换器和流水线模数转换器[1]。

由于系统要求转换速率在200MSPS-300MSPS 之间且转换精度在8位-10位之间,积分型、逐次逼近型和Σ-Δ型在速度上达不到要求,流水线型由于其价格过高,所以在本次设计中选用闪烁型模数转换器。

本次设计采用了ADI 公司生产的闪烁型AD9410转换器。

它是单片、10位精度并且具有最大210MSPS 转换速率的高速模数转换器,其片内还集成了高性能的采样保持放大器和参考电压源,具有较低的功耗和较高的信噪比。

在高速数据采集系统中,若AD 转换器直接与中央处理器相接,则因高速AD 的转换速率较高,迫使中央处理器不断地读取转换结果,因而就占用了中央处理器大部分的IO 带宽,降低了中央处理器的工作效率。

因此在AD 转换器与中央处理器之间连接大容量高速缓存来提高中央处理器工作效率。

选用的ADC 芯片AD9410是同步并行数据接口,具有一个时钟信号和10位数据总线,数据在时钟上升沿送出,和FIFO 的时序匹配,所以非常适合和FIFO 连接。

考虑到FIFO 实现上的方便性和高效性,我们决定采用大容量FIFO 芯片IDT72V36110作为系统高速数据缓存。

不过AD9410是10位输出,IDT72V36110是36位总线,为了既保证总线吞吐率又不损失FIFO 容量,可以设置IDT72V36110总线自动匹配模式来解决这个问题。

通过拉高或拉低IW 、OW 和BW 这三个输入引脚,来设置输入和输出总线的宽度。

通过分别把这三位设置成“高 低 高”,将IDT72V36110配置成16位输入,32位输出。

IDT72V36110会自动把两个16位数据合并成一个32位数据放在FIFO 中,而不损失另外16位容量。

这种接法仅浪费少量FIFO 容量(4bit ),却保证了数据的最大吞吐率[2]。

另外,IDT72V36110的半满(HF#)、满(FF#)、空(EF#)、半空(HE#)等信号都连接到FPGA 上,FPGA 根据这些状态信号来判定IDT72V36110的状态,控制FPGA 内部控制时序。

IDT72V36110的数据输出端也直接连到FPGA 上,由FPGA 直接读取FIFO 中的数据,读时钟RCLC 为80MHz 。

在80MHz 的读时钟下,FIFO 的数据吞吐量为32×80MHz=2.56Gb/s ,即320Mb/s ,不但满足系统最大带宽要求,还减小了数据的传输时间。

3 高速实时存储技术设计实时存储技术包括数据流的逻辑控制部分和数据存储部分。

为了控制高速数据流,需要一个微处理器和一块FPGA 作为核心控制模块。

微处理器工作比较简单,数据流并不通过它传输,它仅仅是控制数据传输的开始和结束及数据的流向等,因此并不要求很强的处理能力。

它与FPGA 可以采用主从方式,FPGA 作为一个外设挂在微处理器总线上。

微处理器可以通过设置内部控制器的工作方式来控制数据传输与存储。

ARM 微处理器作为流行的嵌入式处理器,非常适合作为本系统的微处理器。

ARM 微处理器芯片选用Phlilp 的ARM7芯片LPC2214,具有128kb 片上和Flash 片内RAM ,只需单芯片就可以工作,因此电路设计非常简单,还增强了系统可靠性。

FPGA 直接与FIFO 和硬盘阵列相连,它起到数据到存储器的桥梁作用,因此数据吞吐能力必须非常强。

此外,它还要负责IDE 硬盘的接口逻辑。

因此FPGA 在系统中的重要性非常大。

我们最后选用ALTERA 的Cyclone 系列EP1C6-Q240C6芯片,它具有低功耗,容量大,价格便宜的特点。

12万门的容量足够构建复杂的控制逻辑,其内部还带有100kb 的内存块资源,可以用来设计内部高速FIFO 、双口RAM 等器件,可以简化设计及提高性能。

存储部分是依靠存储器介质来实现的,从存储容量、读写速度和单位成本等方面综合考虑,采用高速硬盘直接存储数据是很有优势的。

为此,可以考虑利用多个IDE 硬盘组成磁盘阵列,采用类似RAID0模式的磁盘阵列组织方第31卷第5期 唐山师范学院学报 2009年9月-68-式。