Power minimization algorithms for LUT-based FPGA technology mapping

- 格式:pdf

- 大小:137.72 KB

- 文档页数:19

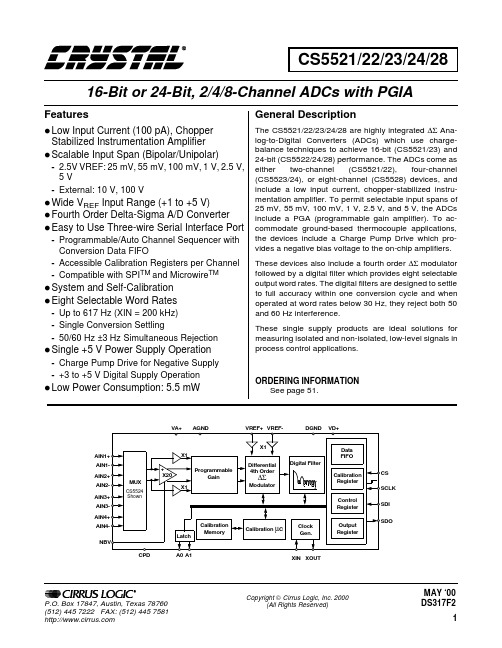

Copyright © Cirrus Logic, Inc. 2000CS5521/22/23/24/2816-Bit or 24-Bit, 2/4/8-Channel ADCs with PGIAFeaturesl Low Input Current (100pA), ChopperStabilized Instrumentation Amplifier l Scalable Input Span (Bipolar/Unipolar)-2.5V VREF: 25mV, 55mV, 100mV, 1V, 2.5V, 5V-External: 10V, 100 Vl Wide V REF Input Range (+1 to +5V)l Fourth Order Delta-Sigma A/D Converter l Easy to Use Three-wire Serial Interface Port-Programmable/Auto Channel Sequencer with Conversion Data FIFO-Accessible Calibration Registers per Channel -Compatible with SPI TM and Microwire TMl System and Self-Calibration l Eight Selectable Word Rates-Up to 617Hz (XIN =200kHz)-Single Conversion Settling-50/60Hz ±3Hz Simultaneous Rejectionl Single +5V Power Supply Operation-Charge Pump Drive for Negative Supply -+3 to +5V Digital Supply Operationl Low Power Consumption: 5.5mWGeneral DescriptionThe CS5521/22/23/24/28 are highly integrated ∆Σ Ana-log-to-Digital Converters (ADCs) which use charge-balance techniques to achieve 16-bit (CS5521/23) and 24-bit (CS5522/24/28) performance. The ADCs come as either two-channel (CS5521/22), four-channel (CS5523/24), or eight-channel (CS5528) devices, and include a low input current, chopper-stabilized instru-mentation amplifier. To permit selectable input spans of 25mV, 55mV, 100mV, 1V, 2.5V, and 5V, the ADCs include a PGA (programmable gain amplifier). To ac-commodate ground-based thermocouple applications,the devices include a Charge Pump Drive which pro-vides a negative bias voltage to the on-chip amplifiers.These devices also include a fourth order ∆Σ modulator followed by a digital filter which provides eight selectable output word rates . The digital filters are designed to settle to full accuracy within one conversion cycle and when operated at word rates below 30Hz, they reject both 50and 60Hz interference.These single supply products are ideal solutions for measuring isolated and non-isolated, low-level signals in process control applications.ORDERING INFORMATIONSee page 51.ProgrammableGainVA+AGND VREF+VREF-VD+DGND XIN XOUTSDOSDI NBVLatchDifferential Digital FilterCalibration Register Control RegisterOutput Register4th Order ∆ΣModulatorCalibration MemoryCalibration µCClock Gen.SCLK CS MUXAIN2++X20X1X1X1CS5524 ShownAIN2-AIN1+AIN1-AIN4+AIN4-AIN3+AIN3-A0A1CPDData FIFO MAY ‘00DS317F2TABLE OF CONTENTS1. CHARACTERISTICS AND SPECIFICATIONS (5)ANALOG CHARACTERISTICS (5)TYPICAL RMS NOISE, CS5521/23 (7)TYPICAL NOISE FREE RESOLUTION (BITS), CS5521/23 (7)TYPICAL RMS NOISE, CS5522/24/28 (8)TYPICAL NOISE FREE RESOLUTION (BITS), CS5522/24/28 (8)5 V DIGITAL CHARACTERISTICS (9)3 V DIGITAL CHARACTERISTICS (9)DYNAMIC CHARACTERISTICS (10)RECOMMENDED OPERATING CONDITIONS (10)ABSOLUTE MAXIMUM RATINGS (10)SWITCHING CHARACTERISTICS (11)2. GENERAL DESCRIPTION (13)2.1 Analog Input (13)2.1.1 Instrumentation Amplifier (14)2.1.2 Coarse/Fine Charge Buffers (14)2.1.3 Analog Input Span Considerations (15)2.1.4 Measuring Voltages Higher than 5 V (15)2.1.5 Voltage Reference (16)2.2 Overview of ADC Register Structure and Operating Modes (16)2.2.1 System Initialization (18)2.2.2 Serial Port Initialization Sequence (18)2.2.3 Command Register Quick Reference (19)2.2.4 Command Register Descriptions (20)2.2.5 Serial Port Interface (25)2.2.6 Reading/Writing the Offset, Gain, and Configuration Registers (26)2.2.7 Reading/Writing the Channel-Setup Registers (26)2.2.7.1 Latch Outputs (28)2.2.7.2 Channel Select Bits (28)2.2.7.3 Output Word Rate Selection (28)2.2.7.4 Gain Bits (28)2.2.7.5 Unipolar/Bipolar Bit (28)2.2.8 Configuration Register (28)2.2.8.1 Chop Frequency Select (28)2.2.8.2 Conversion/Calibration Control Bits (28)2.2.8.3 Power Consumption Control Bits (28)Contacting Cirrus Logic SupportFor a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: /corporate/contacts/SPI™ is a trademark of Motorola Inc., Microwire™ is a trademark of National Semiconductor Corp.Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided “AS IS” without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval sys-tem, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise). Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at .2.2.8.4 Charge Pump Disable (29)2.2.8.5 Reset System Control Bits (29)2.2.8.6 Data Conversion Error Flags (29)2.3 Calibration (31)2.3.1 Self Calibration (31)2.3.2 System Calibration (32)2.3.3 Calibration Tips (34)2.3.4 Limitations in Calibration Range (34)2.4 Performing Conversions and Reading the Data Conversion FIFO (34)2.4.1 Conversion Protocol (35)2.4.1.1 Single, One-Setup Conversion (35)2.4.1.2 Repeated One-Setup Conversions without Wait (35)2.4.1.3 Repeated One-Setup Conversions with Wait (36)2.4.1.4 Single, Multiple-Setup Conversions (36)2.4.1.5 Repeated Multiple-Setup Conversions without Wait (37)2.4.1.6 Repeated Multiple-Setup Conversions with Wait (37)2.4.2 Calibration Protocol (38)2.4.3 Example of Using the CSRs to Perform Conversions and Calibrations (38)2.5 Conversion Output Coding (40)2.5.1 Conversion Data FIFO Descriptions (41)2.6 Digital Filter (42)2.7 Clock Generator (42)2.8 Power Supply Arrangements (43)2.8.1 Charge Pump Drive Circuits (45)2.9 Digital Gain Scaling (45)2.10 Getting Started (46)2.11 PCB Layout (47)3. PIN DESCRIPTIONS (48)3.1 Clock Generator (49)3.2 Control Pins and Serial Data I/O (49)3.3 Measurement and Reference Inputs (49)3.4 Power Supply Connections (50)4. SPECIFICATION DEFINITIONS (51)5. ORDERING GUIDE (51)6. PACKAGE DIMENSION DRAWINGS (52)LIST OF FIGURESFigure 1. Continuous Running SCLK Timing (Not to Scale) (12)Figure 2. SDI Write Timing (Not to Scale) (12)Figure 3. SDO Read Timing (Not to Scale) (12)Figure 4. Multiplexer Configurations (13)Figure 5. Input Models for AIN+ and AIN- pins, £(100 mV Input Ranges (14)Figure 6. Input Models for AIN+ and AIN- pins, >100 mV input ranges (14)Figure 7. Input Ranges Greater than 5 V (16)Figure 8. Input Model for VREF+ and VREF- Pins (16)Figure 9. CS5523/24 Register Diagram (17)Figure 10. Command and Data Word Timing (25)Figure 11. Self Calibration of Offset (Low Ranges) (32)Figure 12. Self Calibration of Offset (High Ranges) (32)Figure 13. Self Calibration of Gain (All Ranges) (32)Figure 14. System Calibration of Offset (Low Ranges) (32)Figure 15. System Calibration of Offset (High Ranges) (33)Figure 16. System Calibration of Gain (Low Ranges) (33)Figure 17. System Calibration of Gain (High Ranges) (33)Figure 18. Filter Response (Normalized to Output Word Rate = 1) (42)Figure 19. Typical Linearity Error for CS5521/23 (42)Figure 20. Typical Linearity Error for CS5522/24/28 (42)Figure 21. CS5522 Configured to use on-chip charge pump to supply NBV (43)Figure 22. CS5522 Configured for ground-referenced Unipolar Signals (44)Figure 23. CS5522 Configured for Single Supply Bridge Measurement (44)Figure 24. Charge Pump Drive Circuit for VD+ = 3 V (45)Figure 25. Alternate NBV Circuits (45)LIST OF TABLESTable 1. Relationship between Full Scale Input, Gain Factors, and Internal AnalogSignal Limitations (15)Table 2. Command Register Quick Reference (19)Table 3. Channel-Setup Registers (27)Table 4. Configuration Register (30)Table 5. Offset and Gain Registers (31)Table 6. Output Coding for 16-bit CS5521/23 and 24-bit CS5522/24/28 (40)1. CHARACTERISTICS AND SPECIFICATIONSANALOG CHARACTERISTICS (T A = 25° C; VA+, VD+ = 5 V ±5%; VREF+ = 2.5 V, VREF- = AGND,NBV = -2.1 V, XIN = 32.768 kHz, CFS1-CFS0 = ‘00’, OWR (Output Word Rate) = 15 Hz, Bipolar Mode, Input Range = ±100 mV; See Notes 1 and 2.)Notes: 1.Applies after system calibration at any temperature within -40° C ~ +85° C.2.Specifications guaranteed by design, characterization, and/or test.3.Specification applies to the device only and does not include any effects by external parasiticthermocouples. LSB N : N is 16 for the CS5521/23 and N is 24 for the CS5522/24/284.Drift over specified temperature range after calibration at power-up at 25° C.5.Measured with Charge Pump Drive off.6.All outputs unloaded. All input CMOS levels and the CS5521/23 do not have a low power mode.ParameterCS5521/23CS5522/24/28Unit Min Typ Max Min Typ Max Accuracy Resolution --16--24Bits Linearity Error -±0.0015±0.003-±0.0007±0.0015%FS Bipolar Offset (Note 3)-±1±2-±16±32LSB N Unipolar Offset (Note 3)-±2±4-±32±64LSB N Offset Drift (Notes 3 and 4)-20--20-nV/°C Bipolar Gain Error -±8±31-±8±31ppm Unipolar Gain Error -±16±62-±16±62ppm Gain Drift (Note 4)-13-13ppm/°CPower SuppliesPower Supply Currents (Normal Mode)I A+(Note 5)I D+I NBV- - - 0.990260 1.2135375 - - - 1.590525 1.9135700mA µA µA Power Consumption (Note 6)Normal Mode Low Power Mode Standby Sleep-N/A -- 5.5N/A 1.25007.5N/A ------95.51.2500127.5--mW mW mW µW Power Supply RejectionPositive Supplies dc NBV--120110----120110--dB dBANALOG CHARACTERISTICS (Continued)Notes:7.For the CS5528, the 25mV, 55mV and 100mV ranges cannot be used unless NBV is powered at -1.8to -2.5V8.See the section of the data sheet which discusses input models. Chop clock is 256Hz (XIN/128) forPGIA (programmable gain instrumentation amplifier). XIN = 32.768kHz.9.The maximum full scale signal can be limited by saturation of circuitry within the internal signal path.ParameterMin TypMaxUnitAnalog InputCommon Mode + Signal on AIN+ or AIN-Bipolar/Unipolar ModeNBV = -1.8 to -2.5 V Range = 25 mV, 55 mV, or 100 mVRange = 1 V, 2.5 V, or 5 VNBV = AGND Range = 25 mV, 55 mV, or 100 mV (Note 7)Range = 1 V, 2.5 V, or 5 V-0.150NBV 1.850.0----0.950VA+2.65VA+V V V V CVF Current on AIN+ or AIN-(Note 8)Range = 25 mV, 55 mV, or 100 mV Range = 1 V, 2.5 V, or 5 V--10010300-pA nA Input Current Drift (Note 8)Range = 25 mV, 55 mV, or 100 mV-1-pA/°C Input Leakage for Multiplexer when Off -10-pA Common Mode Rejection dc50, 60 Hz--120120--dB dB Input Capacitance-10-pF Voltage Reference Input Range (VREF+) - (VREF-)12.5VA+V VREF+(VREF-)+1-VA+V VREF-NBV -(VREF+)-1V CVF Current (Note 8)- 5.0-nA Common Mode Rejection dc50, 60 Hz--110130--dB dB Input Capacitance-16-pFSystem Calibration SpecificationsFull Scale Calibration Range (VREF = 2.5V)Bipolar/Unipolar Mode25 mV 55 mV 100 mV 1 V 2.5 V 5 V1025400.401.02.0------32.571.51051.303.25VA+mV mV mV V V V Offset Calibration Range Bipolar/Unipolar Mode25 mV 55 mV 100 mV (Note 9)1 V 2.5 V 5 V------------±12.5±27.5±50±0.5±1.25±2.50mV mV mV V V VTYPICAL RMS NOISE, CS5521/23 (Notes 10 and 11)Notes:10.Wideband noise aliased into the baseband. Referred to the input. Typical values shown for 25° C.11.To estimate Peak-to-Peak Noise, multiply RMS noise by 6.6 for all ranges and output rates.12.For input ranges <100mV and output rates ≥60Hz, 16.384kHz chopping frequency is used.TYPICAL NOISE FREE RESOLUTION (BITS), CS5521/23 (Note 13)Notes:13.For bipolar mode, the number of bits of Noise Free Resolution is LOG((2XInput Range)/(6.6xRMSNoise))/LOG(2) rounded to the nearest bit. For unipolar mode, the number of bits of Noise Free Resolution is LOG((Input Range)/(6.6xRMS Noise))/LOG(2) rounded to the nearest bit. Also, the CS5521/23’s output conversions are 16 bits. Noise free Resolution numbers are based uponVREF =2.5V and XIN =32.768kHz. The values will be affected directly by changes in VREF, but the effects due to changes in the XIN frequency will be minor.Output Rate (Hz)-3 dB FilterFrequency Input Range, (Bipolar/Unipolar Mode)25 mV55 mV 100 mV 1 V 2.5 V 5 V1.88 1.6490 nV 148 nV 220 nV 1.8 µV 3.9 µV 7.8 µV 3.76 3.27122 nV 182 nV 310 nV2.6 µV 5.7 µV 11.3 µV 7.51 6.55180 nV 267 nV 435 nV3.7 µV 8.5 µV 18.1 µV 15.012.7280 nV 440 nV 810 nV 5.7 µV 14 µV 28 µV 30.025.4580 nV 1.1 µV 2.1 µV 18.2 µV 48 µV 96 µV 61.6 (Note 12)50.4 2.6 µV4.9 µV 8.5 µV 92 µV 238 µV 390 µV 84.5 (Note 12)70.711 µV 27 µV 43 µV 458 µV 1.1 mV 2.4 mV 101.1 (Note 12)84.641 µV72 µV 130 µV 1.2 mV 3.4 mV6.7 mVOutput Rate (Hz)-3 dB FilterFrequency Input Range, (Bipolar Mode)25 mV55 mV 100 mV 1 V 2.5 V5 V 1.88 1.641616161616163.76 3.271616161616167.51 6.5515161616161615.012.715151516161630.025.414141414141461.6 (Note 12)50.412121212121284.5 (Note 12)70.7999999101.1 (Note 12)84.6888888TYPICAL RMS NOISE, CS5522/24/28 (Notes 14 and 15)Notes:14.Wideband noise aliased into the baseband. Referred to the input. Typical values shown for 25° C.15.To estimate Peak-to-Peak Noise, multiply RMS noise by 6.6 for all ranges and output rates.16.For input ranges <100mV and output rates ≥60Hz, 16.384kHz chopping frequency is used.TYPICAL NOISE FREE RESOLUTION (BITS), CS5522/24/28 (Note 17)Notes:17.For bipolar mode, the number of bits of Noise Free Resolution is LOG((2XInput Range)/(6.6xRMSNoise))/LOG(2) rounded to the nearest bit. For unipolar mode, the number of bits of Noise Free Resolution is LOG((Input Range)/(6.6xRMS Noise))/LOG(2) rounded to the nearest bit. Also, the CS5522/24/28’s output conversions are 24 bits. Noise free Resolution numbers are based uponVREF =2.5V and XIN =32.768kHz. The values will be affected directly by changes in VREF, but the effects due to changes in the XIN frequency will be minor.Output Rate (Hz)-3 dB FilterFrequency Input Range, (Bipolar/Unipolar Mode)25 mV55 mV 100 mV 1 V 2.5 V 5 V1.88 1.6490 nV 95 nV 140 nV 1.5 µV 3 µV 6 µV 3.76 3.27110 nV 130 nV 190 nV 2 µV 4 µV 8 µV 7.51 6.55170 nV 200 nV 275 nV2.5 µV 6 µV 11.5 µV 15.012.7250 nV 330 nV 580 nV 4.5 µV 10 µV 20 µV 30.025.4500 nV 1 µV 1.5 µV 16 µV 45 µV 85 µV 61.6 (Note 16)50.4 2 µV 4 µV 8 µV 72 µV 195 µV 350 µV 84.5 (Note 16)70.710 µV 20 µV 35 µV 340 µV 900 µV 2 mV 101.1 (Note 16)84.630 µV60 µV 105 µV 1.1 mV 3 mV5.3 mVOutput Rate (Hz)-3 dB FilterFrequency Input Range, (Bipolar Mode)25 mV55 mV 100 mV 1 V 2.5 V5 V 1.88 1.641617181818183.76 3.271617171718187.51 6.5515161717171715.012.715161616161630.025.414141414141461.6 (Note 16)50.412121212121284.5 (Note 16)70.7101010101010101.1 (Note 16)84.68888885 V DIGITAL CHARACTERISTICS (T A = 25° C; VA+, VD+ = 5 V ±5%; GND = 0;See Notes 2 and 18.))Notes:18.All measurements performed under static conditions.19.I out = -100µA unless stated otherwise. (V OH = 2.4 V @ I out = -40µA.)3 V DIGITAL CHARACTERISTICS (T A = 25° C; VA+ = 5 V ±5%; VD+ = 3.0 V ±10%; GND = 0;See Notes 2 and 18.)ParameterSymbol Min Typ Max Unit High-Level Input VoltageAll Pins Except XIN and SCLKXIN SCLK V IH0.6 VD+(VD+)-0.5(VD+) - 0.45------V V V Low-Level Input VoltageAll Pins Except XIN and SCLKXIN SCLKV IL------0.81.50.6V V V High-Level Output VoltageAll Pins Except CPD and SDO (Note 19)CPD, I out = -4.0 mA SDO, I out = -5.0 mA V OH(VA+) - 1.0(VD+) - 1.0(VD+) - 1.0------V V V Low-Level Output VoltageAll Pins Except CPD and SDO, I out = 1.6 mACPD, I out = 2 mA SDO, I out = 5.0 mA V OL------0.40.40.4V V V Input Leakage Current I in -±1±10µA 3-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFParameterSymbol Min Typ Max Unit High-Level Input VoltageAll Pins Except XIN and SCLKXIN SCLK V IH0.6 VD+(VD+)-0.5(VD+) - 0.45------V V V Low-Level Input VoltageAll Pins Except XIN and SCLKXIN SCLKV IL------0.16 VD+0.30.6V V V High-Level Output VoltageAll Pins Except CPD and SDO, I out = -400 µACPD, I out = -4.0 mA SDO, I out = -5.0 mA V OH(VA+) - 0.3(VD+) - 1.0(VD+) - 1.0------V V V Low-Level Output VoltageAll Pins Except CPD and SDO, I out = 400 µACPD, I out = 2 mA SDO, I out = 5.0 mA V OL------0.30.40.4V V V Input Leakage Current I in -±1±10µA 3-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFDYNAMIC CHARACTERISTICSRECOMMENDED OPERATING CONDITIONS (AGND, DGND = 0 V; See Note 20.)Notes:20.All voltages with respect to ground.ABSOLUTE MAXIMUM RATINGS (AGND, DGND = 0 V; See Note 20.)Notes:21.No pin should go more negative than NBV - 0.3V.22.Applies to all pins including continuous overvoltage conditions at the analog input (AIN) pins.23.Transient current of up to 100mA will not cause SCR latch-up. Maximum input current for a powersupply pin is ±50mA.24.Total power dissipation, including all input currents and output currents.WARNING:Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.ParameterSymbol Ratio Unit Modulator Sampling Frequencyf s XIN/4Hz Filter Settling Time to 1/2 LSB (Full Scale Step)t s1/f outsParameterSymbol Min Typ Max Unit DC Power Supplies Positive Digital Positive Analog VD+VA+ 2.74.75 5.05.0 5.255.25V V Analog Reference Voltage (VREF+) - (VREF-)VRef diff 1.0 2.5VA+V Negative Bias VoltageNBV-1.8-2.1-2.5VParameterSymbol Min Typ Max Unit DC Power Supplies(Note 21)Positive Digital Positive Analog VD+VA+-0.3-0.3--+6.0+6.0V V Negative Bias VoltageNegative Potential NBV +0.3-2.1-3.0V Input Current, Any Pin Except Supplies (Note 22 and 23)I IN --±10mA Output Current I OUT --±25mA Power Dissipation (Note 24)PDN --500mW Analog Input Voltage VREF pins AIN PinsV INR V INA NBV -0.3NBV -0.3--(VA+) + 0.3(VA+) + 0.3V V Digital Input VoltageV IND -0.3-(VD+) + 0.3V Ambient Operating Temperature T A -40-85°C Storage TemperatureT stg-65-150°CSWITCHING CHARACTERISTICS (T A = 25° C; VA+ = 5 V ±5%; VD+ = 3.0 V ±10% or 5 V ±5%;Levels: Logic 0 = 0 V, Logic 1 = VD+; C L = 50 pF.))Notes:25.Device parameters are specified with a 32.768kHz clock; however, clocks up to 200kHz(CS5522/24/28) or 130kHz (CS5521/23) can be used for increased throughput.26.Specified using 10% and 90% points on waveform of interest. Output loaded with 50pF.27.Oscillator start-up time varies with crystal parameters. This specification does not apply when using anexternal clock source.28.Applicable when SCLK is continuously running.Specifications are subject to change without notice.ParameterSymbol Min Typ MaxUnitMaster Clock Frequency (Note 25)External Clock or Internal Oscillator (CS5522/24/28)(CS5521/23)XIN303032.76832.768200130kHz kHz Master Clock Duty Cycle 40-60%Rise Times(Note 26)Any Digital Input Except SCLKSCLKAny Digital Output t rise-----50 1.0100-µs µs ns Fall Times(Note 26)Any Digital Input Except SCLKSCLKAny Digital Output t fall-----50 1.0100-µs µs ns Start-upOscillator Start-up Time XTAL = 32.768 kHz(Note 27)t ost -500-ms Power-on Reset Period t por-2006-XIN cycles Serial Port Timing Serial Clock FrequencySCLK 0-2MHz SCLK Falling to CS Falling for continuous running SCLK(Note 28)t 0100--ns Serial ClockPulse Width High Pulse Width Lowt 1t 2250250----ns ns SDI Write TimingCS Enable to Valid Latch Clock t 350--ns Data Set-up Time prior to SCLK rising t 450--ns Data Hold Time After SCLK Rising t 5100--ns SCLK Falling Prior to CS Disablet 6100--ns SDO Read TimingCS to Data Validt 7--150ns SCLK Falling to New Data Bit t 8--150ns CS Rising to SDO Hi-Zt 9--150nsFigure 1. Continuous Running SCLK Timing (Not to Scale)Figure 2. SDI Write Timing (Not to Scale)Figure 3. SDO Read Timing (Not to Scale)2. GENERAL DESCRIPTIONThe CS5521/22/23/24/28 are highly integrated ∆ΣAnalog-to-Digital Converters (ADCs) which use charge-balance techniques to achieve 16-bit (CS5521/23) and 24-bit (CS5522/24/28) perfor-mance. The ADCs come as either two-channel (CS5521/22), four-channel (CS5523/24), or eight-channel (CS5528) devices, and include a low input current, chopper-stabilized instrumentation ampli-fier. To permit selectable input spans of 25mV, 55mV, 100mV, 1V, 2.5V, and 5V, the ADCs in-clude a PGA (programmable gain amplifier). To accommodate ground-based thermocouple applica-tions, the devices include a CPD (Charge Pump Drive) which provides a negative bias voltage to the on-chip amplifiers.These devices also include a fourth order DS mod-ulator followed by a digital filter which provides eight selectable output word rates of 1.88Hz, 3.76Hz, 7.51Hz, 15Hz, 30Hz, 61.6Hz, 84.5Hz, and 101.1Hz (XIN=32.768kHz). The devices are capable of producing output update rates up to 617Hz when a 200kHz clock is used (CS5522/24/28) or up to 401Hz using a 130kHz clock (CS5521/23). Further note that the digital fil-ters are designed to settle to full accuracy within one conversion cycle and simultaneously reject both 50Hz and 60Hz interference when operated at word rates below 30Hz (assuming a XIN clock frequency of 32.768kHz).To ease communication between the ADCs and a micro-controller, the converters include an easy to use three-wire serial interface which is SPI™ and Microwire™ compatible.2.1 Analog InputFigure4 illustrates a block diagram of the analog in-put signal path inside the CS5521/22/23/24/28. The front end consists of a multiplexer (break before make configuration), a chopper-stabilized instru-mentation amplifier with fixed gain of 20X, coarse/fine charge buffers, and a programmable gain section. For the 25mV, 55mV, and 100mV input ranges, the input signals are amplified by the 20X in-strumentation amplifier. For the 1V, 2.5V, and 5V input ranges, the instrumentation amplifier is by-passed and the input signals are connected to the Programmable Gain block via coarse/fine charge buffers.Figure 4. Multiplexer Configurations2.1.1 Instrumentation AmplifierThe instrumentation amplifier is chopper stabilized and is activated any time conversions are performed with the low level input ranges, ≤100mV. The am-plifier is powered from VA+ and from the NBV (Negative Bias Voltage) pin allowing the CS5521/22/23/24/28 to be operated in either of two analog input configurations. The NBV pin can be bi-ased to a negative voltage between -1.8V and -2.5V, or tied to AGND (for the CS5528, NBV has to be between -1.8V and -2.5V for the ranges below 100mV when the amplifier is engaged). The com-mon-mode plus signal range of the instrumentation amplifier is 1.85V to 2.65V with NBV grounded. The common-mode plus signal range of the instru-mentation amplifier is -0.150V to 0.950V with NBV between -1.8V to -2.5V. Whether NBV is tied between -1.8V and -2.5V or tied to AGND, the (Common Mode + Signal) input on AIN+ and AIN- must stay between NBV and VA+.Figure5illustrates an analog input model for the ADCs when the instrumentation amplifier is en-gaged. The CVF (sampling) input current for each of the analog input pins depends on the CFS1 and CFS0 (Chop Frequency Select) bits in the configu-ration register (see Configuration Register for de-tails). Note that the CVF current is lowest with the CFS bits in their default states (cleared to logic 0s). Further note that the CVF current into the instru-mentation amplifier is less than 300 pA over -40°C to +85°C. Note that Figure5 is for input current modeling only. For physical input capacitance see ‘Input Capacitance’ specification under ANALOG CHARACTERISTICS. Also refer to Applications Note AN30 “Switched-Capacitor A/D Converter Input Structures” for more details on input models and input sampling currents.Note: Residual noise appears in the converter’s baseband for output word rates greater than 61.6Hz if the CFS bits are logic 0 (chop clock=256Hz). For word rates of 30Hz and lower, 256Hz chopping is recommended, and for 61.6Hz, 84.5Hz and 101.1Hz filters, 4096Hz chopping is recommended.2.1.2 Coarse/Fine Charge BuffersThe unity gain buffers are activated any time conver-sions are performed with the high level inputs rang-es, 1V, 2.5V, and 5V. The unity gain buffers are designed to accommodate rail to rail input signals. The common-mode plus signal range for the unity gain buffer amplifier is NBV to VA+.Typical CVF (sampling) current for the unity gain buffer amplifiers is about 10nA (XIN=32.768kHz, see Figure6).Figure 5. Input Models for AIN+ and AIN- pins, ≤(100 mV Input Ranges Figure 6. Input Models for AIN+ and AIN- pins,>100 mV input ranges2.1.3 Analog Input Span ConsiderationsThe CS5521/22/23/24/28 is designed to measure full scale ranges of 25mV, 55mV, 100mV, 1V,2.5V and 5V. Other full scale values can be ac-commodated by performing a system calibration within the limits specified. See the Calibration sec-tion for more details. Another way to change the full scale range is to increase or to decrease the voltage reference to a voltage other than 2.5 . See the Voltage Reference section for more details. Three factors set the operating limits for the input span. They include: instrumentation amplifier satu-ration, modulator 1’s density, and a lower reference voltage. When the 25mV, 55mV or 100mV range is selected, the input signal (including the common mode voltage and the amplifier offset voltage)must not cause the 20X amplifier to saturate in ei-ther its input stage or output stage. To prevent sat-uration the absolute voltages on AIN+ and AIN-must stay within the limits specified (refer to the Analog Input section). Additionally, the differen-tial output voltage of the amplifier must not exceed 2.8V. The equationABS(VIN + VOS) x 20 = 2.8Vdefines the differential output limit, whereVIN = (AIN+) - (AIN-)is the differential input voltage and VOS is the ab-solute maximum offset voltage for the instrumenta-tion amplifier (VOS will not exceed 40mV). If the differential output voltage from the amplifier ex-ceeds 2.8V, the amplifier may saturate, which will cause a measurement error.The input voltage into the modulator must not cause the modulator to exceed a low of 20 percent or a high of 80 percent 1's density. The nominal full scale input span of the modulator (from 30 percent to 70 percent 1’s density) is determined by the VREF voltage divided by the Gain Factor. See Table 1 to determine if the CS5521/22/23/24/28are being used properly. For example, in the 55mV range, to determine the nominal input volt-age to the modulator, divide VREF (2.5V) by the Gain Factor (2.2727).When a smaller voltage reference is used, the re-sulting code widths are smaller causing the con-verter output codes to exhibit more changing codes for a fixed amount of noise. Table 1 is based upon a VREF =2.5V. For other values of VREF, the values in Table 1 must be scaled accordingly.2.1.4 Measuring Voltages Higher than 5 VSome systems require the measurement of voltages greater than 5V. The input current of the instru- Note:1.The converter’s actual input range, the delta-sigma’s nominal full scale input, and the delta-sigma’smaximum full scale input all scale directly with the value of the voltage reference. The values in the table assume a 2.5 V VREF voltage.2.The 2.8V limit at the output of the 20X amplifier is the differential output voltage.Input Range (1)Max. Differential Output20X AmplifierVREF Gain Factor∆-Σ Nominal (1)Differential Input∆-Σ(1)Max. Input ±25 mV 2.8 V (2) 2.5V 5±0.5 V ±0.75 V ±55 mV 2.8 V (2) 2.5V 2.272727...±1.1 V ±1.65 V ±100 mV 2.8 V (2)2.5V 1.25±2.0 V ±3.0 V ±1.0 V - 2.5V 2.5±1.0 V ±1.5 V ±2.5 V - 2.5V 1.0±2.5 V ±5.0 V ±5.0 V- 2.5V0.5±5.0 V0V, VA+Table 1. Relationship between Full Scale Input, Gain Factors, and Internal AnalogSignal Limitations。

自适应Shearlet域约束的全变差图像去噪朱华生;邓承志【期刊名称】《计算机工程》【年(卷),期】2013(039)001【摘要】采用传统非线性扩散图像去嗓方法得到的图像边缘模糊,为此,提出一种有限自适应Shearlet域约束的极小化变分图像去噪算法.通过自适应阈值收缩Shearlet系数,保留图像纹理与边缘空间,利用全变差极小化平滑空间,建立全变差正则化的能量泛函去噪模型.实验结果表明,该算法能在减少图像噪声的同时,保留图像边缘信息,对含有丰富纹理结构的图像,去噪性能更佳.%In this paper, an adaptive Shearlet domain regularized minimization total variation image denoising algorithm is proposed, which can overcome the problem of the traditional nonlinear diffusion image denoising methods. The texture and edge domain is adaptively shrinkaged in Shearlet domain. And then, a total variation regularized energy functional model with restrictions on the finite adaptive shearlet domain is used to deal with smooth domain. Experimental results show that this algorithm can reduce the noise and preserve the edge information, especially to the images containing abundant texture.【总页数】4页(P221-224)【作者】朱华生;邓承志【作者单位】南昌工程学院信息工程学院,南昌330099;南昌工程学院信息工程学院,南昌330099【正文语种】中文【中图分类】TN919.73【相关文献】1.Shearlet变换域自适应图像去噪算法 [J], 朱华生;徐晨光2.基于自适应shearlet域约束下的图像去噪研究 [J], 王丰斌;杨坷巍3.非下采样Shearlet域多变量模型的图像去噪 [J], 刘巧红;林敏;李广超4.基于自适应shearlet域约束下的图像去噪研究 [J], 王丰斌;杨坷巍5.一种改进全变差正则化的Shearlet自适应带钢图像去噪算法 [J], 韩英莉因版权原因,仅展示原文概要,查看原文内容请购买。

AAMI TIR29:2002技术信息报告辐照灭菌过程控制指南AAMI 美国医疗器械促进协会(Association for the Advancement of MEDICALInstrumentation)AAMI 技术信息报告AAMI TIR29:2002辐照灭菌过程控制指南Approved 16 July 2002 by美国医疗器械促进协会摘要: 本技术信息报告增加了ANSI/AAMI/ISO 11137所界定的光子,电子束灭菌的剂量场的建立和规范,过程确认,和常规控制等辐射灭菌。

尽管轫致辐射的要求相似,但在这项工作开始的时候缺乏关于轫致辐射装置的设计和运行的经验。

所以轫致辐射不包括在此指南之内。

关键词: 辐射剂量场, 过程确认, 日常加工,剂量确认美国医疗器械促进协会技术信息报告信息技术报告是美国医疗器械促进协会标准局的刊物,它是为特殊的医疗技术提供。

提交到信息技术报告的材料需要更多专家的意见,发表的信息也得是用的,因为很多行业都急切需要它。

信息技术报告与标准和操作规程建议,读者应该理解这些文件的不同之处。

标准和工业标准由正式的委员会通过收集所有正确的意见和观点,此过程由美国医疗器械促进协会标准局和美国国际标准机构完成。

信息技术报告作为一个标准审核的过程不是一样。

但是,信息技术报告由技术委员会和美国医疗器械促进协会标准出版社发布。

另外一个不同的地方,尽管标准和信息技术报告都需要定期审查,一个标准必须经过重申,修改,或撤回,通常每五年或十年需要正式的被认可。

对于信息技术报告来说,美国医疗器械促进协会和技术委员会达成一致,规定自出版日期五年后(作为一个周期)进行审查报告是否有用,检查信息是否切题和具有实用性,如果信息没有实用性了,此信息技术报告就被删掉。

信息技术报告肯发展,因为它比标准和操作规程建议能更好响应基础安全和性能问题。

或者说因为达成共识是非常困难甚至不可能。

信息技术报告与标准不同,它允许在技术问题上由不同的观点。

MPU-6881 Product Specification Revision 1.0TABLE OF CONTENTSTABLE OF FIGURES (4)TABLE OF TABLES (5)1DOCUMENT INFORMATION (6)1.1R EVISION H ISTORY (6)1.2P URPOSE AND S COPE (7)1.3P RODUCT O VERVIEW (7)1.4A PPLICATIONS (7)2FEATURES (8)2.1G YROSCOPE F EATURES (8)2.2A CCELEROMETER F EATURES (8)2.3A DDITIONAL F EATURES (8)3ELECTRICAL CHARACTERISTICS (9)3.1G YROSCOPE S PECIFICATIONS (9)3.2A CCELEROMETER S PECIFICATIONS (10)3.3E LECTRICAL S PECIFICATIONS (11)3.4I2C T IMING C HARACTERIZATION (15)3.5SPI T IMING C HARACTERIZATION (16)3.6A BSOLUTE M AXIMUM R ATINGS (18)4APPLICATIONS INFORMATION (19)4.1P IN O UT D IAGRAM AND S IGNAL D ESCRIPTION (19)4.2T YPICAL O PERATING C IRCUIT (20)4.3B ILL OF M ATERIALS FOR E XTERNAL C OMPONENTS (20)4.4B LOCK D IAGRAM (21)4.5O VERVIEW (21)4.6T HREE-A XIS MEMS G YROSCOPE WITH 16-BIT ADC S AND S IGNAL C ONDITIONING (22)4.7T HREE-A XIS MEMS A CCELEROMETER WITH 16-BIT ADC S AND S IGNAL C ONDITIONING (22)4.8I2C AND SPI S ERIAL C OMMUNICATIONS I NTERFACES (22)4.9S ELF-T EST (24)4.10C LOCKING (25)4.11S ENSOR D ATA R EGISTERS (25)4.12FIFO (25)4.13I NTERRUPTS (25)4.14D IGITAL-O UTPUT T EMPERATURE S ENSOR (25)4.15B IAS AND LDO S (26)4.16C HARGE P UMP (26)4.17S TANDARD P OWER M ODES (26)5PROGRAMMABLE INTERRUPTS (27)6DIGITAL INTERFACE (28)6.1I2C AND SPI S ERIAL I NTERFACES (28)6.2I2C I NTERFACE (28)6.3I2C C OMMUNICATIONS P ROTOCOL (28)6.4I2C T ERMS (31)6.5SPI I NTERFACE (32)7SERIAL INTERFACE CONSIDERATIONS (32)7.1MPU-6881S UPPORTED I NTERFACES (33)8ASSEMBLY (34)8.1O RIENTATION OF A XES (34)8.2P ACKAGE D IMENSIONS (35)9PART NUMBER PACKAGE MARKING (36)10RELIABILITY (37)10.1Q UALIFICATION T EST P OLICY (37)10.2Q UALIFICATION T EST P LAN (37)11REFERENCE (38)Table of FiguresFigure 1 I2C Bus Timing Diagram (15)Figure 2 SPI Bus Timing Diagram (16)Figure 3 Pin out Diagram for MPU-6881 3.0x3.0x0.9mm QFN (19)Figure 4 MPU-6881 QFN Application Schematic. (a) I2C operation, (b) SPI operation. (20)Figure 5 MPU-6881 Block Diagram (21)Figure 6 MPU-6881 Solution Using I2C Interface (23)Figure 7 MPU-6881 Solution Using SPI Interface (24)Figure 8 START and STOP Conditions (29)Figure 9 Acknowledge on the I2C Bus (29)Figure 10 Complete I2C Data Transfer (30)Figure 11 Typical SPI Master / Slave Configuration (32)Figure 12 I/O Levels and Connections (33)Figure 13 Orientation of Axes Sensitivity and Polarity of Rotation (34)Table of TablesTable 1 Gyroscope Specifications (9)Table 2 Accelerometer Specifications (10)Table 3 D.C. Electrical Characteristics (11)Table 4 A.C. Electrical Characteristics (13)Table 5 Other Electrical Specifications (14)Table 6 I2C Timing Characteristics (15)Table 7 SPI Timing Characteristics (16)Table 8 fCLK = 20MHz (17)Table 9 Absolute Maximum Ratings (18)Table 10 Signal Descriptions (19)Table 11 Bill of Materials (20)Table 12 Standard Power Modes for MPU-6881 (26)Table 13 Table of Interrupt Sources (27)Table 14 Serial Interface (28)Table 15 I2C Terms (31)1 Document Information1.2 Purpose and ScopeThis document is a preliminary product specification, providing a description, specifications, and design related information on the MPU-6881™ MotionTracking device. The device is housed in a small 3x3x0.9mm 24-pin QFN package.Specifications are subject to change without notice. Final specifications will be updated based upon characterization of production silicon. For references to register map and descriptions of individual registers, please refer to the MPU-6881 Register Map and Register Descriptions document.1.3 Product OverviewThe MPU-6881 is a 6-axis MotionTracking device that combines a 3-axis gyroscope, and a 3-axis accelerometer in a small 3x3x0.9mm (24-pin QFN) package. It also features a 4096-byte FIFO that can lower the traffic on the serial bus interface, and reduce power consumption by allowing the system processor to burst read sensor data and then go into a low-power mode. With its dedicated I2C sensor bus, the MPU-6881 directly accepts inputs from external I2C devices. MPU-6881, with its 6-axis integration, enables manufacturers to eliminate the costly and complex selection, qualification, and system level integration of discrete devices, guaranteeing optimal motion performance for consumers. MPU-6881 is also designed to interface with multiple non-inertial digital sensors, such as pressure sensors, on its auxiliary I2C port.The gyroscope has a programmable full-scale range of ±250, ±500, ±1000, and ±2000 degrees/sec. The accelerometer has a user-programmable accelerometer full-scale range of ±2g, ±4g, ±8g, and ±16g. Factory-calibrated initial sensitivity of both sensors reduces production-line calibration requirements.Other industry-leading features include on-chip 16-bit ADCs, programmable digital filters, a precision clock with 1% drift from -40°C to 85°C, an embedded temperature sensor, and programmable interrupts. The device features I2C and SPI serial interfaces, a VDD operating range of 1.71 to 3.45V, and a separate digital IO supply, VDDIO from 1.71V to 3.45V.Communication with all registers of the device is performed using either I2C at 400kHz or SPI at 1MHz. For applications requiring faster communications, the sensor and interrupt registers may be read using SPI at 20MHz.By leveraging its patented and volume-proven CMOS-MEMS Fabrication platform, which integrates MEMS wafers with companion CMOS electronics through wafer-level bonding, InvenSense has driven the package size down to a footprint and thickness of 3x3x0.9mm (24-pin QFN), to provide a very small yet high performance low cost package. The device provides high robustness by supporting 10,000g shock reliability.1.4 Applications∙TouchAnywhere™ technology (for “no touch” UI Application Control/Navigation)∙MotionCommand™ technology (for Gesture S hort-cuts)∙Motion-enabled game and application framework∙Location based services, points of interest, and dead reckoning∙Handset and portable gaming∙Motion-based game controllers∙3D remote controls for Internet connected DTVs and set top boxes, 3D mice∙Wearable sensors for health, fitness and sports2 Features2.1 Gyroscope FeaturesThe triple-axis MEMS gyroscope in the MPU-6881 includes a wide range of features:∙Digital-output X-, Y-, and Z-axis angular rate sensors (gyroscopes) with a user-programmable full-scale range of ±250, ±500, ±1000, and ±2000°/sec and integrated 16-bit ADCs ∙Digitally-programmable low-pass filter∙Gyroscope operating current: 3.2mA∙Factory calibrated sensitivity scale factor∙Self-test2.2 Accelerometer FeaturesThe triple-axis MEMS accelerometer in MPU-6881 includes a wide range of features:∙Digital-output X-, Y-, and Z-axis accelerometer with a programmable full scale range of ±2g, ±4g, ±8g and ±16g and integrated 16-bit ADCs∙Accelerometer normal operating current: 450µA∙Low power accelerometer mode current: 7.27µA at 0.98Hz, 18.65µA at 31.25Hz∙User-programmable interrupts∙Wake-on-motion interrupt for low power operation of applications processor∙Self-test2.3 Additional FeaturesThe MPU-6881 includes the following additional features:∙Auxiliary master I2C bus for reading data from external sensors (e.g. magnetometer)∙ 3.4mA operating current when all 6 motion sensing axes are active∙VDD supply voltage range of 1.8 – 3.3V ± 5%∙VDDIO reference voltage of 1.8 – 3.3V ± 5% for auxiliary I2C devices∙Smallest and thinnest QFN package for portable devices: 3x3x0.9mm (24-pin QFN)∙Minimal cross-axis sensitivity between the accelerometer and gyroscope axes∙4096 byte FIFO buffer enables the applications processor to read the data in bursts∙Digital-output temperature sensor∙User-programmable digital filters for gyroscope, accelerometer, and temp sensor∙10,000 g shock tolerant∙400kHz Fast Mode I2C for communicating with all registers∙1MHz SPI serial interface for communicating with all registers∙20MHz SPI serial interface for reading sensor and interrupt registers∙MEMS structure hermetically sealed and bonded at wafer level∙RoHS and Green compliant3 Electrical Characteristics3.1 Gyroscope SpecificationsTypical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T A=25°C, unless otherwise noted.Please refer to the following document for information on Self-Test: MPU-6500 Accelerometer and Gyroscope Self-Test Implementation; AN-MPU-6500A-02.Table 1 Gyroscope SpecificationsNotes:1. Derived from validation or characterization of parts, not guaranteed in production.3.2 Accelerometer SpecificationsTypical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T A=25°C, unless otherwise noted.Please refer to the following document for information on Self-Test: MPU-6500 Accelerometer and Gyroscope Self-Test Implementation; AN-MPU-6500A-02.Table 2 Accelerometer SpecificationsNotes:1. Derived from validation or characterization of parts, not guaranteed in production.3.3 Electrical Specifications3.3.1 D.C. Electrical CharacteristicsTypical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T A=25°C, unless otherwise noted.Table 3 D.C. Electrical CharacteristicsNotes:1. Derived from validation or characterization of parts, not guaranteed in production.2. Accelerometer Low Power Mode supports the following output data rates (ODRs): 0.24, 0.49, 0.98,1.95, 3.91, 7.81, 15.63, 31.25, 62.50, 125, 250, 500Hz. Supply current for any update rate can becalculated as:a. Supply Current in µA = 6.9 + Update Rate * 0.3763.3.2 A.C. Electrical CharacteristicsTypical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T A=25°C, unless otherwise noted.Table 4 A.C. Electrical CharacteristicsNotes:1. Derived from validation or characterization of parts, not guaranteed in production.3.3.3 Other Electrical SpecificationsTypical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T A=25°C, unless otherwise noted.Table 5 Other Electrical SpecificationsNotes:1. Derived from validation or characterization of parts, not guaranteed in production.3.4 I2C Timing CharacterizationTypical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T A=25°C, unless otherwise noted.Table 6 I2C Timing CharacteristicsNotes:1.Timing Characteristics apply to both Primary and Auxiliary I2C Bus2.Based on characterization of 5 parts over temperature and voltage as mounted on evaluation board or in socketsFigure 1 I2C Bus Timing Diagram3.5 SPI Timing CharacterizationTypical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T A=25°C, unless otherwise noted.Table 7 SPI Timing CharacteristicsNotes:3.Based on characterization of 5 parts over temperature and voltage as mounted on evaluation board or in socketsFigure 2 SPI Bus Timing Diagram3.5.1 fSCLK = 20MHzTable 8 fCLK = 20MHzNotes:1.Based on characterization of 5 parts over temperature and voltage as mounted on evaluation board or in sockets3.6 Absolute Maximum RatingsStress above those listed as “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to the absolute maximum ratings conditions for extended periods may affect device reliability.Table 9 Absolute Maximum Ratings4 Applications Information4.1Pin Out Diagram and Signal DescriptionTable 10 Signal DescriptionsA U X _C LV D D I OS D O / A D 0R E G O U TF S Y N CI N TS C L / S C L Kn C SR E S V S D A / S D IA U X _D AR E S VNC NC NC NC NC NCFigure 3 Pin out Diagram for MPU-6881 3.0x3.0x0.9mm QFN4.2Typical Operating Circuit– 3.3VDC m F1.8 –AD0– 3.3VDC m F1.8 –SD0(a)(b)Figure 4 MPU-6881 QFN Application Schematic. (a) I2C operation, (b) SPI operation.4.3Bill of Materials for External Components Table 11 Bill of Materials4.4 Block DiagramVDD GND PLLFILTFigure 5 MPU-6881 Block Diagram4.5 OverviewThe MPU-6881 is comprised of the following key blocks and functions:∙Three-axis MEMS rate gyroscope sensor with 16-bit ADCs and signal conditioning ∙Three-axis MEMS accelerometer sensor with 16-bit ADCs and signal conditioning ∙Primary I2C and SPI serial communications interfaces∙Auxiliary I2C serial interface∙Self-Test∙Clocking∙Sensor Data Registers∙FIFO∙Interrupts∙Digital-Output Temperature Sensor∙Bias and LDOs∙Charge Pump∙Standard Power Modes4.6 Three-Axis MEMS Gyroscope with 16-bit ADCs and Signal ConditioningThe MPU-6881 consists of three independent vibratory MEMS rate gyroscopes, which detect rotation about the X-, Y-, and Z- Axes. When the gyros are rotated about any of the sense axes, the Coriolis Effect causes a vibration that is detected by a capacitive pickoff. The resulting signal is amplified, demodulated, and filtered to produce a voltage that is proportional to the angular rate. This voltage is digitized using individual on-chip 16-bit Analog-to-Digital Converters (ADCs) to sample each axis. The full-scale range of the gyro sensors may be digitally programmed to ±250, ±500, ±1000, or ±2000 degrees per second (dps). The ADC sample rate is programmable from 8,000 samples per second, down to 3.9 samples per second, and user-selectable low-pass filters enable a wide range of cut-off frequencies.4.7 Three-Axis MEMS Accelerometer with 16-bit ADCs and Signal ConditioningThe MPU-6881’s 3-Axis accelerometer uses separate proof masses for each axis. Acceleration along a particular axis induces displacement on the corresponding proof mass, and capacitive sensors detect the displacement differentially. The MPU-6881’s architecture reduces the accelerometers’ susceptibility to fabrication variations as well as to thermal drift. When the device is placed on a flat surface, it will measure 0g on the X- and Y-axes and +1g on the Z-axis. The accelerometer s’ scale factor is calibrated at the factory and is nominally independent of supply voltage. Each sensor has a dedicated sigma-delta ADC for providing digital outputs. The full scale range of the digital output can be adjusted to ±2g, ±4g, ±8g, or ±16g.4.8 I2C and SPI Serial Communications InterfacesThe MPU-6881 communicates to a system processor using either a SPI or an I2C serial interface. The MPU-6881 always acts as a slave when communicating to the system processor. The LSB of the of the I2C slave address is set by pin 4 (AD0).4.8.1 MPU-6881 Solution Using I2C InterfaceIn the figure below, the system processor is an I2C master to the MPU-6881.Figure 6 MPU-6881 Solution Using I2C Interface4.8.2 MPU-6881 Solution Using SPI InterfaceIn the figure below, the system processor is an SPI master to the MPU-6881. Pins 2, 3, 4, and 5 are used to support the SCLK, SDI, SDO, and CS signals for SPI communications.Figure 7 MPU-6881 Solution Using SPI Interface4.9 Self-TestPlease refer to the register map document for more details on self-test.Self-test allows for the testing of the mechanical and electrical portions of the sensors. The self-test for each measurement axis can be activated by means of the gyroscope and accelerometer self-test registers (registers 13 to 16).When the self-test is activated, the electronics cause the sensors to be actuated and produce an output signal. The output signal is used to observe the self-test response.The self-test response is defined as follows:Self-test response = Sensor output with self-test enabled – Sensor output without self-test enabled The self-test response for each gyroscope axis is defined in the gyroscope specification table, while that for each accelerometer axis is defined in the accelerometer specification table.When the value of the self-test response is within the specified min/max limits of the product specification, the part has passed self-test. When the self-test response exceeds the min/max values, the part is deemed to have failed self-test. It is recommended to use InvenSense MotionApps software for executing self-test.4.10 ClockingThe MPU-6881 has a flexible clocking scheme, allowing a variety of internal clock sources to be used for the internal synchronous circuitry. This synchronous circuitry includes the signal conditioning and ADCs, and various control circuits and registers. An on-chip PLL provides flexibility in the allowable inputs for generating this clock.Allowable internal sources for generating the internal clock are:∙An internal relaxation oscillator∙Any of the X, Y, or Z gyros (MEMS oscillators with a variation of ±1% over temperature)Selection of the source for generating the internal synchronous clock depends on the requirements for power consumption and clock accuracy. These requirements will most likely vary by mode of operation.There are also start-up conditions to consider. When the MPU-6881 first starts up, the device uses its internal clock until programmed to operate from another source. This allows the user, for example, to wait for the MEMS oscillators to stabilize before they are selected as the clock source.4.11 Sensor Data RegistersThe sensor data registers contain the latest gyro, accelerometer, auxiliary sensor, and temperature measurement data. They are read-only registers, and are accessed via the serial interface. Data from these registers may be read anytime.4.12 FIFOThe MPU-6881 contains a 4096-byte FIFO register that is accessible via the Serial Interface. The FIFO configuration register determines which data is written into the FIFO. Possible choices include gyro data, accelerometer data, temperature readings, auxiliary sensor readings, and SYNC input. A FIFO counter keeps track of how many bytes of valid data are contained in the FIFO. The FIFO register supports burst reads. The interrupt function may be used to determine when new data is available.For further information regarding the FIFO, please refer to the MPU-6881 Register Map and Register Descriptions document.4.13 InterruptsInterrupt functionality is configured via the Interrupt Configuration register. Items that are configurable include the INT pin configuration, the interrupt latching and clearing method, and triggers for the interrupt. Items that can trigger an interrupt are (1) Clock generator locked to new reference oscillator (used when switching clock sources); (2) new data is available to be read (from the FIFO and Data registers); (3) accelerometer event interrupts; and (4) the MPU-6881 did not receive an acknowledge from an auxiliary sensor on the secondary I2C bus. The interrupt status can be read from the Interrupt Status register.For further information regarding interrupts, please refer to the MPU-6881 Register Map and Register Descriptions document.4.14 Digital-Output Temperature SensorAn on-chip temperature sensor and ADC are used to measure the MPU-6881 die temperature. The readings from the ADC can be read from the FIFO or the Sensor Data registers.4.15 Bias and LDOsThe bias and LDO section generates the internal supply and the reference voltages and currents required by the MPU-6881. Its two inputs are an unregulated VDD and a VDDIO logic reference supply voltage. The LDO output is bypassed by a capacitor at PLLFILT. For further details on the capacitor, please refer to the Bill of Materials for External Components.4.16 Charge PumpAn on-chip charge pump generates the high voltage required for the MEMS oscillators.4.17 Standard Power ModesThe following table lists the user-accessible power modes for MPU-6881.Table 12 Standard Power Modes for MPU-6881Notes:1. Power consumption for individual modes can be found in section 3.3.1.5 Programmable InterruptsThe MPU-6881 has a programmable interrupt system which can generate an interrupt signal on the INT pin. Status flags indicate the source of an interrupt. Interrupt sources may be enabled and disabled individually.Table 13 Table of Interrupt SourcesFor information regarding the interrupt enable/disable registers and flag registers, please refer to the MPU-6881 Register Map and Register Descriptions document. Some interrupt sources are explained below.6 Digital Interface6.1 I2C and SPI Serial InterfacesThe internal registers and memory of the MPU-6881 can be accessed using either I2C at 400 kHz or SPI at 1MHz. SPI operates in four-wire mode.Table 14 Serial InterfaceNote:To prevent switching into I2C mode when using SPI, the I2C interface should be disabled by setting the I2C_IF_DIS configuration bit. Setting this bit should be performed immediately after waiting for the time specified by the “Start-Up Time for Reg ister Read/Write” in Section 6.3.For further information regarding the I2C_IF_DIS bit, please refer to the MPU-6881 Register Map and Register Descriptions document.6.2 I2C InterfaceI2C is a two-wire interface comprised of the signals serial data (SDA) and serial clock (SCL). In general, the lines are open-drain and bi-directional. In a generalized I2C interface implementation, attached devices can be a master or a slave. The master device puts the slave address on the bus, and the slave device with the matching address acknowledges the master.The MPU-6881 always operates as a slave device when communicating to the system processor, which thus acts as the master. SDA and SCL lines typically need pull-up resistors to VDD. The maximum bus speed is 400 kHz.The slave address of the MPU-6881 is b110100X which is 7 bits long. The LSB bit of the 7 bit address is determined by the logic level on pin AD0. This allows two MPU-6881s to be connected to the same I2C bus. When used in this configuration, the address of the one of the devices should be b1101000 (pin AD0 is logic low) and the address of the other should be b1101001 (pin AD0 is logic high).6.3 I2C Communications ProtocolSTART (S) and STOP (P) ConditionsCommunication on the I2C bus starts when the master puts the START condition (S) on the bus, which is defined as a HIGH-to-LOW transition of the SDA line while SCL line is HIGH (see figure below). The bus is considered to be busy until the master puts a STOP condition (P) on the bus, which is defined as a LOW to HIGH transition on the SDA line while SCL is HIGH (see figure below).Additionally, the bus remains busy if a repeated START (Sr) is generated instead of a STOP condition.SDASCLPSSTART condition STOP conditionFigure 8 START and STOP ConditionsData Format / AcknowledgeI2C data bytes are defined to be 8-bits long. There is no restriction to the number of bytes transmitted per data transfer. Each byte transferred must be followed by an acknowledge (ACK) signal. The clock for the acknowledge signal is generated by the master, while the receiver generates the actual acknowledge signal by pulling down SDA and holding it low during the HIGH portion of the acknowledge clock pulse.If a slave is busy and cannot transmit or receive another byte of data until some other task has been performed, it can hold SCL LOW, thus forcing the master into a wait state. Normal data transfer resumes when the slave is ready, and releases the clock line (refer to the following figure).DATA OUTPUT BYTRANSMITTER (SDA)DATA OUTPUT BYRECEIVER (SDA)SCL FROMMASTERSTARTacknowledgementconditionFigure 9 Acknowledge on the I2C BusCommunicationsAfter beginning communications with the START condition (S), the master sends a 7-bit slave addressfollowed by an 8thbit, the read/write bit. The read/write bit indicates whether the master is receiving data from or is writing to the slave device. Then, the master releases the SDA line and waits for the acknowledge signal (ACK) from the slave device. Each byte transferred must be followed by an acknowledge bit. To acknowledge, the slave device pulls the SDA line LOW and keeps it LOW for the high period of the SCL line. Data transmission is always terminated by the master with a STOP condition (P), thus freeing the communications line. However, the master can generate a repeated START condition (Sr), and address another slave without first generating a STOP condition (P). A LOW to HIGH transition on the SDA line while SCL is HIGH defines the stop condition. All SDA changes should take place when SCL is low, with the exception of start and stop conditions.SDASTART conditionSCLADDRESS R/W ACK DATAACK DATA ACKSTOP conditionSP1 – 789 1 – 789 1 – 789Figure 10 Complete I 2C Data TransferTo write the internal MPU-6881 registers, the master transmits the start condition (S), followed by the I 2Caddress and the write bit (0). At the 9thclock cycle (when the clock is high), the MPU-6881 acknowledges the transfer. Then the master puts the register address (RA) on the bus. After the MPU-6881 acknowledges the reception of the register address, the master puts the register data onto the bus. This is followed by the ACK signal, and data transfer may be concluded by the stop condition (P). To write multiple bytes after the last ACK signal, the master can continue outputting data rather than transmitting a stop signal. In this case, the MPU-6881 automatically increments the register address and loads the data to the appropriate register. The following figures show single and two-byte write sequences.Single-Byte Write SequenceBurst Write SequenceTo read the internal MPU-6881 registers, the master sends a start condition, followed by the I2C address and a write bit, and then the register address that is going to be read. Upon receiving the ACK signal from the MPU-6881, the master transmits a start signal followed by the slave address and read bit. As a result, the MPU-6881 sends an ACK signal and the data. The communication ends with a not acknowledge (NACK) signal and a stop bit from master. The NACK condition is defined such that the SDA line remains high at the 9th clock cycle. The following figures show single and two-byte read sequences.Single-Byte Read SequenceBurst Read Sequence6.4 I2C TermsTable 15 I2C Terms6.5 SPI InterfaceSPI is a 4-wire synchronous serial interface that uses two control lines and two data lines. The MPU-6881 always operates as a Slave device during standard Master-Slave SPI operation.With respect to the Master, the Serial Clock output (SCLK), the Serial Data Output (SDO) and the Serial Data Input (SDI) are shared among the Slave devices. Each SPI slave device requires its own Chip Select (CS) line from the master.CS goes low (active) at the start of transmission and goes back high (inactive) at the end. Only one CS line is active at a time, ensuring that only one slave is selected at any given time. The CS lines of the non-selected slave devices are held high, causing their SDO lines to remain in a high-impedance (high-z) state so that they do not interfere with any active devices.SPI Operational Features1. Data is delivered MSB first and LSB last2. Data is latched on the rising edge of SCLK3. Data should be transitioned on the falling edge of SCLK4. The maximum frequency of SCLK is 1MHz5. SPI read and write operations are completed in 16 or more clock cycles (two or more bytes). Thefirst byte contains the SPI Address, and the following byte(s) contain(s) the SPI data. The firstbit of the first byte contains the Read/Write bit and indicates the Read (1) or Write (0) operation.The following 7 bits contain the Register Address. In cases of multiple-byte Read/Writes, data istwo or more bytes:6. Supports Single or Burst Read/Writes.。