vhdl基础及经典实例开发pdf

- 格式:docx

- 大小:28.68 KB

- 文档页数:3

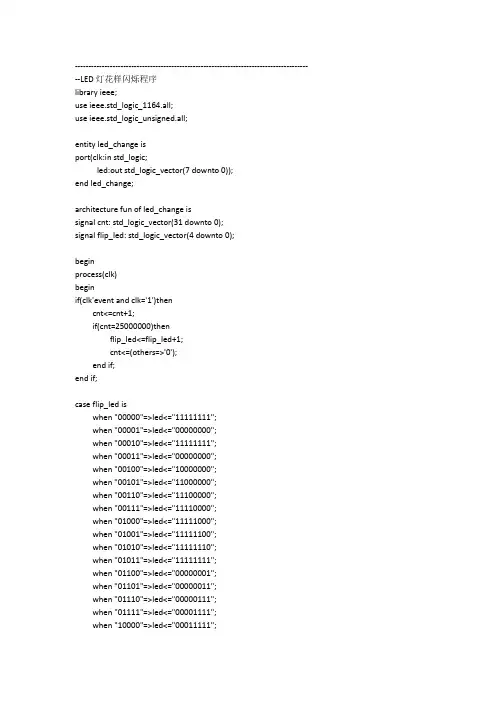

--------------------------------------------------------------------------------------- --LED灯花样闪烁程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led_change isport(clk:in std_logic;led:out std_logic_vector(7 downto 0));end led_change;architecture fun of led_change issignal cnt: std_logic_vector(31 downto 0);signal flip_led: std_logic_vector(4 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thencnt<=cnt+1;if(cnt=25000000)thenflip_led<=flip_led+1;cnt<=(others=>'0');end if;end if;case flip_led iswhen "00000"=>led<="11111111";when "00001"=>led<="00000000";when "00010"=>led<="11111111";when "00011"=>led<="00000000";when "00100"=>led<="10000000";when "00101"=>led<="11000000";when "00110"=>led<="11100000";when "00111"=>led<="11110000";when "01000"=>led<="11111000";when "01001"=>led<="11111100";when "01010"=>led<="11111110";when "01011"=>led<="11111111";when "01100"=>led<="00000001";when "01101"=>led<="00000011";when "01110"=>led<="00000111";when "01111"=>led<="00001111";when "10000"=>led<="00011111";when "10001"=>led<="00111111";when "10010"=>led<="01111111";when "10011"=>led<="11111111";when "10100"=>led<="00000000";when others =>led<="ZZZZZZZZ";end case;if(flip_led>"10100")thenflip_led<="00000";end if;end process;end fun;--拨码开关控制LED程序library ieee;use ieee.std_logic_1164.all;entity switch_led isport(key : in std_logic_vector(1 downto 0);led : out std_logic_vector(7 downto 0)); --八个led灯end switch_led;architecture fun of switch_led isbeginprocess(key)begincase key iswhen "00" => led <="00000000"; -- // "0"when "01" => led <="00001111"; -- // "1"when "10" => led <="11110000"; -- // "2"when "11" => led <="11111111"; -- // "3"when others => led <="ZZZZZZZZ";end case;end process;end;--按键消抖控制LED程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity stable_key isport(clk :in std_logic;key_in:in std_logic;key_out: out std_logic);end ;architecture fun of stable_key issignal cnt : integer range 0 to 1999999;signal key ,key_d : std_logic;beginprocess(clk)beginif clk'event and clk='1' thenif key /= key_in then -----键值变化开始计时10ms key_d <= key_in;cnt <= 0;elsif cnt=1999999 then ---10mskey_out <= not key_d;cnt <= 0;elsecnt <= cnt + 1 ;end if ;key<= key_in;end if ;end process;end ;--蜂鸣器电子琴程序library ieee;use ieee.std_logic_1164.all;entity digital_piano isport(key : in std_logic_vector(7 downto 0); --定义8个按键key1~key8clk : in std_logic; --时钟输入端50Mhzbeep: out std_logic); --蜂鸣器输出端end digital_piano;architecture fun of digital_piano issignal freq : integer range 0 to 50000;signal beep_reg: std_logic;beginbeep_process: process(clk,freq) --分频进程--本工程内核心进程,计数器的大小由counter决定variable cnt : integer range 0 to 50000;beginif clk'event and clk='1' thenif cnt < freq thencnt := cnt + 1;elsecnt := 0 ;beep_reg <=not beep_reg;end if;end if;end process beep_process;freq_process: process(key)begincase key iswhen "11111110" => freq <= 47774; ---------------------------------counter 计算公式:中音do的频率为523.3hz,为了在上个beep_pro进程中得到523的频率counter= 50*1000000/(523*2)when "11111101" => freq <= 42568; --中音re的频率为587.3hzwhen "11111011" => freq <= 37919; --中音mi的频率为659.3hzwhen "11110111" => freq <= 35791; --中音fa的频率为698.5hzwhen "11101111" => freq <= 31888; --中音sol的频率为784hzwhen "11011111" => freq <= 28409; --中音la的频率为880hzwhen "10111111" => freq <= 25309; --中音si的频率为987.8hzwhen "01111111" => freq <= 23912; --高音do的频率为1045.5hzwhen "01111101" => freq <= 21282; --高音re的频率为1174.7hzwhen "01111011" => freq <= 18961; --高音mi的频率为1318.5hzwhen "01110111" => freq <= 17897; --高音fa的频率为1396.9hzwhen "01101111" => freq <= 15944; --高音sol的频率为1568hzwhen "01011111" => freq <= 14205; --高音la的频率为1760hzwhen "00111111" => freq <= 12605; --高音si的频率为1975.5hzwhen others => freq <= 0;end case;end process freq_process;beep <= beep_reg;end;--数码管静态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity static_segled isport(clk : in std_logic;data:out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0));end ;architecture fun of static_segled issignal num : std_logic_vector(3 downto 0);signal cnt : integer range 0 to 12499999 ;beginsel <= "00000000"; --静态显示,全部位选中process(clk)beginif clk'event and clk='1' then --每四秒改变一次数字if cnt=12499999 thencnt<=0;num<= num + 1;elsecnt<= cnt + 1 ;end if ;end if ;end process;process(num)begincase num iswhen "0000" => data<=x"c0"; -- // "0"when "0001" => data<=x"f9"; -- // "1"when "0010" => data<=x"a4"; -- // "2"when "0011" => data<=x"b0"; -- // "3"when "0100" => data<=x"99"; -- // "4"when "0101" => data<=x"92"; -- // "5"when "0110" => data<=x"82"; -- // "6"when "0111" => data<=x"f8"; -- // "7"when "1000" => data<=x"80"; -- // "8"when "1001" => data<=x"90"; -- // "9"when "1010" => data<=x"88"; -- // "a"when "1011" => data<=x"83"; -- // "b"when "1100" => data<=x"c6"; -- // "c"when "1101" => data<=x"a1"; -- // "d"when "1110" => data<=x"86"; -- // "e"when "1111" => data<=x"8e"; -- // "f"when others => data<=x"ff";end case;end process;end ;--数码管动态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity dynamic_segled isport(clk : in std_logic;data: out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0) );end ;architecture fun of dynamic_segled issignal cnt: integer range 0 to 62449;signal flip_led: integer range 0 to 7;beginprocess(clk)beginif clk'event and clk='1' then ----- 动态扫描if cnt=62499 thencnt<=0;flip_led<=flip_led+1; -- 数据改变elsecnt<=cnt + 1;end if ;end if ;end process;process(flip_led)begincase flip_led is ---译码显示when 0 =>sel<="01111111";data<=x"c0";when 1 =>sel<="10111111";data<=x"f9";when 2 =>sel<="11011111";data<=x"a4";when 3 =>sel<="11101111";data<=x"b0";when 4 =>sel<="11110111";data<=x"99";when 5 =>sel<="11111011";data<=x"92";when 6 =>sel<="11111101";data<=x"82";when 7 =>sel<="11111110";data<=x"f8";when others=>sel<="11111111";data<=x"ff"; end case;end process;end ;。

第6章基本单元电路的VHDL设计本章提要:本章介绍了数字系统设计中经常用到的计数器,分频器,选择器,译码器,编码器,寄存器,存储器,输入电路,显示电路等基本单元电路的VHDL程序设计。

学习要求:在教师讲授这些基本单元电路的设计思想的基础上,通过上机调试熟练掌握这些基本单元电路的设计。

关键词:计数器(Counter),分频器(Divder),选择器(Multiplexer),译码器(Decoder),编码器(Encoder),寄存器(Register),存储器(Memory),输入电路(Input Circuit),显示电路(Display Circuit)6.1 计数器的设计6.1.1 同步计数器的设计6.1.2 异步计数器的设计6.2 分频器的设计6.3 选择器的设计6.4 译码器的设计6.5 编码器的设计6.5.1 一般编码器的设计6.5.2 优先级编码器的设计6.6 寄存器的设计6.6.1 数码寄存器的设计6.6.2 移位寄存器的设计6.6.3 并行加载移位寄存器的设计6.7 存储器的设计6.7.1 只读存储器ROM的设计6.7.2 读写存储器SRAM的设计6.8 输入电路的设计6.8.1 键盘扫描电路的设计6.8.2 键盘接口电路的设计6.9 显示电路的设计6.9.1 数码管静态显示电路的设计6.9.2 数码管动态显示电路的设计6.9.2 液晶显示控制电路的设计6.1 计数器的设计计数器是在数字系统中使用最多的时序电路,它不仅能用于对时钟脉冲计数,还可以用于分频,定时,产生节拍脉冲和脉冲序列以及进行数字运算等。

计数器是一个典型的时序电路,分析计数器就能更好地了解时序电路的特性。

计数器分同步计数器和异步计数器两种。

6.1.1 同步计数器的设计所谓同步计数器,就是在时钟脉冲(计数脉冲)的控制下,构成计数器的各触发器状态同时发生变化的那一类计数器。

1) 六十进制计数器众所周知,用一个4位二进制计数器可构成1位十进制计数器,而2位十进制计数器连接起来可以构成一个六十进制的计数器。

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

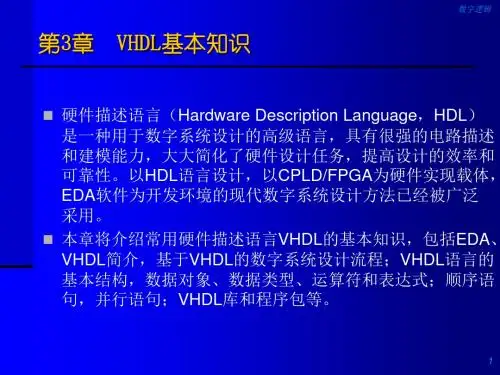

3 VHDL语言VHDL: VHSIC Hardware Description Language.3.1 VHDL语言基础3.2 VHDL基本结构3.3 VHDL语句3.4 状态机在VHDL中的实现3.5 常用电路VHDL程序3.6 VHDL仿真3.7 VHDL综合HDL----Hardware Description Language一种用于描述数字电路的功能或行为的语言。

目的是提为电路设计效率,缩短设计周期,减小设计成本,可在芯片制造前进行有效的仿真和错误检测。

优点:HDL设计的电路能获得非常抽象级的描述。

如基于RTL(Register Transfer Level)描述的IC,可用于不同的工艺。

HDL设计的电路,在设计的前期,就可以完成电路的功能级的验证。

HDL设计的电路类似于计算机编程。

常用的HDL语言:VHDL 、Verilog HDLØVHDL 是美国国防部在20世纪80年代初为实现其高速集成电路硬件VHSIC 计划提出的描述语言;ØIEEE 从1986年开始致力于VHDL 标准化工作,融合了其它ASIC 芯片制造商开发的硬件描述语言的优点,于93年形成了标准版本(IEEE.std_1164)。

Ø1995年,我国国家技术监督局推荐VHDL 做为电子设计自动化硬件描述语言的国家标准。

VHDL 概述:VHDLVHSIC Hardwarter Description Language Very High speed integrated circuit VHSICVHDL优点:Ø覆盖面广,系统硬件描述能力强,是一个多层次的硬件描述语言;ØVHDL语言具有良好的可读性,既可以被计算机接受,也容易被人们所理解;ØVHDL语言可以与工艺无关编程;ØVHDL语言已做为一种IEEE的工业标准,便于使用、交流和推广。

VHDL语言的不足之处:设计的最终实现取决于针对目标器件的编程器,工具的不同会导致综合质量不一样。

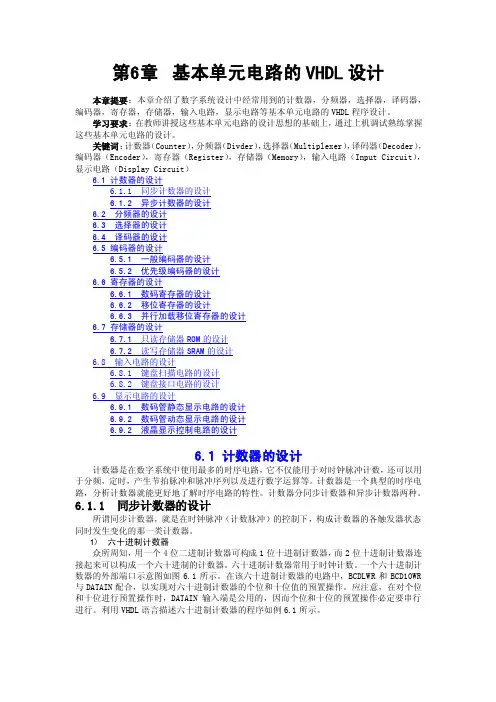

VHDL总复习之必须要掌握的知识点和相关例题目录VHDL总复习之必须要掌握的知识点和相关例题 (1)1. VHDL语言的基本设计实体和完整的VHDL语言程序的结构 (3)2. 进程(PROCESS)语句的结构 (3)3. VHDL语言子程序的结构 (3)(1). 过程(Procedure) (3)(2). 函数(Function) (4)4. 过程与函数的主要区别 (5)5. 进程和子程序中使用的语句 (5)6. VHDL语言中客体的概念及使用范围 (5)7. 信号和变量的区别及作用范围 (5)8. VHDL语言的数据类型和运算操作 (7)9. VHDL语言构造体的三种描述方式 (7)10. COMPONENT(元件)语句和COMPONENT—INSTANT(元件例示)语句的功能和书写格式 (7)11. VHDL语言的主要描述语句的功能、使用场合和语法格式 (8)12. VHDL语言的命名规则 (10)13. VHDL语言的数值类属性描述 (11)14. VHDL语言的信号属性函数 (11)15. 数值系统的定义方法,各种状态的含义 (11)16. 采用有限状态机进行电路设计的基本方法 (12)17. 仿真Δ延时引入的原因和对并发语句仿真结果的影响 (13)18. 逻辑综合的概念与主要步骤 (13)19. 运用VHDL语言和FPGA进行电路设计的主要步骤 (13)VHDL的全称以及利用VHDL设计硬件电路所具有的特点Very High Speed Integrated Circuit Hardware Description Language (超高速集成电路硬件描述语言)(1)设计文件齐全、方法灵活、支持广泛(2)系统硬件描述能力强(3) VHDL语言可以与工艺无关编程(4)VHDL语言标准、规范、易于共享和复用1.VHDL语言的基本设计实体和完整的VHDL语言程序的结构一个VHDL语言的基本设计实体由实体说明和构造体两个部分构成;一个完整的VHDL语言程序包含5个部分:实体、构造体、配置、包集合(程序包)和库。

vhdl基础及经典实例开发pdf VHDL是一种硬件描述语言,它用于描述和设计数字电路。

VHDL的全称是Very High Speed Integrated Circuit Hardware Description Language,它源于20世纪80年代的美国国防部,是一种为了描述硬

件而设计的开发语言。

VHDL的基础知识包括语法、数据类型和结构体。

语法方面,VHDL 有自己的语法规则和词法规则,要正确地描述一个硬件电路,我们需

要熟悉这些规则。

数据类型方面,VHDL内置了基本的数据类型,如bit、bit vector、integer等,这些数据类型可以用来描述电路的输入输出和中间信号。

结构体方面,VHDL支持设计者自定义类型,比如用record来描述一个复杂的数据结构。

在VHDL开发中,经典实例是不可或缺的。

经典实例可以帮助我们更好地理解VHDL的使用方法和特点,也可以让我们更好地掌握VHDL

的编程技巧。

下面是一些经典实例的介绍。

1.二进制加法器(Binary Adder):二进制加法器可以实现两个

二进制数的加法运算。

它是数字电路中常用的基本模块,很多其他的

电路都需要用到它。

通过构建一个二进制加法器的实例,我们可以学习到VHDL的语法规则、数据类型的使用以及模块化设计的思想。

2.时钟分频器(Clock Divider):时钟分频器可以将输入的时钟信号分频为较低频率的信号。

在数字电路中,时钟分频器是非常常见的一个模块,它可以用于控制其他电路的时序。

通过构建一个时钟分频器的实例,我们可以学习到VHDL的状态机设计、时序逻辑的实现以及对时钟信号的处理。

3.多路选择器(Multiplexer):多路选择器可以根据选择信号选择其中的一个输入信号输出。

在数字电路中,多路选择器可以用于实现多个输入的选择和切换。

通过构建一个多路选择器的实例,我们可以学习到VHDL的条件语句的使用、信号赋值的方法以及对多个输入信号的处理。

除了以上这些经典实例,VHDL的应用还非常广泛。

它可以用于设计CPU、FPGA、ASIC等各种数字电路,也可以用于设计计算机芯片、通信芯片等各种集成电路。

在数字系统的设计和开发中,VHDL是一种非常重要的工具和技术。

总结来说,VHDL是一种硬件描述语言,用于描述和设计数字电路。

掌握VHDL的基础知识是学习和使用VHDL的前提,经典实例的开发可

以帮助我们更好地理解VHDL的使用方法和特点。

VHDL在数字系统的设计和开发中有着广泛应用,是一种非常重要的工具和技术。