第3章 VHDL语言基础

- 格式:ppt

- 大小:1.56 MB

- 文档页数:1

第1章VHDL语言基础1.1 概述硬件描述语言(hardware description language,HDL)是电子系统硬件行为描述、结构描述、数据流描述的语言。

目前,利用硬件描述语言可以进行数字电子系统的设计。

随着研究的深入,利用硬件描述语言进行模拟电子系统设计或混合电子系统设计也正在探索中。

国外硬件描述语言种类很多,有的从Pascal发展而来,也有一些从C语言发展而来。

有些HDL成为IEEE标准,但大部分是企业标准。

VHDL来源于美国军方,其他的硬件描述语言则多来源于民间公司。

可谓百家争鸣,百花齐放。

这些不同的语言传播到国内,同样也引起了不同的影响。

在我国比较有影响的有两种硬件描述语言:VHDL语言和Verilog HDL语言。

这两种语言已成为IEEE标准语言。

电子设计自动化(electronic design automation,EDA)技术的理论基础、设计工具、设计器件应是这样的关系:设计师用硬件描述语言HDL描绘出硬件的结构或硬件的行为,再用设计工具将这些描述综合映射成与半导体工艺有关的硬件配置文件,半导体器件FPGA 则是这些硬件配置文件的载体。

当这些FPGA器件加载、配置上不同的文件时,这个器件便具有了相应的功能。

在这一系列的设计、综合、仿真、验证、配置的过程中,现代电子设计理论和现代电子设计方法贯穿于其中。

以HDL语言表达设计意图,以FPGA作为硬件实现载体,以计算机为设计开发工具,以EDA软件为开发环境的现代电子设计方法日趋成熟。

在这里,笔者认为,要振兴我国电子产业,需要各相关专业的人士共同努力。

HDL语言的语法语义学研究与半导体工艺相关联的编译映射关系的研究,深亚微米半导体工艺与EDA设计工具的仿真、验证及方法的研究,这需要半导体专家和操作系统专家共同努力,以便能开发出更加先进的EDA工具软件。

软件、硬件协同开发缩短了电子设计周期,加速了电子产品更新换代的步伐。

毫不夸张地说,EDA工程是电子产业的心脏起搏器,是电子产业飞速发展的原动力。

《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

GDOU-B-11-213《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

第3章VHDL及编程技巧§3.1 VHDL简介3.1.1 关于VHDL随着电子技术的发展,当前数字系缆的设计正朝着速度快,容量大、体积小,重量轻的方向发展。

推动该潮流迅猛发展的引擎就是日趋进步和完善的ASIC设计技术。

目前数字系统的设计可以直接面向用户需求,根据系统的行为和功能要求,自上而下地完成相应的描述、综合、优化、仿真与验证,直到系统生成。

上述设计过程除了系统行为和功能描述以外,其余所有的设计过程几乎都可以用计算机来自动地完成,也就是通常意义上的电子设计自动化(EDA)。

这样做可大大地缩短系统的设计周期,以适应当今品种多、批量小的电子市场的需求,提高产品的竞争能力。

电子设计自动化(EDA)的关键技术之一是要求用形式化方法来描述数字系统的硬件电路,即所谓的硬件描述语言(HDL—Hardware Description Language)。

可以说硬件描述语言及相关的仿真、综合等技术是当今电子设计自动化领域中工程师必备的工具。

硬件描述语言的发展至今已有几十年的历史,并已成功地应用到系统的仿真、验征和设计综合等方面。

上世纪80年代后期,已出现了上百种的硬件描述语言,它们对设计自动化起到了促进和推动作用。

但是它们大多各自针对特定设计领域,无统一的标准。

广大用户所期盼的是一种面向设计的多层次、多领域且得到一致认同的标准的硬件描述语言。

80年代后期由美国国防部开发的VHDL语言恰好满足了上述要求,并在1987年12月由IEEE 标准化(定为IEEEstd 1076--1987标准,1993年进一步修订,被定为ANSI/IEEEstd 1076--1993标准)。

它的出现为电子设计自动化(EDA)的普及和推广奠定了坚实的基础。

据1991年有关统计资料表明,VHDL语言已被广大设计者所接受并用来设计数字系统,尤其是欧洲地区的应用相当广泛。

另外众多的CAD厂商也纷纷使用新开发的电子设计软件与VHDL语言兼容。

第三章VHDL的语句VHDL中的语句按其执行顺序可分为顺序描述语句和并行描述语句两大类。

顺序描述语句的执行顺序是按语句的书写顺序依次执行的,常用于实现模块的算法部分;并行描述语句的执行顺序与书写顺序无关,所有语句是并发执行的,常用于表示模块间的连接关系。

本章将详细介绍这两类VHDL语句。

3.1 VHDL语言的顺序描述语句顺序语句是建模进程、过程和函数功能的基本语句单元,它只能在进程、过程和函数中使用,其执行顺序按照书写顺序来执行,同时前面语句的执行结果会对后面语句的执行结果产生影响。

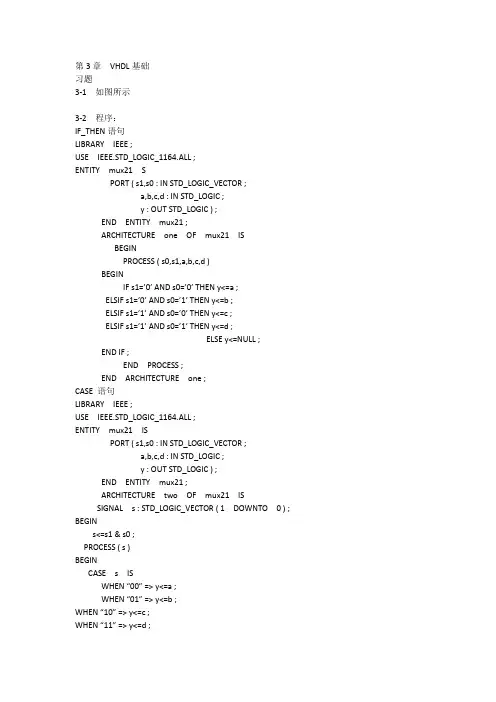

顺序描述语句按照控制方式分为条件控制语句和迭代控制语句,其中,条件控制语句有IF语句和CASE语句,迭代控制语句有循环语句和顺序断言语句。

下面对顺序描述语句进行详细介绍。

3.1.1 信号赋值语句与变量赋值语句采用VHDL描述硬件电路的过程中,数据的传递和端口界面数据的读写都是通过赋值语句来实现的,赋值语句就是将一个数值或表达式传递给某一个数据对象的语句。

VHDL 提供了两类赋值语句:信号赋值语句和变量赋值语句。

信号虽然只能在VHDL程序的并行部分进行说明,但是它在程序的顺序部分和并行部分都可使用。

信号赋值语句的语法如下:待赋值信号<=表达式;变量的说明和赋值操作都只能在程序的顺序部分进行。

变量赋值语句的语法如下:待赋值变量:=表达式;注意:不论是信号还是变量,赋值符号两边必须具备相同的数据类型和位长。

在前一章我们讲过信号与变量的区别,这里有必要重申一下:信号赋值的执行和信号值的更新之间是有一定延迟的,只有经过延迟后信号才能得到新值,否则保持原值;而变量赋值的语句执行后立即得到新值,没有延迟。

上面讲到,信号赋值会有延迟,其实,VHDL允许为信号赋值选择“延迟机制”,即:传输延迟或惯性延迟,其中,传输延迟用于表示无论输入脉冲宽度多窄都能在输出端无失真复现的延迟模型;惯性延迟用于表示输入脉冲传播时间受电路“惯性”影响的延迟模型。