Cadence 原理图库设计

- 格式:doc

- 大小:14.80 MB

- 文档页数:9

Cadence原理图库的制作及使用(二)在上一节中,我们讲述了一种原理图库的制作方法:使用封装编辑器创建封装,然后生成符号。

在本节内容当中,我们将要讲述另外一种制作方法:先创建符号,然后由符号得到封装。

本节将要讲述另外一种方法:从符号得出封装。

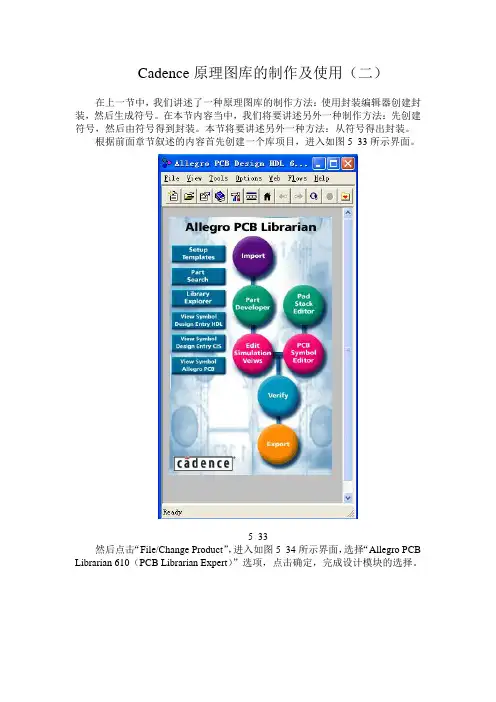

根据前面章节叙述的内容首先创建一个库项目,进入如图5_33所示界面。

5_33然后点击“File/Change Product”,进入如图5_34所示界面,选择“Allegro PCB Librarian 610(PCB Librarian Expert)”选项,点击确定,完成设计模块的选择。

5_34单击图5_33中“Part Developer”,进入库设计软件界面,如图5_35所示。

5_35选择File菜单中的New/Cell选项,出现如图5_36所示对话框。

5_36有些元件有多个相同的功能组,需要创建单个功能组的符号和整个元件的符号以方便原理图设计,满足设计的不同需求。

创建符号的方法如下:1、输入sizeable管脚并通过符号编辑器创建符号;2、创建封装;3、创建必要的通道;4、通过拷贝sym_1来创建sym_2;5、确定sym_2的SIZE属性并添加HAS_FIXED_SIZE 属性。

在“Cell”对应的空白栏处输入元件库的名称,自己可以随意写,但是最好用和芯片信息相关的名字,比如可以用元件型号命名,例如要制作74HC04的原理图元件库,在空白栏处输入74HC04,单击确定,出现如图5_37所示界面。

5_37选择左边项目栏中的symbols选项,右键点击弹出如图5_38所示界面。

5_38选择弹出菜单中的“New”选项,左键点击之后界面如图5_39所示。

5_39在右边界面当中选择“symbol pins”选项卡,界面如图5_40所示。

5_40左键点击“Pins”选项卡,弹出如图5_41 所示菜单。

选择“Add”选项,打开如图5_42所示界面。

5_415_42在该例子中,我们选择【Sizeable】单选框,74HC04芯片有一个输入管脚A,一个输出管脚Y,共有六个slots。

原理图库设计一,工具及库文件目录结构目前公司EDA库是基于Cadence设计平台,Cadence提供Part Developer库开发工具供大家建原理图库使用。

Cadence 的元件库必具备如下文件目录结构为:Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table)Sym_1:存放元件符号Entity:存放元件端口的高层语言描述Chips:存放元件的物理封装说明和属性Part-table:存放元件的附加属性,用于构造企业特定部件我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。

二,原理图库建库参考标准1,Q/ZX 04.104.1电路原理图设计规范-Cadence元器件原理图库建库要求该标准规定了元件库的分类基本要求和划分规则,元器件原理图符号单元命名基本要求和规则,元器件原理图符号单元图形绘制基本要求和规则。

2, Q/ZX 04.125 EDA模块设计规范此标准规定了全公司基于Cadence设计平台的EDA模块库的设计标准。

3, Q/ZX 73.1151 EDA 库管理办法此标准规定了公司统一的基于Cadence设计平台的元器件原理图库,封装库,仿真库和相应PCBA DFM评审辅助软件VALOR的VPL库及相应的元器件资料的管理办法。

从此标准中我们可以知道VPL建库流程,建库过程的各项职责以及VPL库的验证,维护等管理办法。

4, Q/ZX 73.1161 EDA模块库管理办法此标准规定了全公司基于Cadence设计平台的EDA模块库的管理办法。

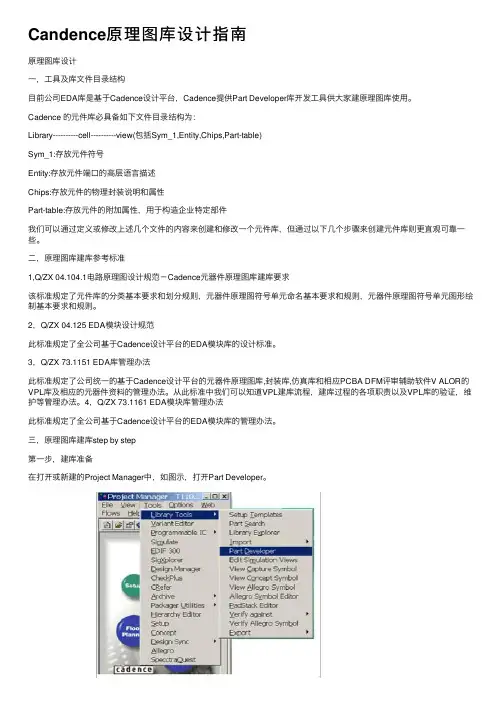

三,原理图库建库step by step第一步,建库准备在打开或新建的Project Manager中,如图示,打开Part Developer。

第二章 Cadence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL 是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计,Design Entry CIS原本是OrCAD公司的产品,OrCAD公司后来被Cadence公司收购,于是Design Entry CIS也就成了Cadence公司的另一套电路原理图设计软件。

Design Entry CIS原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用Design Entry CIS原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的STC系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到USB转UART串行口、STC系列单片机下载电路等方面的知识。

接着,我们将围绕一块ARM-7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于ARM-7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB 16.2→Design Entry CIS”,如下图所示:图2-1 启动Design Entry CIS这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了Design Entry CIS,出现如下界面:图2-3 OrCAD Capture CIS软件界面与大多数软件一样,OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的。

Candence原理图库设计指南原理图库设计⼀,⼯具及库⽂件⽬录结构⽬前公司EDA库是基于Cadence设计平台,Cadence提供Part Developer库开发⼯具供⼤家建原理图库使⽤。

Cadence 的元件库必具备如下⽂件⽬录结构为:Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table)Sym_1:存放元件符号Entity:存放元件端⼝的⾼层语⾔描述Chips:存放元件的物理封装说明和属性Part-table:存放元件的附加属性,⽤于构造企业特定部件我们可以通过定义或修改上述⼏个⽂件的内容来创建和修改⼀个元件库,但通过以下⼏个步骤来创建元件库则更直观可靠⼀些。

⼆,原理图库建库参考标准1,Q/ZX 04.104.1电路原理图设计规范-Cadence元器件原理图库建库要求该标准规定了元件库的分类基本要求和划分规则,元器件原理图符号单元命名基本要求和规则,元器件原理图符号单元图形绘制基本要求和规则。

2,Q/ZX 04.125 EDA模块设计规范此标准规定了全公司基于Cadence设计平台的EDA模块库的设计标准。

3,Q/ZX 73.1151 EDA库管理办法此标准规定了公司统⼀的基于Cadence设计平台的元器件原理图库,封装库,仿真库和相应PCBA DFM评审辅助软件V ALOR的VPL库及相应的元器件资料的管理办法。

从此标准中我们可以知道VPL建库流程,建库过程的各项职责以及VPL库的验证,维护等管理办法。

4,Q/ZX 73.1161 EDA模块库管理办法此标准规定了全公司基于Cadence设计平台的EDA模块库的管理办法。

三,原理图库建库step by step第⼀步,建库准备在打开或新建的Project Manager中,如图⽰,打开Part Developer。

然后出现如下画⾯,点击new cell开始建库注意建库过程中的各项运⾏提⽰出现在此处点击Create New,下图新菜单中提⽰⼤家选择库⽬录,新建库元件名称。

Cadence原理图库设计一.工具及库文件目录结构Cadence提供Part Developer库开发工具供大家建原理图库使用。

Cadence 的元件库必具备如下文件目录结构为:Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table)Sym_1:存放元件符号Entity:存放元件端口的高层语言描述Chips:存放元件的物理封装说明和属性Part-table:存放元件的附加属性,用于构造企业特定部件我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。

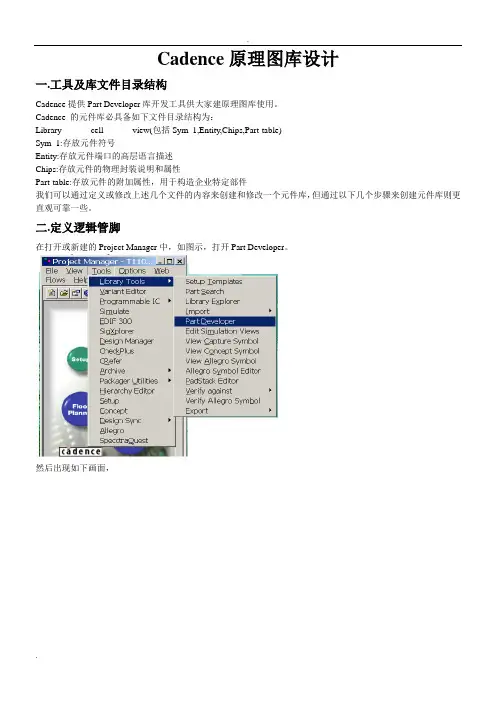

二.定义逻辑管脚在打开或新建的Project Manager中,如图示,打开Part Developer。

然后出现如下画面,点击Create New,下图新菜单中提示大家选择库路径,新建库元件名称及器件类型。

点击ok后,Part Developer首先让大家输入元件的逻辑管脚。

一个原理图符号可以有标量管脚和矢量管脚。

标量管脚在符号中有确定位置,便于检查信号与管脚的对应,但矢量管脚却可使原理图更简洁,适用于多位总线管脚。

点击上图中的Edit,编辑器会让我们对首或尾带有数字的字符串的多种输入方式(A1; 1A; 1A1)进行选择,一但选定,编辑器即可对同时具有数字和字母的管脚输入进行矢量或标量界定。

管脚名首尾均不带数字的字符串如A; A1A则自动被识别为标量管脚。

按照元件手册决定管脚名称及逻辑方向,选择是否为低电平有效,点击ADD即可加入新的管脚。

(注:不论是标量或矢量管脚,均可采用集体输入,如在Pin Names栏可输入A1-A8, 1C-16C)三.加入封装相关信息点击Packages,按右键,选择New,出现如下画面。

在Gerneral的各项填入相关信息,选择Specify Package Type可指定封装类型,在Reference Designator中填入或选择位号标识,JEDEC_TYPE和ALT_SYMBOLS分别可填入对应的PCB封装类型及替代封装。

第五掌Cadence原理图元件库的制作及使用5.1原理图库项目的创建库项目的创建,与第四章中lib的建立过程一样,可参考前面章节。

5.2原理图库管理工具在Cadence的原理图库创建和管理过程中,要用到如下工具:1. Library Explorer:用于原理图库的管理2. Part Developer:编辑库文件3. Part Table Editor:创建和修改元件列表文件5.3 原理图库的制作根据第四章相关内容,创建一个名称为lib的库文件,创建完成之后如图5_1所示。

5_1然后点击“File/Change Product”选项,出现图5_2所示的对话框。

5_2选择“Allegro PCB Librarian 610(PCB Librarian Expert)”选项,点击确定,完成设计模块的选择。

单击图5_1中“Part Developer”,进入库设计软件界面,如图5_3所示。

5_3选择File菜单中的New/Cell选项,出现如图5_4所示对话框。

5_4在“Cell”对应的空白栏处输入元件库的名称,自己可以随意写,但是最好用和芯片信息相关的名字,比如可以用元件型号命名,例如要制作XCV300EFG256的原理图元件库,在空白栏处输入XCV300EFG256,单击确定,出现如图5_5所示界面。

5_5选中项目栏中的“Packages”选项,单击鼠标右键,选择弹出菜单中“New”选项,点击出现如图5_6所示界面。

5_6选中图5_6中“General”选项卡,在这个界面当中可以设计元件的类和位号的前缀。

此处选择IC(芯片),位号前缀可以选择U,用户也可以根据自己的习惯自行输入。

选中5_6中“Package Pin”选项卡,鼠标左键单击“Pins”出现如图5_7所示界面。

5_7单击弹出菜单中的“Add”选项,出现如图5_8所示界面。

5_8用户需要知道整个元件的信息(可以在网上进行搜索),然后将元件的信息添加进去。

cadence原理图设计报告

工具:Design Entry CIS

设计目标:绘制原理图库与原理图,最终产生网表文件(PCB设计使用)。

1.1新建原理图工程

原理图工程以.opj结尾,原理图以.DSN后缀结束;原理图库以.OLB后缀1.2新建多个原理图部分

右击可以设置成根原理图部分。

1.3设置原理图纸张大小

1.4tools 下可以设置工具窗口显示与隐藏

1.5options-P可以设置背景颜色等,设置点状与线状背景。

1.6options-D可以设置原理图纸的大小等

2制作库文件

2.1新建library

file-->new-->library(点击保存,设置库名称)

2.2创建元件右键new--》part

2.3设置器件属性:名称,填写封装,类型等

2.4设置好管教后添加边框

2.5放置器件

(可以添加不同路径的库文件进来)

2.6view--》page

设置管教属性状态

2.7添加库文件,复制元器件进入自己库

2.8

支持不同原理图间元器件的拷贝、

原理图中的原价有错误可以直接编辑库文件,然后更新原理图中对应的器件

器件的名称不允许重复可以讲引脚属性设置成pow属性

2.9同page放置网络标号

2.10不是同一页的网络标号放置offpage

2.11填写封装

2.12更新缓存

2.13DRC检查

2.14输出网表文件

(1)第一方网表文件,用于PCB设计。

出现错误时需要修改至没错才会产生。

(2)第三方网表文件

2.15导出BOM表单

(注意添加封装信息)。

原理图库设计一,工具及库文件目录结构目前公司EDA库是基于Cadence设计平台,Cadence提供Part Developer库开发工具供大家建原理图库使用。

Cadence 的元件库必具备如下文件目录结构为:Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table)Sym_1:存放元件符号Entity:存放元件端口的高层语言描述Chips:存放元件的物理封装说明和属性Part-table:存放元件的附加属性,用于构造企业特定部件我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。

二,原理图库建库参考标准1,Q/ZX 04.104.1电路原理图设计规范-Cadence元器件原理图库建库要求该标准规定了元件库的分类基本要求和划分规则,元器件原理图符号单元命名基本要求和规则,元器件原理图符号单元图形绘制基本要求和规则。

2,Q/ZX 04.125 EDA模块设计规范此标准规定了全公司基于Cadence设计平台的EDA模块库的设计标准。

3,Q/ZX 73.1151 EDA库管理办法此标准规定了公司统一的基于Cadence设计平台的元器件原理图库,封装库,仿真库和相应PCBA DFM评审辅助软件V ALOR的VPL库及相应的元器件资料的管理办法。

从此标准中我们可以知道VPL建库流程,建库过程的各项职责以及VPL库的验证,维护等管理办法。

4,Q/ZX 73.1161 EDA模块库管理办法此标准规定了全公司基于Cadence设计平台的EDA模块库的管理办法。

三,原理图库建库step by step第一步,建库准备在打开或新建的Project Manager中,如图示,打开Part Developer。

然后出现如下画面,点击new cell开始建库注意建库过程中的各项运行提示出现在此处点击Create New,下图新菜单中提示大家选择库目录,新建库元件名称。

第二章 Cadence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL 是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计,Design Entry CIS原本是OrCAD公司的产品,OrCAD公司后来被Cadence公司收购,于是Design Entry CIS也就成了Cadence公司的另一套电路原理图设计软件。

Design Entry CIS原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用Design Entry CIS原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的STC系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到USB转UART串行口、STC系列单片机下载电路等方面的知识。

接着,我们将围绕一块ARM-7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于ARM-7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB 16.2→Design Entry CIS”,如下图所示:图2-1 启动Design Entry CIS这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了Design Entry CIS,出现如下界面:图2-3 OrCAD Capture CIS软件界面与大多数软件一样,OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的。

第二章的原理图设计2.1软件概述软件系统有两套电路原理图的设计工具,一套是,另一套就是我们马上要开始学习的。

其中是公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而主要用于常规的板级电路设计,原本是公司的产品,公司后来被公司收购,于是也就成了公司的另一套电路原理图设计软件。

原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到转串行口、系列单片机下载电路等方面的知识。

接着,我们将围绕一块7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识一.启动我们在电脑上点击“开始→所有程序→ 16.2→”,如下图所示:这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“”一项,点击“”按钮后,就实际启动了,出现如下界面:图2-3 软件界面与大多数软件一样,软件也是以项目方式管理我们的设计文件的。

在软件中,一个项目可以包含若干个设计,每个设计对应一个板,所以一个项目通常对应一个由多块电路板构成的产品;而每个设计可以由若干张原理图构成。

对于我们要完成的“系列单片机下载器”而言,它是非常简单的产品,该产品只包含一块电路板,所以该项目中只有一个设计;又因为该电路板上的电路也非常简单,使用一张图纸就可以清楚地描述了,所以该设计只有一张原理图。

我们将首先要新建一个项目:在窗体上点击“→→”出现如下对话框:图2-4 新建项目在“”中输入项目名称,“”中输入项目文件的存放位置(最好给每一个项目建立一个文件夹,把项目中的所有文件都放入该文件夹),在“ a ”栏目中,选择“”(因为我们要进行电路原理图的设计)。

Cadence原理图库设计

一.工具及库文件目录结构

Cadence提供Part Developer库开发工具供大家建原理图库使用。

Cadence 的元件库必具备如下文件目录结构为:

Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table)

Sym_1:存放元件符号

Entity:存放元件端口的高层语言描述

Chips:存放元件的物理封装说明和属性

Part-table:存放元件的附加属性,用于构造企业特定部件

我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。

二.定义逻辑管脚

在打开或新建的Project Manager中,如图示,打开Part Developer。

然后出现如下画面,

点击Create New,下图新菜单中提示大家选择库路径,新建库元件名称及器件类型。

点击ok后,Part Developer首先让大家输入元件的逻辑管脚。

一个原理图符号可以有标量管脚和矢量管脚。

标量管脚在符号中有确定位置,便于检查信号与管脚的对应,但矢量管脚却可使原理图更简洁,适用于多位

总线管脚。

点击上图中的Edit,编辑器会让我们对首或尾带有数字的字符串的多种输入方式(A1; 1A; 1A1)进行选择,一但选定,编辑器即可对同时具有数字和字母的管脚输入进行矢量或标量界定。

管脚名首尾均不带数字的字符串如A; A1A则自动被识别为标量管脚。

按照元件手册决定管脚名称及逻辑方向,选择是否为低电平有效,点击ADD即可加入新的管脚。

(注:不论是标量或矢量管脚,均可采用集体输入,如在Pin Names栏可输入A1-A8, 1C-16C)

三.加入封装相关信息

点击Packages,按右键,选择New,出现如下画面。

在Gerneral的各项填入相关信息,选择Specify Package Type可指定封装类型,在Reference Designator中填入

或选择位号标识,JEDEC_TYPE和ALT_SYMBOLS分别可填入对应的PCB封装类型及替代封装。

Physical Pin Mapping对话框涉及PCB封装与原理图库符号的管脚对应问题:

1, 如果在General中没指定JEDEC_TYPE,可通过Add Manually方式加入封装管脚,选择Add Manually,点击Pin Numbers,出现Add Physical Pin Numbers对话框,选择Nuneric,输入需要加的管脚或集体输入比如1-20,即可把1到20的管脚均罗列到Physical Pins栏内。

如果在General中指定了JEDEC_TYPE,管脚可以直接从封装中提取。

在Logical栏选择逻辑管脚,在Physical Pins栏内选择相应封装管脚,点击Map,即可实现从原理图符号到PCB

封装的管脚映射,如下图。

对于多行列封装,可能存在A1-A10,B1-B10,C1-C10这样的管脚,我们在加入Physical Pins之前,应在Add Physical Pin Numbers对话框中选择Grid阵列输入,如下图。

2, 如果在General中指定了JEDEC_TYPE,在Physical Pin Mapping对话框中允许我们通过封装库中已有封装的既定管脚来实现管脚映射。

在Physical Pin Mapping对话框中选择Extract From Footprint,点击Pin Numbers后即可把已有封装的管脚罗列到Physical Pins栏内。

余下的映射操作同上。

学会使用这个对两者之间的对应关系有好处。

四.创建元件符号图

在Part Developer编辑器主界面选择Symbols按右键选择New,将出现如下界面提示我们选择建立一个单部件元件还是多部件元件,多部件元件允许我们把元件符号拆成几个部份分别表示物理封装的一部份,在元件管脚非常多时比较适用。

多部件元件与单部件元件的创建方法类似,我们就以单部件元件为例。

选择All Pin,然后点击Next,则出现如下画面。

上图中第一项Logical表示只把逻辑管脚体现在符号中,隐含电源和地;第二项Logic+Power+Ground

表示把三者都体现在符号中,第三项Logic,Power+Ground表示把三者分别用两个符号来表示,少用。

如果选择第一项则一定要通过POWER_GROUP属性来定义电源和地。

点击Next,则出现如下画面。

此表提示我们可以更改或新建封装类型,如不想更改和新建,则点击Modify Existing Package后不更改内容。

点击Next,出现如下画面,点击Finish,完成符号的初步编辑。

如果选择了电源和地的隐含方式,需要在Symbols的属性栏的Additional Properties内加Power_Group属性如下图示,注意对齐方式及可见性的选择。

选择Symbol Properties的Symbol Pins对话框,还可对符号中逻辑管脚的位置和次序进行编辑。

如下图。

对Symbols Properties编辑完成后,可点击主菜单的sym_1按右键进入Concept-HDL,在Concept-HDL中可适当调整管脚及文字的位置。

在Concept-HDL中编辑符号图形时,系统自动将栅格设置为0.05 2, 意思是跟踪栅格50mil,显示栅格100mil, 最好别更改这个默认值,否则在原理图设计时,会遇到麻烦。

五.创建Part-table文件

Part-table文件用于灵活构造部件以满足用户不同需要。

例如我们可以在Part-table文件中重定义JEDEC_TYPE 和ALT_SYMBOLS替代曾经加入过的封装信息。

在Part Developer主界面点击Part Table Files,右键选择New后进入Ptf Editor,如下图。

在Header对话框内分别可定义Key属性,Injected属性,Global属性。

在Part Rows对话框内中定义部件的属性值。

Part-table文件是一个ASCII文件,任何文本编辑器均可编写或修改该文件,注意文件内容必须符合图例格式。

Example:

FILE_TYPE = MULTI_PHYS_TABLE;

PART 'AD704'

CLASS=IC

{========================================================================================}

:VENDOR_PART_NUMBER(OPT) = PART_NUMBER | JEDEC_TYPE | DESCRIPTION ;

{========================================================================================}

'AD704AR'(!) = '12100068' | 'SO16-300' | 'Vcc(max)+18V,CMRR>94.0dB,SR>0.15V/us'

'AD704AN'(!) = '12100069' | 'SO16-150' | 'Vcc(max)+18V,CMRR>94.0dB,SR>0.15V/us'

END_PART

END.

在制作Part-table文件时,最好是引用其他人的Part-table文件来修改以节省设计时间。

六.验证原理图符号库

完成符号库设计后,在Part Developer 界面选择Tools->Verify,对元件库进行检查,如果没有报错,则此元件库创建基本成功了,为了验证此元件库是否可用,我们可以新创建一个Project,打开Concept-HDL,在原理图页中调入新做的零件打包看是否能成功把元件符号转成PCB封装。