cadence原理图设计规范

- 格式:doc

- 大小:42.00 KB

- 文档页数:4

第二章 Cadence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL 是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计,Design Entry CIS原本是OrCAD公司的产品,OrCAD公司后来被Cadence公司收购,于是Design Entry CIS也就成了Cadence公司的另一套电路原理图设计软件。

Design Entry CIS原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用Design Entry CIS原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的STC系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到USB转UART串行口、STC系列单片机下载电路等方面的知识。

接着,我们将围绕一块ARM-7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于ARM-7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB 16.2→Design Entry CIS”,如下图所示:图2-1 启动Design Entry CIS这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了Design Entry CIS,出现如下界面:图2-3 OrCAD Capture CIS软件界面与大多数软件一样,OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的。

原理图设计规范文档修改情况版本状态修订内容实施日期编制审核1.0起草2011-4-151 概述本文档的目的在于说明当使用ORCAD完成原理图设计,使用Candence公司的Allegro完成PCB布线设计时,在使用ORCAD设计原理图时的流程和一些注意事项,为一个工作组的设计人员提供设计规范,方便设计人员之间进行交流和相互检查,便于Allegro的网表导入。

2 设计流程原理图的设计流程分为:器件选择,原理封装设计,原理图设计,原理图检查,PCB封装指定,输出网表,原理图整理,提交设计。

2.1 器件选择依据几个原则选定器件:功能适合原则:既保证冗余性,又不会造成大的浪费,例如电源芯片和FPGA芯片。

软件开发的方便性:对于同一功能的器件,应该考虑技术支持和驱动程序设计。

通用性原则:可替换种类越多越好,避免停产等。

布线的方便性:例如封装的选择决定着器件面积和管脚的间距。

生产的方便性:BGA封装的器件避免选择管脚的间距特别小的封装器件(例如S3C6410的BGA封装FBGA424,管脚间距为0.5mm),目前国内的生产工艺以及焊接水平与国外还有一定的差距。

目前国内的BGA 加工对于管脚间距为0.8mm的BGA封装器件的加工工艺已经很成熟。

可方便采购原则:向采购部门要求提供购货渠道,价格和订货周期。

接插件选择:尽量选择接口可靠和方便安装的接口。

2.2 原理封装设计封装设计时,最好把管脚归类放置,电源放在顶部,地放置在底部,输入放在左边,输出放置在右边。

管脚类型应该指定,对于双向脚最好指定为PASSIVE.设计原理封装的工程师应该设计相应的PCB封装。

原理封装应该保持器件尺寸的合理性,便于原理图设计。

对于低有效的管脚命名应该使用\ 例如 R\S\T\表现为RST1。

对于总线管脚,直接命名为 PCI_AD0,PCI_AD1,….对于重名管脚,加1,2,3,…;例如 VCC1,VCC2。

不使用隐藏管脚功能。

2.3 原理图设计2.3.1 原理图分页设计原则:在确定方案后,首先划分功能模块,相同模块尽量放置在同一页,页大小一般采用C型页面大小。

在电子设计自动化(EDA)领域,Cadence是一家提供EDA工具的知名公司。

在Cadence的工具中,设计规则(Design Rules)是设计流程中的关键部分。

这些规则定义了电路板或芯片的物理和电气特性,确保设计在制造和操作过程中能够正常工作。

在本文中,我们将深入探讨Cadence设计规则的重要性、不同类型的规则以及它们在EDA工具中的应用。

### **1. Cadence设计规则的重要性:**设计规则在EDA工具中的重要性不可忽视,它们有助于确保设计的可靠性、性能和可制造性。

以下是一些设计规则的重要方面:#### **可靠性和性能:**设计规则确保电路在操作中的可靠性和性能。

通过定义电路中各个元件的准确位置、尺寸和连接方式,规则确保电路在预期工作条件下能够稳定运行。

#### **制造可行性:**设计规则在制造过程中起到了至关重要的作用。

它们确保设计是可制造的,可以满足制造工艺的要求。

例如,规定最小特征尺寸、间距和层间连接的规则有助于确保制造过程的成功。

#### **减少错误和返工:**遵循设计规则有助于减少设计中的错误和需要返工的可能性。

通过在设计阶段检测和解决问题,可以提高整个设计流程的效率,并减少后续阶段的成本。

#### **提高设计团队协作:**规则的使用也有助于提高设计团队之间的协作。

它们提供了设计的标准,确保每个设计者都遵循相同的规范,从而简化了设计审核和交接的过程。

### **2. Cadence设计规则的分类:**在Cadence工具中,设计规则可以分为多个类别,每个类别都关注电路设计的不同方面。

以下是一些常见的设计规则类别:#### **物理设计规则:**- **DRC(Design Rule Check)规则:** DRC规则关注电路的物理布局,确保元件之间的间距、连接等满足工艺和制造的要求。

- **LVS(Layout vs. Schematic)规则:** LVS规则用于验证布局与原理图之间的一致性,确保设计与预期的电气特性相匹配。

原理图设计规范原理图设计基本要求日期修订版本修改描述作者目录一、图纸规则 (4)二、文件命名及作图规范: (4)1.文件命名方法,其格式如下:项目名_版本 (4)三、器件位号及序号规范: (8)1.电容的表示方法: (9)2.电阻的表示方法: (9)3.电感的表示方法 (10)5.变压器表示方法 (10)6. 连接器的规格描述 (10)7. 跳线的规格描述 (10)8.发光二极管的表示方法 (11)9.二极管的表示方法 (11)10.三极管的表示方法 (11)11.场效应管的规格描述 (11)12.普通IC类的表示方法 (11)13.光藕规格描述 (12)14.开关器件的表示方法 (12)15.继电器的表示方法 (12)16.晶振及钟振的表示方法 (12)17.保险丝的表示方法 (12)18.防雷器件及其他保护器件表示方法 (12)19. TVS管的规格描述 (13)20.滤波器规格描述 (13)21.光组件规格描述 (13)22.螺丝(SCREW)孔规格描述 (13)23. PCB印制天线(Antenna)的规格描述 (13)24.光学定位点 (13)25.可选器件描述的表示方法 (13)四、电路参数标注规范: (14)五、布局规则及标识 (14)六、线的规则 (19)七、网络标号 (20)八、地及电源网络定义规则: (21)一、 图纸规则1.图纸使用英制单位,使用默认纸张(A,B,C,D,E),禁止使用自定义纸张;2.原理图格点的风格采用dots,器件格点风格采用lines;格点的大小采用默认设置1:3.SCH中所用标示及注明,全部使用英文。

4.对于复杂电路,要求将原理图幅面划分区域,定义各模块中的子模块,并表注各子模块的功能;二、 文件命名及作图规范:1.文件命名方法,其格式如下:项目名_版本1.1项目名称为该型号的名称,如:GRUFNV5B.7U731.2版本号:V0.11.3分页名称以Pxx_XXXX…P: Page的第一个英文字母,表示页码;xx:表示第几页,从第1页到第9页的范围内,用01到09表示,第10页以上(包括第10页),用数字表示,如11;XXXX:页面的英文名称,第一页到第三页的名称固定,分别为:Cover Page、Block Diagram、Machine Diagram;1.4原理图和第一页到第三页必须按照1.5~1.7中插图的格式进行制作,相关模板可从以下地址下载:PLM\系统\文档管理\文档库-工作区\文档库\layout相关文件夹\原理图作图模板。

原理图库设计一,工具及库文件目录结构目前公司EDA库是基于Cadence设计平台,Cadence提供Part Developer库开发工具供大家建原理图库使用。

Cadence 的元件库必具备如下文件目录结构为:Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table)Sym_1:存放元件符号Entity:存放元件端口的高层语言描述Chips:存放元件的物理封装说明和属性Part-table:存放元件的附加属性,用于构造企业特定部件我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。

二,原理图库建库参考标准1,Q/ZX 04.104.1电路原理图设计规范-Cadence元器件原理图库建库要求该标准规定了元件库的分类基本要求和划分规则,元器件原理图符号单元命名基本要求和规则,元器件原理图符号单元图形绘制基本要求和规则。

2, Q/ZX 04.125 EDA模块设计规范此标准规定了全公司基于Cadence设计平台的EDA模块库的设计标准。

3, Q/ZX 73.1151 EDA库管理办法此标准规定了公司统一的基于Cadence设计平台的元器件原理图库,封装库,仿真库和相应PCBA DFM评审辅助软件VALOR的VPL库及相应的元器件资料的管理办法。

从此标准中我们可以知道VPL建库流程,建库过程的各项职责以及VPL库的验证,维护等管理办法。

4, Q/ZX 73.1161 EDA模块库管理办法此标准规定了全公司基于Cadence设计平台的EDA模块库的管理办法。

三,原理图库建库step by step第一步,建库准备在打开或新建的Project Manager中,如图示,打开Part Developer。

然后出现如下画面,点击Create New,下图新菜单中提示大家选择库目录,新建库元件名称。

原理图设计规范理念: 设计好一份规范的原理图对设计好PCB/跟机/做客户资料具有指导性意义,是做好一款产品的基础。

一、标准图框图幅根据实际需要,我公司常用图幅为A2、A3、A4,并有标准格式的图框。

其中每一图幅可根据方向分为Landscape(纵向)及Portrait(横向)。

在选用图纸时,应能准确清晰的表达区域电路的完整功能。

二、电路布局原理图的作用是表示电路连接关系,因此需要注意电路结构的易读性。

一般可将电路按照功能划分成几个部分,并按照信号流程将各部分合理布局。

连线时,需注意避免线条的不必要交叉,以免难于辨识。

具体要求如下:1. 各功能块布局要合理, 整份原理图需布局均衡. 避免有些地方很挤,而有些地方又很松, PCB 设计同等道理.2. 尽量将各功能部分模块化(如功放,RADIO, E.VOL, SUB-WOOFER 等),以便于同类机型资源共享, 各功能模块界线需清晰.3. 接插口(如电源/喇叭插座, AUX IN, RCA OUTPUT, KB/CD SERVO 接口等)尽量分布在图纸的四周围, 示意出实际接口外形及每一接脚的功能.4. 可调元件(如电位器), 切换开关等对应的功能需标识清楚.5. 滤波器件(如高/低频滤波电容,电感)需置于作用部位的就近处.6. 重要的控制或信号线需标明流向及用文字标明功能.7. CPU 为整机的控制中心, 接口线最多. 故CPU周边需留多一些空间进行布线及相关标注,而不致于显得过分拥挤.8. CPU 的设置管脚(如AREA1/AREA2, CLOCK1/CLOCK2等)需于旁边做一表格进行对应设置的说明.9. 重要器件(如接插座,IC, TUNER 等)外框用粗体线(统一 0.5mm).10. 元件标号照公司要求按功能块进行标识.11. 元件参数/数值务求准确标识. 特别留意功率电阻一定需标明功率值, 高耐压的滤波电容需标明耐压值.12. 每张原理图都需有公司的标准图框,并标明对应图纸的功能,文件名,制图人名/审核人名, 日期, 版本号.13. 计初始阶段工程师完成原理图设计并自我审查合格后, 需提交给项目主管进行再审核, 直到合格后才能开始进行PCB 设计.三、元件标注1.元件标注最基本信息,即显示在图上的信息应该包括元器件位号和元器件值。

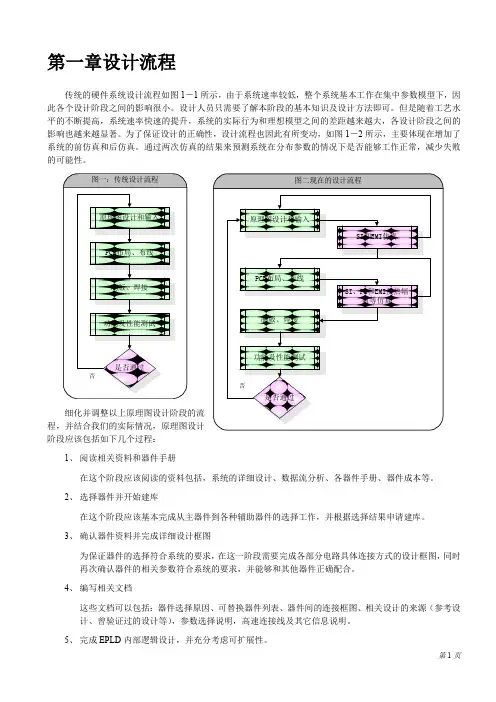

第一章设计流程传统的硬件系统设计流程如图1-1所示,由于系统速率较低,整个系统基本工作在集中参数模型下,因此各个设计阶段之间的影响很小。

设计人员只需要了解本阶段的基本知识及设计方法即可。

但是随着工艺水平的不断提高,系统速率快速的提升,系统的实际行为和理想模型之间的差距越来越大,各设计阶段之间的影响也越来越显著。

为了保证设计的正确性,设计流程也因此有所变动,如图1-2所示,主要体现在增加了系统的前仿真和后仿真。

通过两次仿真的结果来预测系统在分布参数的情况下是否能够工作正常,减少失败的可能性。

细化并调整以上原理图设计阶段的流程,并结合我们的实际情况,原理图设计阶段应该包括如下几个过程:1、 阅读相关资料和器件手册在这个阶段应该阅读的资料包括,系统的详细设计、数据流分析、各器件手册、器件成本等。

2、 选择器件并开始建库在这个阶段应该基本完成从主器件到各种辅助器件的选择工作,并根据选择结果申请建库。

3、 确认器件资料并完成详细设计框图为保证器件的选择符合系统的要求,在这一阶段需要完成各部分电路具体连接方式的设计框图,同时再次确认器件的相关参数符合系统的要求,并能够和其他器件正确配合。

4、 编写相关文档这些文档可以包括:器件选择原因、可替换器件列表、器件间的连接框图、相关设计的来源(参考设计、曾验证过的设计等),参数选择说明,高速连接线及其它信息说明。

5、 完成EPLD 内部逻辑设计,并充分考虑可扩展性。

在编写相关文档的的同时需要完成EPLD内部逻辑的设计,确定器件容量及连接方式可行。

6、使用Concept-HDL绘制原理图7、检查原理图及相关文档确保其一致性。

以上流程中并未包括前仿真的相关内容,在设计中可以根据实际情况,有选择的对部分重要连线作相关仿真,也可以根据I/O的阻抗,上升下降沿变化规律等信息简单分析判断。

此流程中的各部分具体要求、注意事项、相关经验和技巧有待进一步完善。

第二章Concept-HDL的使用运行Concept-HDL后将会出现类似如下界面。

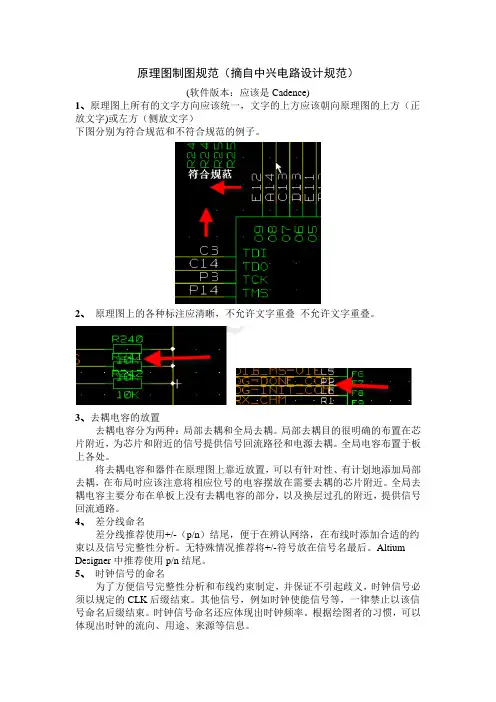

原理图制图规范(摘自中兴电路设计规范)(软件版本:应该是Cadence)1、原理图上所有的文字方向应该统一,文字的上方应该朝向原理图的上方(正放文字)或左方(侧放文字)下图分别为符合规范和不符合规范的例子。

2、原理图上的各种标注应清晰,不允许文字重叠不允许文字重叠。

3、去耦电容的放置去耦电容分为两种:局部去耦和全局去耦。

局部去耦目的很明确的布置在芯片附近,为芯片和附近的信号提供信号回流路径和电源去耦。

全局电容布置于板上各处。

将去耦电容和器件在原理图上靠近放置,可以有针对性、有计划地添加局部去耦,在布局时应该注意将相应位号的电容摆放在需要去耦的芯片附近。

全局去耦电容主要分布在单板上没有去耦电容的部分,以及换层过孔的附近,提供信号回流通路。

4、差分线命名差分线推荐使用+/-(p/n)结尾,便于在辨认网络,在布线时添加合适的约束以及信号完整性分析。

无特殊情况推荐将+/-符号放在信号名最后。

Altium Designer中推荐使用p/n结尾。

5、时钟信号的命名为了方便信号完整性分析和布线约束制定,并保证不引起歧义,时钟信号必须以规定的CLK后缀结束。

其他信号,例如时钟使能信号等,一律禁止以该信号命名后缀结束。

时钟信号命名还应体现出时钟频率。

根据绘图者的习惯,可以体现出时钟的流向、用途、来源等信息。

例如:FPGA1_8K_CLK,FPGA2_33M_CLK,OIB0_52CHIP_TCLK 都是符合规范的命名。

串联端接时钟网络的命名参见串联端接网络的绘制和命名6、串联端接网络的绘制和命名对于源端端接网络,正确的画法应该是将串阻直接画在驱动器件的输出端,串阻和驱动器件之间的网络可以不进行命名,串阻之后的网络进行命名。

如下图所示为一个正确的范例。

如果将串阻放在接收端,或者在串阻之前的信号进行命名,串阻之后的信号不进行命名,都会使得布线的分析和检查困难,甚至会造成串阻被放置在接收端而未被查出的结果,导致信号完整性较差。

cadence原理图设计报告

工具:Design Entry CIS

设计目标:绘制原理图库与原理图,最终产生网表文件(PCB设计使用)。

1.1新建原理图工程

原理图工程以.opj结尾,原理图以.DSN后缀结束;原理图库以.OLB后缀1.2新建多个原理图部分

右击可以设置成根原理图部分。

1.3设置原理图纸张大小

1.4tools 下可以设置工具窗口显示与隐藏

1.5options-P可以设置背景颜色等,设置点状与线状背景。

1.6options-D可以设置原理图纸的大小等

2制作库文件

2.1新建library

file-->new-->library(点击保存,设置库名称)

2.2创建元件右键new--》part

2.3设置器件属性:名称,填写封装,类型等

2.4设置好管教后添加边框

2.5放置器件

(可以添加不同路径的库文件进来)

2.6view--》page

设置管教属性状态

2.7添加库文件,复制元器件进入自己库

2.8

支持不同原理图间元器件的拷贝、

原理图中的原价有错误可以直接编辑库文件,然后更新原理图中对应的器件

器件的名称不允许重复可以讲引脚属性设置成pow属性

2.9同page放置网络标号

2.10不是同一页的网络标号放置offpage

2.11填写封装

2.12更新缓存

2.13DRC检查

2.14输出网表文件

(1)第一方网表文件,用于PCB设计。

出现错误时需要修改至没错才会产生。

(2)第三方网表文件

2.15导出BOM表单

(注意添加封装信息)。

原理图设计简介本文简要介绍了原理图的设计过程,希望能对初学者有所帮助。

一.建立一个新的工程在进行一个新的设计时,首先必须利用Project Manager 对该设计目录进行配置,使该目录具有如下的文件结构。

所用的文件库信息。

Design directory 启动Project ManagerOpen: 打开一个已有Project .New :建立一个新的Project . 点击New 如下图:cadence 将会以你所填入的project name 如:myproject 给project file 和design library 分别命名为myproject.cpm和myproject.lib点击下一步Available Library:列出所有可选择的库。

包括cadence自带库等。

Project Library:个人工程中将用到的所有库。

如myproject_lib点击下一步点击下一步点击Finish完成对设计目录的配置。

为统一原理图库,所有共享的原理图库统一放在CDMA硬件讨论园地----PCB设计专栏内。

其中:libcdma 目录为IS95项目所用的器件库。

libcdma1目录为IS95项目之后所用的器件库。

每台机器上只能存放一套共享的原理图库,一般指定放在D:盘的根目录下,即:D:\libcdma , D:\libcdma1 ...* 注意:设计开始时,应该首先将机器上的库与共享的原理图库同步。

下面介绍如何将共享库加入到自己的工程库中。

点击Setup点击Edit 编辑cds.lib文件。

添入以下语句:define libcdma d:\libcdmadefine libcdma1 d:\libcdma1则库libcdma , libcdma1被加入Availiable Library 项内。

如下图:点击Add依次将库libcdma , libcdma1加入右边自己的工程库中。

另:可通过右端Up, Down键排列库的优先级。

C e n c e原理图设计技巧集团企业公司编码:(LL3698-KKI1269-TM2483-LUI12689-ITT289-C a d e n c e原理图设计技巧一、工具栏介绍二、原理图设计规范三、原理图设计基本步骤生成文件网表用于制作PCB文件元器件明细用于制作明细表元器件清单用于器件采购Tcl文件用于导入QuartusII进行FPGA管脚验证个人经验:生成的文件以pdf格式打印出来(包括原理图),更加方便使用四、常用操作(1)元器件镜像翻转:选中后Edit/Mirror/Horizontally(水平)/Vertically(垂直)(2)Edittext内容换行:Ctrl+Enter(3)元器件批量修改:选中所需修改的元器件,右键EditProperties (4)在管脚标示上加横线Eg:1OE—》1O\E\回车(5)元件库中填充:选中闭环的图形,右键选中EditPropertiesFilestyle下拉列表选中Soild常用快捷键-1.放大/缩小——I/O或Ctrl+滚轮上/下2.放置元器件——P3.放置地——G4.元器件旋转——R5.放置wire——W6.放置Net——N7.放置Text——T五、基本技巧1.Find功能使用然后点击工程dsn文件,Ctrl+F调出查找MatchCase:大小写匹配Highlight:高亮显示所查网络/器件2.生成元器件清单选中DSN文件,Tools/BillofMaterials3.如何检查原理图错误(1)查看原理图中的元器件信息如下图(2)查看网络信息双击某一网络即可查看其在原理图中的位置,进而检查原理图错误(3)DRC检查选中工程DSN文件,Tools/DesignRulesCheck4.从原理图中导出网表设置完毕之后,会在指定路径下产生pstchip.dat,pstxnet.dat,patxprt.dat文件pstchip.dat:记录的是各个封装的相关参数pstxnet.dat:记录各个器件引脚的电气连接关系patxprt.dat:记录的是各个器件对应的封装类型5.关于输出文件的打印File/Print,选中Setup进行打印设置,选中虚拟打印机,这里安装的是AdobePDF(Acrobat9.0Pro)然后选择纸张大小、方向,确定即可。

原理图设计规范

理念: 设计好一份规范的原理图对设计好PCB/跟机/做客户资料具有指导性意义,是做好一款产品的基础。

一、标准图框图幅

根据实际需要,我公司常用图幅为A2、A3、A4,并有标准格式的图框。

其中每一图幅可根据方向分为Landscape(纵向)及Portrait(横向)。

在选用图纸时,应能准确清晰的表达区域电路的完整功能。

二、电路布局

原理图的作用是表示电路连接关系,因此需要注意电路结构的易读性。

一般可将电路按照功能划分成几个部分,并按照信号流程将各部分合理布局。

连线时,需注意避免线条的不必要交叉,以免难于辨识。

具体要求如下:

1. 各功能块布局要合理, 整份原理图需布局均衡. 避免有些地方很挤,而有些

地方又很松, PCB 设计同等道理.

2. 尽量将各功能部分模块化(如功放,RADIO, E.VOL, SUB-WOOFER 等),以便于同

类机型资源共享, 各功能模块界线需清晰.

3. 接插口(如电源/喇叭插座, AUX IN, RCA OUTPUT, KB/CD SERVO 接口等)尽

量分布在图纸的四周围, 示意出实际接口外形及每一接脚的功能.

4. 可调元件(如电位器), 切换开关等对应的功能需标识清楚.

5. 滤波器件(如高/低频滤波电容,电感)需置于作用部位的就近处.

6. 重要的控制或信号线需标明流向及用文字标明功能.

7. CPU 为整机的控制中心, 接口线最多. 故CPU周边需留多一些空间进行布线

及相关标注,而不致于显得过分拥挤.

8. CPU 的设置管脚(如AREA1/AREA2, CLOCK1/CLOCK2等)需于旁边做一表格进

行对应设置的说明.

9. 重要器件(如接插座,IC, TUNER 等)外框用粗体线(统一 0.5mm).

10. 元件标号照公司要求按功能块进行标识.

11. 元件参数/数值务求准确标识. 特别留意功率电阻一定需标明功率值, 高耐

压的滤波电容需标明耐压值.

12. 每张原理图都需有公司的标准图框,并标明对应图纸的功能,文件名,制图人

名/审核人名, 日期, 版本号.

13. 计初始阶段工程师完成原理图设计并自我审查合格后, 需提交给项目主

管进行再审核, 直到合格后才能开始进行PCB 设计.

三、元件标注

1.元件标注最基本信息,即显示在图上的信息应该包括元器件位号和元器件值。

其中元器件位号一般根据元器件种类以不同的英文字符表示,一般以英文首位字母表示:电阻 R

电容 C

电感 L

变压器 T

二极管 D

三极管 Q

继电器 RL

集成电路 IC、U

接插件 CN、CZ、JP

根据在机器内分板不同或者实现功能不同,可在字母前后加一位固定数值,例如:1RXX、C2XX等。

长度一般控制在4个字符以下,少部分可以5个字符表示。

而元器件值应该包含元件值和必要的额定值。

2.电阻

≤1ohm 以小数表示,而不以毫欧表示 0RXX,例如0R47、0R033

≤999ohm 整数表示为 XXR,例如100R、470R

包含小数表示为XRX,例如4R7、4R99、49R9

≤999K 整数表示为 XXK,例如100K、470K

包含小数表示为XKX,例如4K7、4K99、49K9

≤1M 整数表示为 XXM,例如1M、10M

包含小数表示为XMX,例如4M7、2M2

电阻如只标数值,则代表其功率低于1/4W。

如果其功率大于1/4W,则需要标明实际功率。

为区别电阻种类可在其后标明: CF碳膜、MF金属膜、PF氧化膜、FS熔断、CE瓷壳。

3.电容

≤1pF 以小数加p表示,例如0p47

≤999pF 整数表示为 XXp,例如100p、470p

包含小数表示为XpX,例如4p7、6p8

≤999nF 整数表示为 XXn,例如100n、470n

包含小数表示为XnX,例如4n7、6n8

习惯上,接近1uF的电容也可以以0.XXu表示,例如0.1u、0.22u

≥1uF 整数表示为 XXu,例如100u、470u、1000u

包含小数表示为XuX,例如4u7、6u8

习惯上,大于1000uF的也可以Xm表示,1m=1000u

容值后标明耐压,以“/”与容值隔开。

电解电容必须标明耐压,其他介质电容,如不标明耐压,则缺省定义为“耐压63V”。

4.电感的电感量标法同电容容量标法。

二、三极管、集成电路以及继电器等标实际型号即可,如有特殊要求可包含档号。

接插件标明脚数即可。

四、字符要求

元器件值和普通说明文字一般使用Arial字体10号字高。

标题性字符可自行设定字体和大小。

字符的放置应尽可能靠近元件符号,并且注意不和周围字符交叠。

五、元器件选择规则

1.电阻:

1.1碳膜电阻,

优点:价格便宜

缺点:热噪声较大,精度较低,大阻值稳定性稍差。

一般在控制电路,以及不引入噪声的区域使用。

1.2金属膜电阻

优点:低噪声,高精度,高稳定性

缺点:价格稍贵,不耐高温

一般用在对于精度、稳定性、噪声有要求的部位。

1.3金属氧化膜电阻

优点:低噪声,高精度,高稳定性,耐高温

缺点:价格贵

一般用于电阻本身高热的情况。

1.4熔断电阻

优点:低噪声,高精度,高稳定性,可熔断

缺点:价格贵

在金属氧化膜电阻的基础上加入助熔剂,一般用在电阻开路可以保护电路的部位。

2.电容:

2.1铝电解电容:

优点:价格便宜,容量大,体积小

缺点:漏电大,寿命短,高频特性差,精度差

一般用在需要容量大的地方

2.2钽电解电容:

优点:相对于铝电解之外的电容,价格便宜,容量大,体积小;相对于铝电解,漏电小,高频特性好。

缺点:相对于铝电解,价格贵,容量小,体积大;相对于铝电解之外的电容,漏电大,高频特性差。

用于数字电路单板退藕

2.3聚酯电容:

优点:高频特性好,精度高,稳定性好

缺点:价格轨,体积大

用于性能要求高的部位

2.4瓷片电容:

优点:超高频特性好

缺点:容量小、易损坏

用在高频滤波、补偿部位

3. PCB板材

3.1 CEM-1

优点:价格便宜,方便开模

缺点:板材强度差,由于工艺造成的线条精度较低

3.2 FR-4

优点:线条精度高,板材强度高

缺点:价格贵,基本不可开模

3.3 对于板材的选择基于的原则是:

客户要求客户有时会根据产品的定位定义板材的使用,对于此定义必须执行。

价格因素综合考虑产品的售价以及实际使用PCB面积,以及批量和模具费用。

性能必要某些产品对稳定性有更高的要求,则可以优先考虑使用较高档的板材。

六、隐藏信息

可在元件中加入元器件的例如生产厂家、型号、成本等信息。

但必须隐藏,以保持图面清晰。

七、图纸更改

对所有已正式下发的图纸的更改,必须按公司程序对更改方案经评审和批准通过后出具ECN(需符合公司关于ECN填写规范),并同时于图纸上明确的标注更改处,更改版本号,ECN 号,并于规定的栏目内简要说明更改细节,更改原因等。

八、文件名及图号编号规则

LY-XXX-XXXX VXX.SCH

1 2 3

1.项目名。

如Z4U、Z11U、W4、CKD等。

2.部件名。

如 0110、0210等,参见结构部件编号。

3.版本号。

如 V1.1等。