SignalTapⅡ嵌入式逻辑分析仪的使用

- 格式:ppt

- 大小:8.31 MB

- 文档页数:96

初步学习使用Signal Tap 进行调试。

使用signal tap需要先建立一个 signaltap II logic analyzer file .将这个文件添加到qeartus project当中。

在此之前要先编译好之前的project,添加好signaltap文件并设置好之后,重新编译,然后下载到FPGA中运行,此时,在signaltap的操作界面点击运行,就可以看到相关的采样数据。

理解:signal文件是添加到project并编译的,所以一样是下载到了FPGA里面,是实际的电路。

在最后调试完之后,把这部分文件删除再重新编译,不然很浪费FPGa空间。

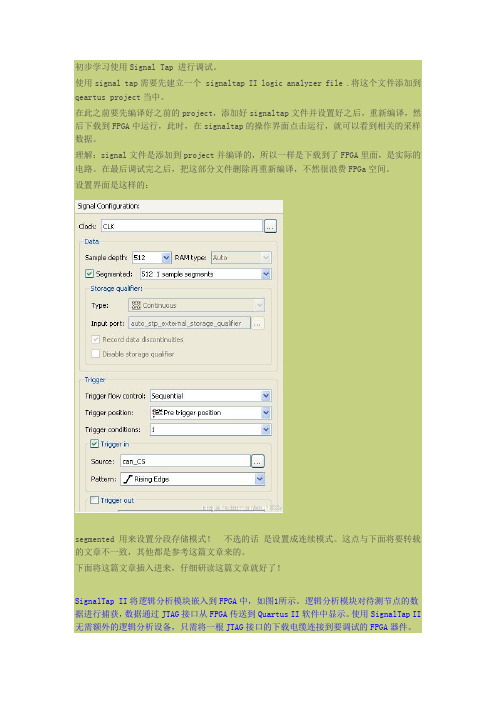

设置界面是这样的:segmented 用来设置分段存储模式!不选的话是设置成连续模式。

这点与下面将要转载的文章不一致,其他都是参考这篇文章来的。

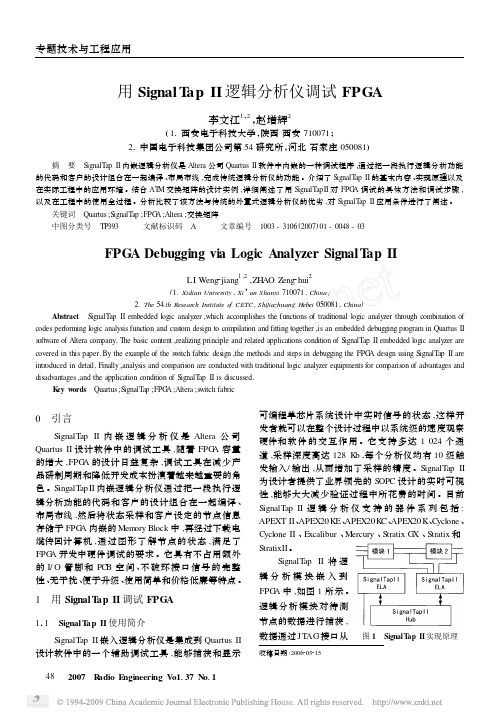

下面将这篇文章插入进来,仔细研读这篇文章就好了!SignalTap II将逻辑分析模块嵌入到FPGA中,如图1所示。

逻辑分析模块对待测节点的数据进行捕获,数据通过JTAG接口从FPGA传送到Quartus II软件中显示。

使用SignalTap II 无需额外的逻辑分析设备,只需将一根JTAG接口的下载电缆连接到要调试的FPGA器件。

SignalTap II对FPGA的引脚和内部的连线信号进行捕获后,将数据存储在一定的RAM块中。

因此,需要用于捕获的采样时钟信号和保存被测信号的一定点数的RAM块。

使用SignalTap II的一般流程是:设计人员在完成设计并编译工程后,建立SignalTap II (.stp)文件并加入工程、配置STP文件、编译并下载设计到FPGA、在Quartus II软件中显示被测信号的波形、在测试完毕后将该逻辑分析仪从项目中删除。

以下描述设置SignalTap II 文件的基本流程:1.设置采样时钟。

采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则无法正确反映被测信号波形的变化。

SignalTap II逻辑分析仪的使用一、例子我们使用如图1所示的verilog代码所实现的开关电路作为例子。

这个电路把DE系列开发板上的前8个开关简单的和对应的8个红色LED相连接。

它是这样工作的:在时钟(CLOCK_50)的上升沿读取开关的值,放入对应的寄存器,寄存器的输出与红色LED直接相连接。

按照图1代码实现该电路,锁定引脚,编译整个工程等等,这些在这里不再重复累述。

二、使用SignalTap II软件在本文的第一部分,我们将建立SignalTap逻辑分析仪来探测8个LED开关的值,同时,我们将设定逻辑分析仪的触发信号为当第一个开关(LED[0])为高电平。

1. 选择File->New打开逻辑分析仪窗口,该窗口如图2所示。

选择SignalTap II逻辑分析仪文件并点击OK。

2. SignalTap II界面如图3所示。

保存文件并命名为switches.stp。

在下一步如图4所示对话框中点击OK,接下来出现对话框”Do you want to enable SignalTap II file‘switches.stp’ for the current project?”询问是否在当前工程中使用SignalTap II,点击Yes(图5)。

现在,SignalTap II 文件switches.stp已经和当前工程相关联了。

注意:如果我们需要在工程中不使用该SignalTap II文件,或者不使用SignalTap II逻辑分析仪,在Quartus II界面中选择Assignments->Settings。

然后在打开窗口左边的分类列表中选择SignalTap II Logic Analyzer,如图6所示。

可以把Enable SignalTap II Logic Analyzer前面的勾去掉来关闭逻辑分析仪。

在一个工程中可能同时会有多个SignalTap文件,但在同一时刻只能有一个有效。

用Signal T ap II 逻辑分析仪调试FPGA李文江1,2,赵增辉2(11西安电子科技大学,陕西西安710071;21中国电子科技集团公司第54研究所,河北石家庄050081)摘 要 S ignalT ap II 内嵌逻辑分析仪是Altera 公司Quartus II 软件中内嵌的一种调试程序,通过把一段执行逻辑分析功能的代码和客户的设计组合在一起编译、布局布线,完成传统逻辑分析仪的功能。

介绍了S ignalT ap II 的基本内容、实现原理以及在实际工程中的应用环境。

结合AT M 交换矩阵的设计实例,详细阐述了用S ignalT apII 对FPG A 调试的具体方法和调试步骤,以及在工程中的使用全过程。

分析比较了该方法与传统的外置式逻辑分析仪的优劣,对S ignalT ap II 应用条件进行了阐述。

关键词 Quartus ;S ignalT ap ;FPG A ;Altera ;交换矩阵中图分类号 TP393 文献标识码 A 文章编号 1003-3106(2007)01-0048-03FPGA Debugging via Logic Analyzer SignalT ap IILI Weng 2jiang 1,2,ZH AO Z eng 2hui 2(1.Xidian Univer sity ,Xi ’an Shanxi 710071,China ;2.The 54th Research Institute o f CETC ,Shijiazhuang Hebei 050081,China )Abstract S ignalT ap II embedded logic analyzer ,which accom plishes the functions of traditional logic analyzer through combination of codes per forming logic analysis function and custom design to com pilation and fitting together ,is an embedded debugging program in Quartus II s oftware of Altera com pany.The basic content ,realizing principle and related applications condition of S ignalT ap II embedded logic analyzer are covered in this paper.By the exam ple of the s witch fabric design ,the methods and steps in debugging the FPG A design using S ignalT ap II are introduced in detail.Finally ,analysis and com paris on are conducted with traditional logic analyzer equipments for com paris on of advantages and disadvantages ,and the application condition of S ignalT ap II is discussed.K ey w ords Quartus ;S ignalT ap ;FPG A ;Altera ;s witch fabric收稿日期:20062052150 引言SignalT ap II 内嵌逻辑分析仪是Altera 公司Quartus II 设计软件中的调试工具,随着FPG A 容量的增大,FPG A 的设计日益复杂,调试工具在减少产品研制周期和降低开发成本扮演着越来越重要的角色。

第10章SignalTapⅡ嵌入式逻辑分析仪的使用10.1 在设计中嵌入SignalTapⅡ逻辑分析仪10.2 在SOPC Builder中使用SignalTapⅡ逻辑分析仪10.3 在DSP Builder中使用SignalTapⅡ逻辑分析仪思考题10.1 在设计中嵌入SignalTapⅡ逻辑分析仪在设计中嵌入SignalTapⅡ逻辑分析仪有两种方法:第一种方法是建立一个SignalTapⅡ文件(.stp),然后定义STP文件的详细内容;第二种方法是用MegaWizard Plug-In Manager建立并配置STP文件,然后用MegaWizard实例化一个HDL输出模块。

图10.1给出用这两种方法建立和使用SignalTapⅡ逻辑分析仪的过程。

SignalTapMegaWizardQuartusSTPQuartus,/ 图10.1 SignalTapⅡ操作流程10.1.1 使用STP文件建立嵌入式逻辑分析仪1.创建STP文件STP文件包括SignalTapⅡ逻辑分析仪设置部分和捕获数据的查看、分析部分。

创建一个STP文件的步骤如下:(1) 在QuartusⅡ软件中,选择File→New命令。

(2) 在弹出的New对话框中,选择Other Files标签页,从中选择SignalTapⅡ File,如图10.2所示。

图10.2 新建一个STP文件(3) 点击OK按钮确定,一个新的SignalTapⅡ窗口如图10.3所示。

DataS etup图10.3 SignalTapⅡ窗口上面的操作也可以通过Tools→SignalTapⅡLogic Analyzer命令完成,这种方法也可以用来打开一个已经存在的STP文件。

2.设置采集时钟在使用SignalTapⅡ逻辑分析仪进行数据采集之前,首先应该设置采集时钟。

采集时钟在上升沿处采集数据。

设计者可以使用设计中的任意信号作为采集时钟,但Altera建议最好使用全局时钟,而不要使用门控时钟。

SignalTapII及SignalProbe使用指南1.SignalTapII支持器件及下载电缆SignalTapII内嵌式逻辑分析仪需要占用ALMs/LEs布线资源和RAM采样存储资源,支持下面的器件系列:StratxiII、Stratix、StratixIIGX、StratixGX、CycloneII、Cyclone、APEXII、APEX20K/E/C、Excalibur和Mercury。

SignalII逻辑分析仪支持目前Altera所有下载电缆,包括USB Blaster、ByteBlasterII、ByteBlasterMV和MasterBlaster。

2.SignalTapII工作流程及资源消耗○1配置ELA(Embedded Logic Analyzer)。

○2通过QuartusII软件完成布局布线,ELA下载至FPGA中。

○3ELA采样到内部触发信号。

○4ELA通过JTAG电路与QuartusII软件发生通信,以图形化的界面显示出来。

ELA占用片内LE资源由信号通道数及触发级数决定,占用片内RAM资源由信号通道数及采样深度来决定。

Altera建议选择选择通道数量和采样深度时要考虑二者之间的平衡,以免占用太多RAM资源,影响原本的逻辑设计。

比如不推荐同时使用1024个最大通道数和128K最大采样深度(相当于消耗了32,768 个M4K的资源)。

下表给出了在Statix/Cyclone 器件中使用ELA的资源占用情况。

3.SignalTapII设计流程在设计中嵌入SignalTapII有两种方法:一是创建一个SignalTapII文件(.stp),然后定义STP文件的详细内容;二是用MegaWizard Plug-In Manager建立并配置STP文件,然后用MegaWizard实例化一个HDL输出模块。

1)创建STP文件在QuartusII软件中选择File菜单下New命令,弹出的New对话框中选择Other Files 标签栏,选择SignalTap II File。

逻辑分析仪使用方法逻辑分析仪是一种用于测试和分析电子设备中信号波形的仪器,它在电子工程领域中有着广泛的应用。

逻辑分析仪的使用方法对于工程师和技术人员来说至关重要,正确的使用方法可以帮助他们更准确地分析和解决问题。

下面将介绍逻辑分析仪的使用方法,希望能对大家有所帮助。

首先,使用逻辑分析仪之前需要对仪器本身有所了解。

逻辑分析仪通常包括输入端口、触发设置、采样率、存储深度等功能。

在开始使用之前,需要对这些功能有所了解,并且熟悉仪器的操作界面和按钮功能。

在连接逻辑分析仪之前,需要确保被测试的电子设备已经断电,并且对测试线进行正确的连接。

一般来说,逻辑分析仪会有多个输入通道,需要根据测试的需要选择合适的通道进行连接。

接下来是设置触发条件。

触发条件是指当输入信号满足一定的条件时,逻辑分析仪开始采集数据。

在设置触发条件时,需要根据被测试设备的信号特点来进行设置,以确保能够捕获到需要分析的信号波形。

采样率和存储深度也是需要注意的地方。

采样率决定了逻辑分析仪对信号波形的采样速度,而存储深度则决定了能够存储的波形数据量。

在进行设置时,需要根据被测试设备的信号特点来进行调整,以确保能够捕获到完整的波形数据。

在一切准备就绪后,可以开始对被测试设备进行电源供给,并进行数据采集。

在采集过程中,需要留意观察逻辑分析仪的显示屏,确保能够捕获到需要的信号波形。

最后,在数据采集完成后,需要对采集到的数据进行分析和处理。

逻辑分析仪通常会提供数据分析的功能,可以对采集到的波形数据进行放大、缩小、测量等操作,以便更好地分析和理解信号波形的特点。

总的来说,逻辑分析仪的使用方法并不复杂,但是需要对仪器本身有所了解,并且根据被测试设备的信号特点进行合理的设置和操作。

希望以上介绍能够对大家在使用逻辑分析仪时有所帮助。

逻辑分析仪使用方法逻辑分析仪是一种用于测试和分析数字信号的仪器,广泛应用于电子、通信、计算机等领域。

它能够帮助工程师快速准确地分析数字电路中的信号,发现问题并进行调试。

下面将介绍逻辑分析仪的基本使用方法,希望能帮助您更好地使用这一工具。

首先,使用逻辑分析仪前,需要准备好相应的测试设备和接线。

确保待测电路处于断电状态,并按照逻辑分析仪的说明书,正确连接测试线和探头。

接线完成后,打开逻辑分析仪并设置相应的参数,如采样频率、触发方式等。

这些参数的设置需要根据具体的测试需求进行调整,以确保能够捕获到需要分析的信号。

接下来,进行信号采集和分析。

在逻辑分析仪上设置好参数后,可以开始进行信号的采集。

通过触发功能,可以使逻辑分析仪在特定条件下自动捕获信号,并将其显示在屏幕上。

在信号捕获后,可以通过逻辑分析仪提供的分析工具,如时序图、状态图等,对信号进行深入分析。

通过观察信号的波形和时序关系,可以快速定位问题,并进行故障排除。

最后,根据分析结果进行调试和优化。

通过逻辑分析仪的帮助,我们可以快速准确地找到问题所在,并进行相应的调试和优化。

在调试过程中,可以通过逻辑分析仪实时监测信号的变化,以便及时调整电路参数并验证效果。

通过不断的分析和调试,最终可以确保电路的稳定性和可靠性。

总之,逻辑分析仪作为一种重要的测试工具,在数字电路设计和调试过程中发挥着不可替代的作用。

正确的使用方法能够帮助工程师更快速地定位问题并进行调试,提高工作效率。

希望本文介绍的逻辑分析仪使用方法能够对您有所帮助,谢谢阅读!。

逻辑分析仪使用方法逻辑分析仪是一种用于测试和分析数字电路信号的仪器,它可以帮助工程师和技术人员快速准确地找出数字电路中的故障和问题。

在使用逻辑分析仪之前,我们需要了解一些基本的使用方法和注意事项,以确保测试的准确性和安全性。

首先,准备工作非常重要。

在使用逻辑分析仪之前,我们需要确保测试设备和被测对象的电源已经关闭,并且连接线路正确。

此外,还需要检查逻辑分析仪的各个部件和连接线是否完好无损,确保仪器的正常工作。

接下来,我们需要正确连接逻辑分析仪。

根据被测对象的信号类型和特点,选择合适的测试夹具和连接线,并将其正确连接到逻辑分析仪上。

在连接过程中,一定要注意连接的稳固性和正确性,避免因连接不良而导致测试结果不准确。

然后,我们可以进行逻辑分析仪的设置。

根据测试的需要,设置逻辑分析仪的采样率、触发条件、触发电平等参数,以确保能够捕获到需要分析的信号。

在设置参数时,需要根据被测对象的信号特点和测试要求进行合理的调整,以获得准确的测试结果。

接着,进行测试操作。

在进行测试之前,需要确保被测对象的电源已经打开,并且处于正常工作状态。

然后,启动逻辑分析仪进行信号采集和分析,观察被测对象的信号波形和特征,以找出其中的问题和异常。

在测试过程中,需要密切关注逻辑分析仪的显示结果,及时发现并记录下异常情况。

最后,进行数据分析和故障定位。

根据逻辑分析仪采集到的数据和波形,进行数据分析和信号特征分析,找出其中的问题和故障原因。

在分析过程中,可以利用逻辑分析仪提供的各种分析工具和功能,帮助快速准确地定位故障,并提出相应的解决方案。

总之,逻辑分析仪是一种非常重要的测试仪器,它可以帮助工程师和技术人员快速准确地找出数字电路中的故障和问题。

在使用逻辑分析仪时,需要严格按照使用方法进行操作,并注意安全和准确性。

希望本文所述的逻辑分析仪使用方法能够对大家有所帮助,谢谢!。