数字电路逻辑设计第3章集成逻辑门综述

- 格式:ppt

- 大小:2.41 MB

- 文档页数:28

习题参考解答第1章基本知识1.什么是数字信号?什么是模拟信号?(注:所有蓝色标题最后均去掉!)答案:数字信号:指信号的变化在时间上和数值上都是断续的,或者说是离散的,这类信号有时又称为离散信号。

例如,在数字系统中的脉冲信号、开关状态等。

模拟信号:指在时间上和数值上均作连续变化的信号。

例如,温度、交流电压等信号。

2.数字系统中为什么要采用二进制?答案:二进制具有运算简单、物理实现容易、存储和传送方便、可靠等优点。

3.机器数中引入反码和补码的主要目的是什么?答案:将减法运算转化为加法运算,统一加、减运算,使运算更方便。

4.BCD码与二进制数的区别是什么?答案:二进制数是一种具有独立进位制的数,而BCD码是用二进制编码表示的十进制数。

5.采用余3码进行加法运算时,应如何对运算结果进行修正?为什么?答案:两个余3码表示的十进制数相加时,对运算结果修正的方法是:如果有进位,则结果加3;如果无进位,则结果减3。

为了解决四位二进制运算高位产生的进位与一位十进制运算产生的进位之间的差值。

6.奇偶检验码有哪些优点和不足?答案:奇偶检验码的优点是编码简单,相应的编码电路和检测电路也简单。

缺点是只有检错能力,没有纠错能力,其次只能发现单错,不能发现双错。

7.按二进制运算法则计算下列各式。

答案:(1)110001 (2)110.11 (3)10000111 (4)1018.将下列二进制数转换成十进制数、八进制数和十六进制数。

答案:(1)(117)10 ,(165)8 ,(75)16(2)(0.8281)10 ,(0.65)8 ,(0.D4)16(3)(23.25)10 ,(27.2)8 ,(17. 4)169.将下列十进制数转换成二进制数、八进制数和十六进制数(精确到二进制小数点后4位)。

答案:(1)(1000001)2 ,(101)8 ,(41)16(2)(0.0100)2 ,(0.20)8 ,(0.40)16(3)(100001.0101)2 ,(41.24)8 ,(21.50)1610.写出下列各数的原码、反码和补码。

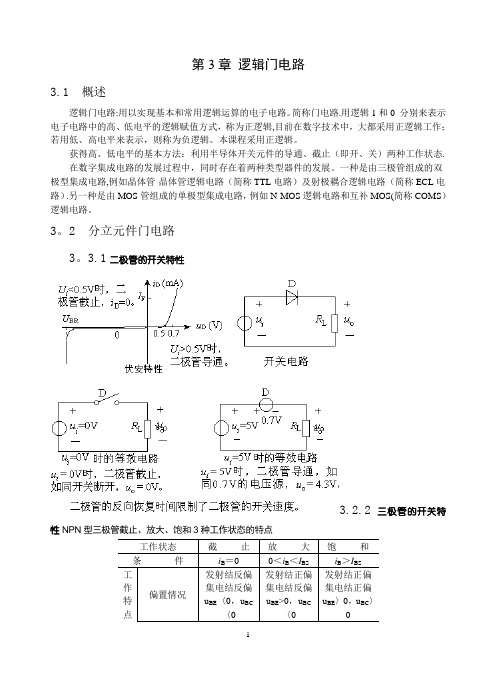

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

路。

简称门电路。

5V一、TTL 与非门图3-1 典型TTL 与非门电路3.2 TTL 集成门电路•数字集成电路中应用最广的为TTL 电路(Transister-Transister-Logic 的缩写)•由若干晶体三极管、二极管和电阻组成,TTL 集成电路有54/74系列 ①输出高电平UOH 和输出低电平UOL 。

•输出高电平U OH:至少有一个输入端接低电平时的输出电平。

•输出低电平U OL:输入全为高电平时的输出电平。

• 电压传输特性的截止区的输出电压UOH=3.6V,饱和区的输出电压UOL=0.3V。

一般产品规定U OH≥2.4V、U OL<0.4V时即为合格。

二、TTL与非门的特性参数③开门电平U ON 和关门电平U OFF 。

开门电平U ON 是保证输出电平达到额定低电平(0.3V )时,所允许输入高电平的最低值,表示使与非门开通的最小输入电平。

通常U ON =1.4V ,一般产品规定U ON ≤1.8V 。

关门电平U OFF 是保证输出电平为额定高电平(2.7V 左右)时,允许输入低电平的最大值,表示与非门关断所允许的最大输入电平。

通常U OFF ≈1V ,一般产品要求U OFF ≥0.8V 。

5). 扇入系数Ni和扇出系数N O 是指与非门的输入端数目。

扇入系数Ni是指与非门输出端连接同类门的个数。

反扇出系数NO映了与非门的带负载能力。

6)输入短路电流I IS 。

当与非门的一个输入端接地而其余输入端悬空时,流过接地输入端的电流称为输入短路电流。

7)8)平均功耗P 指在空载条件下工作时所消耗的电功率。

三、TTL门电路的改进 74LS系列 性能比较好的门电路应该是工作速度既快,功耗又小的门电路。

因此,通常用功耗和传输延迟时间的乘积(简称功耗—延迟积或pd积)来评价门电路性能的优劣。

74LS系列又称低功耗肖特基系列。

74LS系列是功耗延迟积较小的系列(一般t pd<5 ns,功耗仅有2 mW) 并得到广泛应用。

数字电路逻辑设计(第二版) 王毓银电子科技大学第1章绪论1.1 数字信号1.2 数制及其转换1.3 二一十进制代码(BCD代码)1.4 算术运算与逻辑运算1.5 数字电路1.6 VHDL1.7 本课程的任务与性质习题第2章逻辑函数及其简化2.1 逻辑代数2.1.1 基本逻辑2.1.2 基本逻辑运算2.1.3 真值表与逻辑函数2.1.4 逻辑函数相等2.1.5 三个规则2.1.6 常用公式2.1.7 逻辑函数的标准形式2.2 逻辑函数的简化2.2.1 公式法(代数法)2.2.2 图解法(卡诺图法)2.2.3 逻辑函数的系统简化法习题第3章集成逻辑门3.1 晶体管的开关特性3.1.1 晶体二极管开关特性3.1.2 晶体三极管开关特性3.2 TTL集成逻辑门3.2.1 晶体管一晶体管逻辑门电路(TTL)3.2.2 TTL与非门的主要外部特性3.2.3 TTL或非门、异或门、OC门、三态输出门等3.2.4 其他系列TTL门电路3.3 发射极耦合逻辑(ECL)门与集成注入逻辑(I2L)电路3.3.1 发射极耦合逻辑(ECL)门3.3.2 I2L逻辑门3.4 MOS逻辑门3.4.1 MOS晶体管3.4.2 MOS反相器和门电路3.5 CMOS电路3.5.1 CMOS反相器工作原理3.5.2 CMOS反相器的主要特性3.5.3 CMOS传输门3.5.4 CMOS逻辑门电路3.5.5 BiCMOS门电路3.5.6 CMOS电路的正确使用方法3.6 VHDL描述逻辑门电路3.6.1 VHDL描述电路的基本方法3.6.2 VHDL描述逻辑门电路习题第4章组合逻辑电路4.1 组合逻辑电路分析4.1.1 全加器4.1.2 编码器4.1.3 译码器4.1.4 数值比较器4.1.5 数据选择器4.1.6 奇偶产生/校验电路4.2 组合逻辑电路设计4.2.1 采用小规模集成器件的组合逻辑电路设计4.2.2 采用中规模集成器件实现组合逻辑函数4.3 组合逻辑电路的冒险现象4.3.1 静态逻辑冒险4.3.2 如何判断是否存在逻辑冒险4.3.3 如何避免逻辑冒险4.4 VHDL描述组合逻辑电路4.4.1 VHDL表达式、运算符和数据类型4.4.2 在结构体行为描述中常用语句4.4.3 结构描述语句4.4.4 VHDL语句描述组合逻辑电路习题第5章集成触发器5.1 基本触发器5.1.1 基本触发器电路组成和工作原理5.1.2 基本触发器功能的描述5.2 钟控触发器5.2.1 钟控R—S触发器5.2.2 钟控D触发器5.2.3 钟控J-K触发器5.2.4 钟控T触发器5.2.5 电位触发方式的工作特性5.3 主从触发器5.3.1 主从触发器基本原理5.3.2 主从J-K触发器主触发器的一次翻转现象5.3.3 主从J-K触发器集成单元5.3.4 集成主从J-K触发器的脉冲工作特性5.4 边沿触发器5.4.1 维持一阻塞触发器5.4.2 下降沿触发的边沿触发器5.4.3 CMOS传输门构成的边沿触发器5.5 VHDL描述触发器5.5.1 时钟信号和复位、置位信号的VHDL描述5.5.2 触发器的VHDL描述习题第6章时序逻辑电路6.1 时序逻辑电路概述6.2 时序逻辑电路分析6.2.1 时序逻辑电路的分析步骤6.2.2 寄存器、移位寄存器6.2.3 同步计数器6.2.4 异步计数器6.3 时序逻辑电路设计6.3.1 同步时序逻辑电路设计的一般步骤6.3.2 采用小规模集成器件设计同步计数器6.3.3 采用小规模集成器件设计异步计数器6.3.4 采用中规模集成器件实现任意模值计数(分频)器6.4 序列信号发生器6.4.1 设计给定序列信号的产生电路6.4.2 根据序列循环长度M的要求设计发生器电路6.5 时序逻辑电路的VHDL描述6.5.1 移位寄存器的VHDL描述6.5.2 计数器的VHDL描述习题第7章半导体存储器7.1 概述7.1.1 半导体存储器的特点与应用7.1.2 半导体存储器的分类7.1.3 半导体存储器的主要技术指标7.2 顺序存取存储器(SAM)7.2.1 动态CMOS反相器7.2.2 动态CMOS移存单元7.2.3 动态移存器和顺序存取存储器(SAM)7.3 随机存取存储器(RAM)7.3.1 RAM的结构7.3.2 RAM存储单元7.3.3 RAM集成片HM6264简介7.3.4 RAM存储容量的扩展7.4 只读存储器(ROM)7.4.1 固定ROM7.4.2 可编程ROM7.4.3 利用ROM实现组合逻辑函数7.4.4 EPROM集成片简介习题第8章可编程逻辑器件8.1 可编程逻辑器件基本结构8.1.1 “与一或”阵列结构8.1.2 查找表结构8.1.3 可编程逻辑器件编程技术8.2 简单可编程逻辑器件(SPLD)8.2.1 PAL器件的基本结构8.2.2 GAL器件的基本结构8.2.3 典型GAL器件8.3 复杂可编程逻辑器件(CPLD)8.3.1 概述8.3.2 可编程互连阵列结构CPLD8.3.3 全局互连结构CPLD8.4 现场可编程门阵列(FPGA)器件8.4.1 概述8.4.2 连续互连型FPGA器件8.4.3 分段互连型FPGA器件8.4.4 FPGA器件特点8.5 可编程逻辑器件的开发8.5.1 PLD设计流程8.5.2 PLD编程与配置习题第9章脉冲单元电路9.1 脉冲信号与电路9.1.1 脉冲信号9.1.2 脉冲电路9.2 集成门构成的脉冲单元电路9.2.1 施密特触发器9.2.2 单稳态触发器9.2.3 多谐振荡器9.3 555定时器及其应用9.3.1 555定时器的电路结构9.3.2 用555定时器构成施密特触发器9.3.3 用555定时器构成单稳态触发器9.3.4 用555定时器构成多谐振荡器习题第10章模数转换器和数模转换器10.1 概述10.1.1 数字控制系统1O.1.2 数据传输系统10.1.3 自动测试和测量设备10.1.4 多媒体计算机系统10.2 数模转换器(DAC)10.2.1 数模转换原理和一般组成10.2.2 权电阻网络DAC10.2.3 R-2R倒T形电阻网络DAC10.2.4 单值电流型网络DAC10.2.5 集成DAC及其应用举例10.2.6 DAC的转换精度与转换速度10.3 模数转换器(ADC)10.3.1 模数转换基本原理10.3.2 并联比较型ADC10.3.3 逐次逼近型ADC10.3.4 双积分型ADC10.4 集成ADC及其应用举例10.4.1 双积分型集成ADC10.4.2 逐次逼近型集成ADC10.4.3 ADC的转换精度和转换速度习题第11章数字系统设计基础11.1 数字系统设计的基本方法11.1.1 数字系统的组成11.1.2 数字系统设计方法11.2 系统控制器的描述11.2.1 ASM图描述方法11.2.2控制器设计——硬件实现11.2.3控制器设计——软件设计(VHDL描述)11.3 数字系统设计举例11.3.1 方案构思11.3.2 顶层的VHDL实现11.3.3 次级模块电路分析与设计11.3.4 控制器电路的设计习题附录一半导体集成电路型号命名方法附录二集成电路主要性能参数附录三二进制逻辑单元图形符号说明主要参考文献汉英名词术语对照。