iCORE扩展板原理图注释版_by_i7

- 格式:pdf

- 大小:396.89 KB

- 文档页数:5

Capture Allegro学习笔记Allegro中常见的文件格式.brd 工具:PCB Design Expert PCB布线.ddb 工具:Protel.art 工具:CAM350 Allegro PCB Design file/impot ARTwork.d 工具:pads2005.drl 工具:Protel.opj 设计项目工程.olb 创建新的元件库allegro/APD.jrl :记录开启Allegro/APD 期间每一个执行动作的command . 产生在每一次新开启Allegro/APD 的现行工作目录下.env :存在pcbenv 下,无扩展名,环境设定档.allegro/APD.ini :存在pcbenv 下,记录menu 的设定.allegro/APD.geo :存在pcbenv 下,记录窗口的位置.master.tag :开启Allegro/APD 期间产生的文字文件,记录最后一次存盘的database文件名称,下次开启Allegro/APD 会将档案load 进来.从Allegro/APD.ini搜寻directory = 即可知道Master.tag 存在的位置 . lallegro.col :存在pcbenv 下,从设定颜色的调色盘Read Local 所写出的档案.只会影响到调色盘的24 色而不会影响class/subclass 的设定..brd :board file (Allegro)..mcm :multi-chip module (APD) ,design file..log :记录数据处理过程及结果..art :artwork 檔..txt :文字文件,如参数数据,device 文件 .. 等..tap :NC drill 的文字文件..dat :资料文件..scr :script 或macro 记录文件..pad :padstack 檔..dra :drawing 档, create symbol 前先建drawing ,之后再compiled 成binary symbol 档..psm :package symbol ,实体包装零件..osm :format symbol , 制造,组装,logo图形的零件..ssm :shape symbol , 自订pad 的几何形状,应用在Padstack Designer. .bsm :mechanical symbol , 没有电器特性的零件..fsm :flash symbol , 负片导通孔的连接方式..mdd :module ,模块,可在Allegro 建立,包含已placed , routed 的数据..sav :corrupt database,当出现此种档案时,表示你的板子的数据结构已经破坏,情况不严重可以用DB Doctor修复。

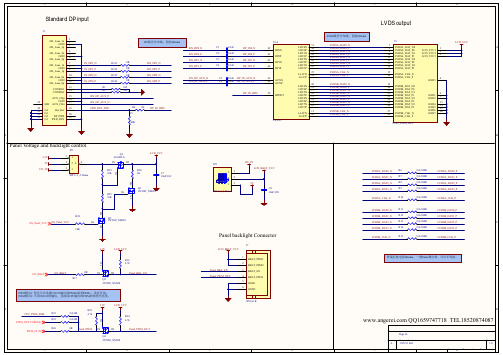

112233445566DDCCB BA ATitleSizeDocument NumberRevDate:Sheetof52APage 011.0CS5211 RefHPD_DET_DP0DP_IN_AUX_P DP_IN_HPDDP_IN0_N DP_IN1_PDP_IN1_N DP_IN0_P DP_IN_AUX_N LVDSA_DAT0_NLVDSA_DAT1_N LVDSA_DAT2_N LVDSA_CLK_N LVDSA_DAT3_N LVDSB_DAT0_N LVDSB_DAT1_N LVDSB_DAT2_N LVDSB_CLK_N LVDSB_DAT3_N LVDSA_DAT0_P LVDSA_DAT1_P LVDSA_DAT2_P LVDSA_CLK_P LVDSA_DAT3_P LVDSB_DAT0_P LVDSB_DAT1_P LVDSB_DAT2_P LVDSB_CLK_PLVDSB_DAT3_P RX_DP0_PRX_DP0_N RX_DP1_NRX_DP1_PRX_DP_AUX_P RX_DP_AUX_NEN_BKLTEN_Panel_VCCPanel_BKL_ENPanel_PWM_OUTPanel_BKL_ENPanel_PWM_OUTPanel_PWMCPU_PWM_DIMDP_IN_HPDR260RR244.7k1G3D2S Q22N7002_NMOS1G3D2S Q1AO3401AC60.1uF C50.1uF R14NA/100R C710uF/16VR7NA/100R R23NA/0RGND26GND15BKLT_PWM4BKLT_EN3BKLT_PWR22BKLT_PWR11J7WF1x6-RR10NA/100R1G 3D2SQ52N7002_NMOS1G 3D2SQ32N7002_NMOSR201KR21M R13NA/100R R21NA/0RC810uF/16VR1910KR9NA/100R11442233JP1SIP 3+1_2.54mmR164.7kR2510KR2810KR11MR41KR12NA/100R R5100KC20.1uF R15NA/100RR170RC40.1uFR8NA/100R 112233JP2SIP 1x3_2.54mmML_Lane_3n1ML_Lane_2n4ML_Lane_1n7ML_Lane_0n10ML_Lane_3p3ML_Lane_2p 6ML_Lane_1p 9ML_Lane_0p 12GND2GND 5GND8GND11CONFIG113CONFIG214GND 16Hot_Det18AUX_CHp15AUX_CHn 17DP_PWR 20PWR_RTN 19G121G222G323G424MH25J1R6NA/100R C10.1uF C30.1uF R224.7kR11NA/100R LCD_VCC11LCD_VCC33GND25LVDSA_DAT_N07LVDSA_DAT_N19LVDSA_DAT_N211GND413LVDSA_CLK_N 15LVDSA_DAT_N317LVDSB_DAT_N019LVDSB_DAT_N121LVDSB_DAT_N223GND625LVDSB_CLK_N27LVDSB_DAT_N329LCD_VCC22GND14GND36LVDSA_DAT_P08LVDSA_DAT_P110LVDSA_DAT_P212GND514LVDSA_CLK_P16LVDSA_DAT_P318LVDSB_DAT_P020LVDSB_DAT_P122LVDSB_DAT_P224GND726LVDSB_CLK_P28LVDSB_DAT_P330J5CON_LVDS_OUT1G3D2S Q42N7002_NMOS12V_IN5V3.3V3.3VLCD_BKLT_VCCLCD_VCCLCD_VCCLCD_BKLT_VCCEN_Panel_VCCEN_BKLTPWM_OUT1/GPIO(4)PWM_OUT0Standard DP inputPanel V oltage and backlight controlLVDS output12V_INRX_DP_AUX_P RX_DP_AUX_NLVDSA_DAT0_N LVDSA_DAT1_N LVDSA_DAT2_NLVDSA_CLK_NLVDSA_DAT3_N LVDSB_DAT0_NLVDSB_DAT1_N LVDSB_DAT2_N LVDSB_CLK_NLVDSB_DAT3_NLVDSA_DAT0_P LVDSA_DAT1_P LVDSA_DAT2_P LVDSA_CLK_PLVDSA_DAT3_P LVDSB_DAT0_P LVDSB_DAT1_P LVDSB_DAT2_P LVDSB_CLK_PLVDSB_DAT3_P 3.3V 5V RX_DP1_N RX_DP1_P RX_DP0_PRX_DP0_N R1230R R1240RR1250R R1260RIN_DP1_N IN_DP1_P IN_DP0_PIN_DP0_N LCD_VCCLCD_VCCLVDS 线差分布线,阻抗100ohmDP 线差分布线,阻抗100ohm Panel backlight Connector终端匹配电阻100ohm ,一般Panle 都自带,可以不焊接。

CC2650开发板DIY之五——PCB设计原理图一、开发板逻辑原理图如前所述,CC2650是一个功能丰富,特点鲜明的全能型射频通讯管理芯片,简单地把主要的功能引脚引出的开发板设计是好的设计方案,不过不大符合不断地给自己找麻烦的DIY的精神。

因此,这次开发板的设计是借鉴和参考了TI提供的若干个参考设计,围绕CC2650的2个特点进行设计:提供传感器信号以实现对sensor control的实现,以及利用独特的bootloader功能实现程序重载的NapOS的实现。

所以就围绕CC2650的开发板设计就有电源部分,射频部分,环境传感器部分和外围接口部分组成。

二、PCB设计参数和主要元件封装2.1 PCB基板考虑用标准的4层板设计:top layer, groundlayer, power layer, bottom layer。

原计划的2层板实现应该不容易实现最短走线,暂不考虑。

2.2 天线采用PCB板载天线,采用比较小的折线方案。

其实除了外置扩展天线,各种PCB板载天线在传输数据上差别不是很显著。

如下图:2.3 CC2650F128RGZRRGZ采用了48引脚的QFN48封装。

这个提供的I/O数量最多,在各种封装中尺寸最大,容量也最大,Flash大大128K,便于测试多种协议栈的要求。

支持多种I/O接口方式。

可以有多种供电方式,采用第一种供电方案,1路工作电压3.3V,最高耐受电压4.1V。

2.4 HDC1000YPAT 温湿度传感器采用DSBGA封装,8点焊接,工作电压3.3V,最大耐受电压6V。

采用I2C通讯方式。

2.5 OPT3001DNPR 高亮度传感器。

USON封装,6引脚。

工作电压3.3V(工作范围1.6-3.6V),最大耐受电压5.5V。

采用I2C通讯方式。

2.6 TMP107BID高精度温度传感器SOIC封装。

8引脚。

工作电压3.3V(工作范围1.7-5.5V),最大耐受电压6V。

采用UART通讯方式。

ARM+FPGA iCore4T 双核心工控板硬件手册iCore4T双核心工控板简介1.硬件资源及特性2.ARM核心3.FPGA核心4.双核心连接模式5.电源管理6.时钟管理7.金手指与标准50P扩展B转USART功能9.SDRAM存储器10.EEPORM存储器11.FLASH存储器12.SDIO接口TF卡13.SWD仿真接口14.单色LED15.FPGA之AS配置模式(可选)16.FPGA之PS配置模式(默认)17.FPGA之JTAG接口1iCore4T双核心工控板简介iCore4T异构双核心板是银杏公司推出的第四代iCore 系列双核心板的升级产品;它具有ARM+FPGA双核心组合,尺寸小,便携性高,可扩展性强等特点。

iCore4T使用DDR3内存条接口,丰富的扩展功能可以满足测试测量,自动控制,数据采集,自主学习等生产生活的需要。

“ARM”核心采用CORTEX-M7内核的STM32H750IBK6芯片,最高主频可达480MHZ,性能可达1027DMIPS。

“ARM”核心作为CPU角色(亦可以说成“串行”执行角色),负责功能实现、事件处理及接口等功能。

芯片提供了双精度浮点单元,DSP指令集等高性能特性;其丰富的通信接口可以满足您大部分的外设扩展。

“FPGA”核心采用Altera公司四年飓风四代FPGA EP4CE10F17C8N,内置强大的锁相环、RAM块、乘法器模块,适用于大多数测试测量、数据采集、接口通信、协议栈转换、自动控制等应用。

ARM通过高速SPI与FPGA进行数据交换,时钟可达130MHz,通过DMA加持,实测传输速度优于13MB/s,高速的数据交换使得两核心之间的协同能力大大增加,它的便利性与实时性使得iCore4T可以应对越来越高的测试测量及自动控制类产品功能、性能的需求。

图1 iCore4T双核心工控板原理框图iCore4T特性如下:ARM核心:采用主频480M的高性能STM32H750IBFPGA核心:采用Altera公司第四代Cyclone 系列FPGA EP4CE10F17C8NARM I/O扩展:多达66个高性能I/O扩展ARM外设扩展:通过金手指可扩展DAC、USB2.0高速/全速、以太网、液晶、I2C、SPI、ADC、UART、CAN、一路DCDC电源等ARM接口扩展:用于调试的USB转UART功能TF卡存储扩展:ARM SDIO接口的TF卡接口扩展FLASH扩展:内置4线高速SPI NOR FLASH,容量达8MBytes,可用于程序代码扩展SDRAM扩展:ARM外扩SDRAM,容量为32M BytesEEPOM扩展:ARM外扩EEPOM,I2C通信,容量为4KbitARM调试口:6P简化后的SWD调试接口,可以选配转接器以适应通用的20p接口FPGA I/O扩展:多达120个高性能I/O扩展与GK50标准扩展的36个I/OPS配置:基于ARM的FPGA重配置功能,可以完成FPGA固件在线更新FPGA调试口:6P简化后的FPGA JTAG端口,可以选配转接器以适应通用的10p接口串行总线:用于ARM与FPGA连接的高速SPI串行总线温度传感器:内置片上温度传感器,可实时监测环境工作温度金手指扩展:金手指包括120个FPGA扩展与66个ARM扩展,可扩展DAC、USB2.0高速/全速、以太网、液晶、I2C、SPI、ADC、UART、CAN、一路DCDC电源等外设电源管理:供电采用USB-UART供电与金手指外部扩展供电同时供电,也可单独选择其中一项供电。