低介电常数材料研究

- 格式:ppt

- 大小:1.72 MB

- 文档页数:35

低介电常数材料的特点、分类及应用胡扬摘要: 本文先介绍了低介电常数材料(Low k Materials)的特点、分类及其在集成电路工艺中的应用。

指出了应用低介电常数材料的必然性,举例说明了低介电常数材料依然是当前集成电路工艺研究的重要课题,并展望了其发展前景。

正文部分综述了近年研究和开发的low k材料,如有机和无机低k材料,掺氟低k材料,多孔低k材料以及纳米低k材料等,评述了纳米尺度微电子器件对低k 薄膜材料的要求。

最后特别的介绍了一种可能制造出目前最小介电常数材料的技术: Air-Gap。

关键词:低介电常数;聚合物;掺氟材料;多孔材料;纳米材料 ;Air-Gap1.引言随着ULSI器件集成度的提高,纳米尺度器件内部金属连线的电阻和绝缘介质层的电容所形成的阻容造成的延时、串扰、功耗就成为限制器件性能的主要因素,微电子器件正经历着一场材料的重大变革:除用低电阻率金属(铜)替代铝,即用低介电常数材料取代普遍采用的SiO2(k:3.9~4.2)作介质层。

对其工艺集成的研究,已成为半导体ULSI工艺的重要分支。

这些低k材料必须需要具备以下性质:在电性能方面:要有低损耗和低泄漏电流;在机械性能方面:要有高附着力和高硬度;在化学性能方面:要有耐腐蚀和低吸水性;在热性能方面:要有高稳定性和低收缩性。

2.背景知识低介电常数材料大致可以分为无机和有机聚合物两类。

目前的研究认为,降低材料的介电常数主要有两种方法:其一是降低材料自身的极性,包括降低材料中电子极化率(electronic polarizability),离子极化率(ionic polarizability)以及分子极化率(dipolar polarizability)。

在分子极性降低的研究中,人们发现单位体积中的分子密度对降低材料的介电常数起着重要作用。

材料分子密度的降低有助于介电常数的降低。

这就是第二种降低介电常数的方法:增加材料中的空隙密度,从而降低材料的分子密度。

书山有路勤为径,学海无涯苦作舟

低介电常数低介质损耗PCB 基材

本文讨论了低介电常数、低介质损耗印制电路板基材的制法、性能及

应用。

1、引言

在近期的专利文献资料特许公开2012-56994 プリプレグ、金属张金属板、プリント配线板及び半导体装置一文中讨论了低介电常数、低介质损耗PCB 基材的制法及性能等;采用该方法制作的覆铜板样品的介电常数在1GHz 条件下为3.44~3.77,而介质损耗为0.0024~ 0.0033。

2、实验部分

2.1、试样制法

实验应用的主要原料有环氧树脂、双马来酰亚胺化合物、氰酸酯树脂以

及填料等,另外还应用到固化剂,它是在间- 位上有着胺基的苯氧化物,如其具体结构如在实验中具体应用的固化剂名称、结构、型号等结合举例将进一步

说明。

同时在实验过程中的溶剂、玻纤布、铜箔等原材料,制作印制电路板要

应用相关工序的化学物品以及制作半导体组件要应用相应的芯片等,在各举例

中将具体介绍。

为了阐明本发明的要点,给出了实施和比较两组举例。

2.1.1、实施例

实施例1(1) 树脂溶液的配制取7.0 质量(下同)份的双-(3-乙基-5-甲基-4- 马来酰亚胺苯基)甲烷(ケイアイ化成公司制造,型号为BM

(2) 制造半固化片

用上面得出的树脂溶液浸渍玻纤布(厚度为0.032mm,旭化成エレクトロニクス公司制造),在180℃烘干约5 分钟,得出树脂组成物为83%(质量百分。

低介电常数材料在超大规模集成电路工艺中的应用摘要:本文概述了低介电常数材料(Low k Materials)的特点、分类及其在集成电路工艺中的应用。

指出了应用低介电常数材料的必然性,最后举例说明了低介电常数材料依然是当前集成电路工艺研究的重要课题,并展望了其发展前景。

1引言半导体集成电路技术的飞速发展推动了新材料、新技术的不断进步,也使得半导体工业成长为工业界不可忽视的力量。

随着线宽的不断减小、晶体管密度的不断提升,越来越多的人把目光投向了低介电常数材料在超大规模集成电路中的应用。

当Intel,IBM,AMD,Motorola,Infineon,TSMC以及UMC等公司相继宣布将在0.13 mm及其以下的技术中使用低介电常数材料时,对低介电常数材料(Low k materials)及其工艺集成的研究,就逐渐成为半导体集成电路工艺的又一重要分支。

在集成电路工艺中,有着极好热稳定性、抗湿性的二氧化硅(SiO2)一直是金属互联线路间使用的主要绝缘材料。

而金属铝(Al)则是芯片中电路互联导线的主要材料。

然而,随着集成电路技术的进步,具有高速度、高器件密度、低功耗以及低成本的芯片越来越成为超大规模集成电路制造的主要产品。

此时,芯片中的导线密度不断增加,导线宽度和间距不断减小,互联中的电阻(R)和电容(C)所产生的寄生效应越来越明显。

图1是集成工艺技术与信号传输延迟的关系。

随着集成工艺技术的提高(线宽的减小),由互联引起的信号延迟也就成为制约芯片性能提升的重要因素。

当器件尺寸小于0.25mm后,克服阻容迟滞(RC Delay)而引起的信号传播延迟、线间干扰以及功率耗散等,就成为集成电路工艺技术发展不可回避的课题。

金属铜(Cu)的电阻率(~1.7μΩ·cm)比金属铝的电阻率(~2.7μΩ·cm)低约40%。

因而用铜线替代传统的铝线就成为集成电路工艺发展的必然方向。

如今,铜线工艺已经发展成为集成电路工艺的重要领域。

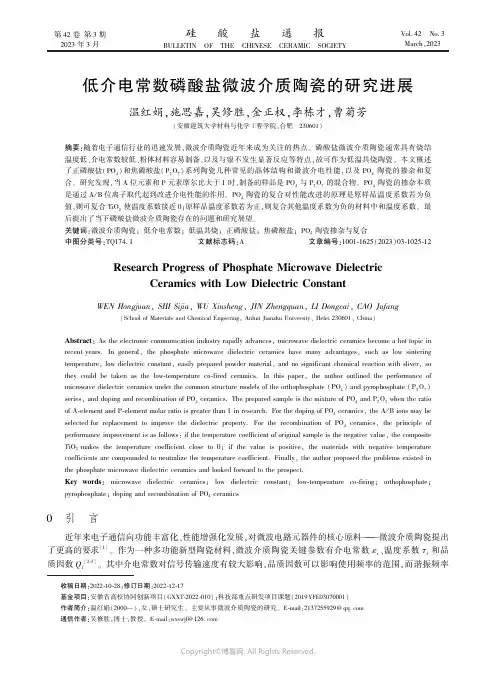

低介电常数微波介质陶瓷研究进展摘要:当前,电子元件正在向小型化、片式化、集成化方向发展,使得低温共烧陶瓷(Low-temperaturecofiredceramic,LTCC)技术越来越引起人们的关注。

目前,新一代基于LTCC技术的电子元件已经成为当前主流的电子元件,而该技术要求微波介质陶瓷能够与高电导率的银、铜等电极材料实现低温共烧。

然而,大多数性能优异的微波介质陶瓷的烧结温度都比较高,难以达到与金属电极低温共烧的要求。

为了降低其烧结温度,通常在基体中加入一定量低熔点的烧结助剂,但过多的烧结助剂往往会引起材料介电性能劣化。

因此,探索新型固有烧结温度低的微波介质陶瓷仍将是研究微波介质陶瓷材料领域的一个热点方向。

高频化是微波元器件发展的必然趋势,随着通讯设备工作频率向毫米波段拓展,信号延迟问题会变得更加突出,因此,对作为通讯设备关键材料的微波介质陶瓷性能参数提出了更高的要求。

与中、高介电常数材料相比,低介电常数材料能够降低基板与金属电极间的交互耦合损耗,缩短芯片间信号传播的延迟时间。

关键词:低介电常数;微波介质;陶瓷研究1钨酸盐体系目前对钨酸盐低介电常数微波介质陶瓷的研究主要集中在AWO4(A=Mg、Mn、Zn、Ca、Sr、Ba、Cd)体系上,其晶体结构与A2+的半径有关。

当A2+的半径较大时(如Ca、Ba、Sr),易形成四方相白钨矿结构,空间点群为I41/a;当A2+的半径较小时(如Mg、Zn、Mn、Cd),则会形成单斜相黑钨矿结构,空间点群为P2/c。

1988年,Nishigaki等[8]研究WO3对BaO-4TiO2陶瓷微波介电性能影响时,发现掺杂少量WO3显著提高了陶瓷的品质因数,这是因为形成了BaWO4第二相。

随后,他们以Ba-CO3和WO3粉末为原料于1200℃制备出BaWO4单相陶瓷,并首次报道其微波介电性能:εr=8.2,Q×f=18000GHz,τf=-33×10-6/℃。

低K材料在半导体集成电路中的应用与展望在超大规模集成电路工艺中,有着极好热稳定性、抗湿性的二氧化硅一直是金属互连线路间使用的主要绝缘材料,金属铝则是芯片中电路互连导线的主要材料。

然而,相对于元件的微型化及集成度的增加,电路中导体连线数目不断的增多,使得导体连线架构中的电阻(R)及电容(C)所产生的寄生效应,造成了严重的传输延迟(RC delay),在130纳米及更先进的技术中成为电路中讯号传输速度受限的主要因素。

因此,在降低导线电阻方面,由于金属铜具有高熔点、低电阻系数及高抗电子迁移的能力,已被广泛地应用于连线架构中来取代金属铝作为导体连线的材料。

另一方面,在降低寄生电容方面,由于工艺上和导线电阻的限制,使得我们无法考虑籍有几何上的改变来降低寄生电容值。

因此,具有低介电常数(low k)的材料便被不断地发展。

在将低介电常数材料应用于集成电路的整合工艺时,对于低介电常数材料特性的要求,除了要具备有低的介电常数之外,还需具有良好的物理,材料及电特性。

通常有两种主要的方法被使用来降低材料的介电常数,第一种方法是设法降低材料本身的极性(polarization),包括降低材料中的电子极化、离子极化以及分子极化。

另外一种则是在介电材料内制造空隙(Porosity) 。

工艺上,低介电常数材料的制造分为化学气相沉积法与旋涂式两大主流,即CVD与SOD法。

但SOD方法在45纳米工艺技术之前不会被业界用于批量生产。

业界已成功研发出沉积多种低介电常数薄膜的技术能力,包括氟硅玻璃(FSG)、碳掺杂的氧化硅(如:Black Diamond)、以及氮掺杂的碳化硅(如:BLOK )。

Black Diamond膜 是一种以氧化硅为基础的化学气相沉积薄膜,有效介电常数小于3.0。

而BLOK则是一种低介电常数的铜金属阻挡层与蚀刻终止层,在双镶嵌工艺应用中可作为氮化硅低介电常数的替代材料。

在与氟硅玻璃及Black Diamond薄膜完成双镶嵌工艺整合后,相较于氧化硅/氮化硅材料而言,电容值可降低达25%至35%。

05018功 燧 讨 科 2021年第5期(52)卷文章编号:1001-9731 (2021 )05-05018-07低介电常数改性聚酰亚胺材料的研究进展*黄兴文朋小康刘荣涛廖松义12,刘屹东12,闵永刚12(1.广东工业大学材料与能源学院,广州510006; 2.东莞华南设计创新院,广东东莞523808)摘 要: 聚酰亚胺(PI )广泛应用于电子集成电路的绝缘材料领域。

随着电子通信行业的不断更新换代,信号传输频率逐渐往高频发展(例如5G 通讯),为了满足信号传输速度快、介电损耗低的要求,需要不断地降低印刷线路板(PCB )绝缘材料的介电常数。

常规聚酰亚胺介电常数偏高,不适合直接用于PCB 的绝缘材料,为满足未来5G 高频通信要求,必须对其进行改性,因此本文综述了低介电常数聚酰亚胺改性的研究进展,并对其进行了展望。

关键词:改性聚酰亚胺;高频通信;低介电常数;低介电损耗;5G 通讯中图分类号:TM215.3 文献标识码:A DOI :10.3969/j.issn.1001-9731.2021.05.0040引言聚酰亚胺是指一类含有酰亚胺环的聚合物⑴,由 二酐和二胺经过逐步聚合反应、亚胺化而成,其分子通 式如图1所示。

美国杜邦公司首次商业化聚酰亚胺,商品名为Kpton,到现在聚酰亚胺已经衍生了很多的产品,如联苯型聚酰亚胺⑵和硫醚型聚酰亚胺[]等等。

聚酰亚胺由于具有耐高温、耐电晕、耐辐射性、高强度、高绝缘、低吸湿率、低介电常数和低介电损耗等优异的 综合性能,作为特种高分子材料被广泛应用于印刷线路板的绝缘领域。

图1聚酰亚胺分子通式Fig 1 General polyimide molecular formula对于高频天线用的印刷线路板,其信号传输速度 与材料的介电常数成反比关系,可用以下公式来描述⑷:“ C 0其中V 为传输速率,C 。

为真空光速为材料介电常 数,从式可以看出相对介电常数越小,信号传输速度越快;而另一方面介电损耗则与介电常数成正比关系[5],介电常数越大,损耗也越大。

高频低介电材料

1.无机陶瓷材料:无机陶瓷材料具有优异的高频性能,例如氧化铝、氮化硼、氮化铝等。

它们具有低介电常数、低损耗和良好的热稳定性,适用于高频电子器件和射频通信系统。

2.聚合物材料:聚合物材料是一种结构松散、分子链可自由转动的有机物质,具有较低的介电常数和损耗。

例如聚四氟乙烯(PTFE)、聚酰亚胺(PI)、聚苯硫醚(PPS)等,它们被广泛应用于高频电路板、天线和射频连接器等器件中。

3.氧化物和氮化物复合材料:氧化物和氮化物复合材料在高频电子器件中也具有广泛的应用。

例如氧化铝和氮化硅的复合材料、氧化铝和氮化铝的复合材料等。

这些复合材料综合了不同材料的优点,具有更低的介电常数和更低的损耗。

4.非晶合金材料:非晶合金材料是一种具有无序结构的金属合金材料,它具有较低的介电常数和高的导电性能。

非晶合金材料可以在高频电子器件中用作导体和屏蔽材料,减少信号的干扰和电磁波的损耗。

不同条件下低介电常数材料机械性研究【摘要】目前最新的组件结构均采用低介电常数材料及铜导线技术来降低多层金属联机中时间延迟效应。

低介电常数材料多为组织松散,机械强度不理想,故低介电常数材料是多层金属导线,外力将易于跨越材料之降伏强度,势必导致断线之危机,进而破坏组件的运作。

针对低介电常数材料的机械性质,首先探讨低介电常数材料本身的机械性质;其次探讨低介电常数材料和相邻材料的附着性质。

【关键词】电常数材料;铜导线;多层金属导线1.简介在先进的集成电路多层金属导线设计准则中,0.18世代之最小金属间距已小于0.25微米;为了降低集成电路组件操作时的时间延迟及功率消耗,金属间的隔绝材料使用低介电常数材料乃是必要的。

另一方面,芯片封装技术亦伴随着集成电路多层金属导线尺寸的快速缩小,而面临相同的困境。

由于低介电常数材料使用的必然性及可预期的广大市场需求,过去几年来,全世界半导体材料供货商及研发中心均致力于发展质量合乎新世代集成电路要求的低介电常数材料。

大约有100种左右不同的低介电常数材料,以化学气相沉积、旋涂式沉积或其他方式制备而成,然而经由电性质、热性质及机械性质鉴定后,仅有少数低介电常数材料符合基本物理及化学性质要求;对于制程整合的考虑更进一步淘汰了一些物性及化性稳定的低介电常数材料。

所以目前建议可能使用的低介电常数材料,大致上仅剩(I)有机硅酸盐类和(II)有机高分子相关材料两大类。

尽管如此,这两大类低介电常数材料并非完美,基本结构的改进仍有许多空间需努力。

针对低介电常数材料的机械性质。

低介电常数材料的机械性质包含两个主要部分;第一部分为材料本身的机械性质,硬度及薄膜应力为两个重要指标。

一般而言,为了达到低介电性质,低介电常数材料多为组织松散的多孔性材质,弹性模数只有传统二氧化硅(72 GPa)的1/10到1/5倍,热膨胀系数则比传统二氧化硅大4到10倍;低介电常数薄膜应力通常为相对值不大的张应力,此特性亦有别于传统二氧化硅。

第42卷第3期2023年3月硅㊀酸㊀盐㊀通㊀报BULLETIN OF THE CHINESE CERAMIC SOCIETY Vol.42㊀No.3March,2023低介电常数磷酸盐微波介质陶瓷的研究进展温红娟,施思嘉,吴修胜,金正权,李栋才,曹菊芳(安徽建筑大学材料与化学工程学院,合肥㊀230601)摘要:随着电子通信行业的迅速发展,微波介质陶瓷近年来成为关注的热点㊂磷酸盐微波介质陶瓷通常具有烧结温度低㊁介电常数较低㊁粉体材料容易制备,以及与银不发生显著反应等特点,故可作为低温共烧陶瓷㊂本文概述了正磷酸盐(PO 4)和焦磷酸盐(P 2O 7)系列陶瓷几种常见的晶体结构和微波介电性能,以及PO 4陶瓷的掺杂和复合㊂研究发现,当A 位元素和P 元素摩尔比大于1时,制备的样品是PO 4与P 2O 7的混合物㊂PO 4陶瓷的掺杂本质是通过A /B 位离子取代起到改进介电性能的作用㊂PO 4陶瓷的复合对性能改进的原理是原样品温度系数若为负值,则可复合TiO 2使温度系数接近0;原样品温度系数若为正,则复合其他温度系数为负的材料中和温度系数㊂最后提出了当下磷酸盐微波介质陶瓷存在的问题和研究展望㊂关键词:微波介质陶瓷;低介电常数;低温共烧;正磷酸盐;焦磷酸盐;PO 4陶瓷掺杂与复合中图分类号:TQ174.1㊀㊀文献标志码:A ㊀㊀文章编号:1001-1625(2023)03-1025-12Research Progress of Phosphate Microwave Dielectric Ceramics with Low Dielectric ConstantWEN Hongjuan ,SHI Sijia ,WU Xiusheng ,JIN Zhengquan ,LI Dongcai ,CAO Jufang (School of Materials and Chemical Engeering,Anhui Jianzhu University,Hefei 230601,China)Abstract :As the electronic communication industry rapidly advances,microwave dielectric ceramics become a hot topic in recent years.In general,the phosphate microwave dielectric ceramics have many advantages,such as low sintering temperature,low dielectric constant,easily prepared powder material,and no significant chemical reaction with sliver,so they could be taken as the low-temperature co-fired ceramics.In this paper,the author outlined the performance of microwave dielectric ceramics under the common structure models of the orthophosphate (PO 4)and pyrophosphate (P 2O 7)series,and doping and recombination of PO 4ceramics.The prepared sample is the mixture of PO 4and P 2O 7when the ratio of A-element and P-element molar ratio is greater than 1in research.For the doping of PO 4ceramics,the A /B ions may be selected for replacement to improve the dielectric property.For the recombination of PO 4ceramics,the principle of performance improvement is as follows:if the temperature coefficient of original sample is the negative value,the composite TiO 2makes the temperature coefficient close to 0;if the value is positive,the materials with negative temperature coefficients are compounded to neutralize the temperature coefficient.Finally,the author proposed the problems existed in the phosphate microwave dielectric ceramics and looked forward to the prospect.Key words :microwave dielectric ceramics;low dielectric constant;low-temperature co-firing;orthophosphate;pyrophosphate;doping and recombination of PO 4ceramics 收稿日期:2022-10-28;修订日期:2022-12-17基金项目:安徽省高校协同创新项目(GXXT-2022-010);科技部重点研发项目课题(2019YFE03070001)作者简介:温红娟(2000 ),女,硕士研究生㊂主要从事微波介质陶瓷的研究㊂E-mail:2137255929@通信作者:吴修胜,博士,教授㊂E-mail:wxswjf@ 0㊀引㊀言近年来电子通信向功能丰富化㊁性能增强化发展,对微波电路元器件的核心原料 微波介质陶瓷提出了更高的要求[1]㊂作为一种多功能新型陶瓷材料,微波介质陶瓷关键参数有介电常数εr ㊁温度系数τf 和品质因数Q f [2-3]㊂其中介电常数对信号传输速度有较大影响,品质因数可以影响使用频率的范围,而谐振频率1026㊀陶㊀瓷硅酸盐通报㊀㊀㊀㊀㊀㊀第42卷的温度系数可以影响器件的温度稳定性㊂微波介质陶瓷作为新兴材料中的一种,以其不同的介电常数㊁品质因数和温度系数在通信和雷达行业广泛运用㊂微波通信技术研究在近些年朝着毫米波方向发展,对材料在毫米波段下的传递速度和频率接收范围以及温度稳定性提出了要求㊂一般来说介电常数越低,传递信号时传播速度就会越高;品质因数越高,材料使用时的频率范围就越广;温度系数越接近0,材料的温度稳定性就越好㊂微波介质陶瓷根据介电常数大小可分为高介电常数微波介质陶瓷(εr >30)㊁中介电常数微波介质陶瓷(15<εr ɤ30)和低介电常数微波介质陶瓷(0<εr ɤ15)㊂其中低介电常数微波介质陶瓷由于具有良好的信号传播速度,成为重点研究对象㊂常见的低介电常数微波介质陶瓷包括氧化铝系㊁AAl 2O 4系(A =Zn㊁Mg)㊁硅酸盐系㊁钼酸盐㊁钒酸盐和磷酸盐等㊂磷酸盐微波介质陶瓷有许多优点,如介电常数低㊁品质因数高和烧结温度低等,因此近年来成为新的研究热点[4-6]㊂本文主要介绍了低介电常数磷酸盐微波介质陶瓷㊂首先将磷酸盐陶瓷分为正磷酸盐陶瓷和焦磷酸盐陶瓷,分别列举出这两种磷酸盐下常见的系列陶瓷并举例展现磷酸盐陶瓷性能的优越性,最后介绍掺杂与复合两种方式对磷酸盐陶瓷性能的改进并举例说明㊂1㊀PO 4系列1.1㊀LiMPO 4系列图1㊀LiMgPO 4陶瓷晶体结构示意图[11]Fig.1㊀Crystal structure diagram of LiMgPO 4ceramics [11]LiMPO 4系陶瓷分两种情况,第一种在结构上LiMPO 4(M =Mg㊁Ni㊁Mn)系陶瓷属于正交晶系[7]㊂图1是LiMgPO 4的晶体结构示意图,[LiO 6]八面体单元与八面体Mg 和四面体P 相互连接㊂LiMPO 4的介电性能不仅与烧结温度有关,也与M 离子种类有关㊂为了研究LiMgPO 4体系,Thomas 等[8]在950ħ下对其进行3h 的烧结,发现介电常数为6.6,品质因数为79100GHz,温度系数为55ppm /ħ(1ppm =10-6)㊂同时Xiao 等[9-10]研究发现LiNiPO 4体系在825ħ烧结条件下理论密度超过95%,介电常数为5.18,品质因数为24076GHz㊂由于其具有介电常数和烧结温度较低的特点,LiMPO 4(M =Mg㊁Ni㊁Mn)系陶瓷还可以与Ag 共烧,因此LiMPO 4系陶瓷在低温共烧陶瓷(low-temperature co-fired ceramics,LTCC)技术中有较大的潜力㊂相较于LiMPO 4的橄榄石结构,第二种结构中每四个O 原子都可与阳离子合成四面体,[ZnO 4]和[LiO 4]四面体可连接构成磷酸锂锌(LiZnPO 4,LZP)结构㊂为了研究LiZnPO 4陶瓷性能随温度的变化情况,Shi 等[12]设置了不同的温度梯度,在不同温度下烧结的LiZnPO 4的性能见表1㊂可知介电常数和品质因数随烧结温度提高而增大,密度也达到顶峰(96.01%),当烧结温度升高至825ħ以上时密度降低,品质因数和介电常数减小,此结果表明性能和烧结致密程度呈正相关㊂表1㊀LiZnPO 4微波介质陶瓷的介电常数㊁品质因数与密度[12]Table 1㊀Dielectric constant ,quality factor and density of LiZnPO 4microwave dielectric ceramics [12]Temperature /ħεr εrc Q f /GHz Density /(g㊃cm -3)Relative density /%725 5.46 5.9925311 3.30792.33750 5.47 5.9528883 3.30893.01775 5.48 5.8939366 3.31193.97800 5.50 5.8643908 3.32194.66825 5.50 5.7747207 3.32896.01850 5.47 5.7745281 3.31195.39㊀㊀注:εr 是介电常数,εrc 是介电损耗,Q f 是品质因数㊂第3期温红娟等:低介电常数磷酸盐微波介质陶瓷的研究进展1027㊀1.2㊀A 3(PO 4)2(A =Mg ㊁Cu )正磷酸盐陶瓷具有稳定的晶体结构,作为优良的功能材料在许多领域被广泛应用㊂Mg 3(PO 4)2具有单斜晶系结构,属于空间群P 121/n 1,多采用固相合成法,在1000ħ下介电常数最低可达到5.42㊂Zhang 等[13]将Mg 3(PO 4)2和30%(质量分数)Ag 的复合材料在950ħ下烧结,通过扫描电镜分别观察Mg 3(PO 4)2和Ag 两组相,发现没有任何杂相,因此得出Mg 3(PO 4)2和Ag 之间没发生显著反应的结论㊂Cu 3(PO 4)2属于三斜晶系,由六面体[CuO 5]和四面体[PO 4]组成,[CuO 5]和[PO 4]通过角共享连接,Cu 2+以两种类型排列,一种形成六面体,另一种位于多面体间隙中㊂Feng 等[14]通过扫描电镜测得Cu 3(PO 4)2陶瓷的密度在900ħ下达到最大,介电常数和品质因数具有明显的密度依赖性,介电常数为7.33,品质因数为86756GHz,温度系数为-30ppm /ħ,P O 化学键在Cu 3(PO 4)2陶瓷的微波介电性能中起到主要作用㊂1.3㊀BPO 4BPO 4微波介质陶瓷因其超低的介电特性受到广泛关注,在已知显微结构会对陶瓷性能产生影响的基础上,Wang 等[15]先后研究了固态烧结(solid state sintering,SSS)和放电等离子烧结(spark plasma sintering,SPS)两种烧结方法制备的BPO 4微波介质陶瓷㊂BPO 4是具有方石英结构的超低介电陶瓷,BPO 4具有类似SiO 2衍生物结构,顶点共享四面体网络的开放晶体结构使填充分数降低,分子摩尔体积增加,使介电常数进一步降低㊂研究发现固相烧结会降低BPO 4的性能,由于样品是多孔结构,在高温下晶粒收缩严重并发生升华,温度的升高导致孔隙变大,产生巨大损失,升温到1200ħ时,BPO 4最高相对密度仅为74.6%㊂用放电等离子烧结方法制备的BPO 4陶瓷在烧结期间产生的脉冲电流对等离子体施加压力,产生的影响会改变烧结时间和降低烧结温度,在1000ħ下制备的BPO 4陶瓷的相对密度为92.7%,但B 2O 3会降低BPO 4陶瓷熔点,样品在较高温度下可能发生熔融,使样品烧结失败㊂BPO 4在1200ħ固态烧结下介电常数为3.38,品质因数为18200GHz,温度系数为-42.8ppm /ħ㊂采用放电等离子烧结方式1000ħ烧结,介电常数为4.20,品质因数为4000GHz,温度系数为-20.7ppm /ħ㊂使用改进的谐振腔方法评估介电常数和品质因数在4.6~14.6GHz 的频率依赖性,结果如图2所示,可知介电常数在4.6~14.6GHz 较为稳定㊂主要微波频率下的离子和电子位移极化通常决定了介电常数的大小,而这两者对频率几乎没有依赖㊂低温烧结和快速烧结抑制了晶粒的生长,导致SPS 样品的晶粒尺寸明显小于1200ħ烧结的SSS 样品的晶粒尺寸,如图3所示,进而得出放电等离子烧结方式下品质因数远小于固态烧结方式下品质因数的结论㊂图2㊀固相烧结和放电等离子烧结样品在不同频率下εr 和Q f 变化趋势[15]Fig.2㊀εr and Q f change trend of solid state sintering and spark plasma sintering samples at different frequencies [15]随着频率从4.6GHz 增加到14.6GHz,两种烧结方式下样品的品质因数都增加了近7倍㊂在微波介质陶瓷中,非本征介电损耗是非常正常的,这与微结构缺陷有关㊂外部介电损耗通常与频率不成正比,导致品质因数与频率相关[16-17]㊂因此,外部因素的影响可以通过品质因数的频率依赖程度估计㊂与典型的微波介1028㊀陶㊀瓷硅酸盐通报㊀㊀㊀㊀㊀㊀第42卷质陶瓷相比,目前BPO 4陶瓷的品质因数表现出更强的频率依赖性,如图2所示㊂结构上若能进一步改善,品质因数的频率依赖性有望得到抑制,BPO 4陶瓷的品质因数将有巨大的改善空间㊂图3㊀在1100㊁1200ħ下固态烧结的BPO 4陶瓷(SSS 样品)和1000ħ下放电等离子烧结的BPO 4陶瓷(SPS 样品)断裂表面的SEM 照片[15]Fig.3㊀SEM images of fractured surfaces of BPO 4ceramics (SSS samples)solid state sintered at 1100,1200ħ,and BPO 4ceramics (SPS sample)spark plasma sintered at 1000ħ[15]材料研究需了解材料的组成㊁合成㊁性能间的相互作用关系,对比两种烧结样品可知固相烧结样品收缩明显㊂在多价金属磷酸盐稳定性的研究过程中发现其在高温下会发生解离,氧化磷转化为蒸汽㊂故烧结过程中样品会升华,导致孔隙变大,孔隙数减少,进而相对密度降低,性能变差,若出现熔融,将导致样品烧结失败㊂采用放电等离子烧结方式制备的陶瓷样品因其烧结特性使制备时间缩短,从而使晶粒生长受到抑制,进而使样品内部晶粒均匀性能优异㊂对这一类磷酸盐陶瓷性能的总结见表2,可得到一种材料通过不同烧结方式会表现出不同性能的结论㊂表2㊀正磷酸盐微波介质陶瓷分类Table 2㊀Classification of orthophosphate microwave dielectric ceramicsRaw material Temperature /ħSintering style εr Q f /GHz τf /(ppm㊃ħ-1)Reference LiMgPO 4825SSS 5.1824076[9]BPO 41200SSS 3.3818200-42.8[15]BPO 41000SPS 4.204000∗(5.9)~4000∗(6.9)-20.7[15]1.4㊀AB 2PO 6(AB 2(PO 4)O 2)对于AB 2PO 6(AB 2(PO 4)O 2)体系,A 为+3价阳离子,B 为+2价阳离子,目前主要研究BiB 2PO 6系列㊂结构上BiZn 2PO 6的三维结构属于正交晶系,Bi 原子以共价键的形式与四个O 原子相连,形成一个[BiO 4]方形金字塔,[PO 4]四面体相互独立㊂Zhang 等[18]发现在725ħ下烧结的BiZn 2PO 6陶瓷具有最好的性能,介电常数为13.269,品质因数为18030GHz,温度系数为-18.9ppm /ħ,超过725ħ时品质因数降低,BiZn 2PO 6的品质因数与晶体内部结构有关,当温度升高时样品体积收缩导致密度增加,晶体内部空隙减小使样品测试的性能增加,当温度超过临界点时晶粒形貌会发生不规则变化,导致陶瓷的性能降低,在合适的烧结温度范围内样品具有良好的致密性和完整的晶粒形貌,如图4所示,性能不会降低,因此许多样品在测量时性能会表现出随着温度升高先提高后降低的趋势㊂由此可知温度所导致的结构变化也会改变陶瓷的性能㊂晶格能与晶体内部键能的大小也对品质因数有重要影响㊂BiZn 2PO 6陶瓷的温度系数对烧结温度不敏感㊂由此可知在低温条件下获得的BiZn 2PO 6陶瓷具有优异的致密性㊂BiZn 2PO 6陶瓷的键类型㊁键长㊁晶格能如表3所示㊂通过表3可知P O 键的离子性和晶格能都要大于其他键,表明P O 键对BiZn 2PO 6化合物的介电常数更为重要㊂第3期温红娟等:低介电常数磷酸盐微波介质陶瓷的研究进展1029㊀图4㊀不同温度烧结的BiZn 2PO 6陶瓷的SEM 照片[18]Fig.4㊀SEM images of BiZn 2PO 6ceramics sintered at different temperatures [18]表3㊀BiZn 2PO 6陶瓷的键类型㊁键长㊁晶格能[18]Table 3㊀Bond type ,bond length and lattice energy of BiZn 2PO 6ceramics [18]AtomBond type Bond length /ÅLattice energy /(kJ㊃mol -1)Average lattice energy /(kJ㊃mol -1)Bi Bi O(1)1 2.340ˑ22028Bi O(1)2 2.301ˑ22055Bi O(3) 3.063ˑ21645Bi O(4) 2.940ˑ117221862.5Zn(1)Zn(1) O(1) 1.970ˑ21537Zn(1) O(2) 2.084ˑ21467Zn(1) O(4) 2.050ˑ114321478.7Zn(2)Zn(2) O(1) 1.970ˑ21537Zn(2) O(2) 2.016ˑ21505Zn(2) O(3) 2.116ˑ114281490.0P P O(2) 1.557ˑ25189P O(3) 1.443ˑ16296P O(4) 1.430ˑ168346106.3Hao 等[19]研究了BiCu 2PO 6陶瓷,BiCu 2PO 6陶瓷的密度为6.481g /cm 3,结构上与BiZn 2PO 6同属于正交晶系,研究发现BiCu 2O 6的致密度随温度提升表现出上涨趋势,并在860ħ时达到最大值98.2%,介电常数为16.04,品质因数为39110GHz,温度系数为-59ppm /ħ㊂由于晶粒劣化,介电常数通常在熔化前略有降低,随温度升高呈先增大后减小的趋势㊂可见AB 2PO 6系列的磷酸盐介电常数偏高㊂通过对BiZn 2PO 6研究发现温度系数受内部因素和外部因素影响,内部因素主要为晶格振动,表现为不同元素间的化学键晶格能,晶格能越高,品质因数越大㊂如表3所示,P O 键的平均晶格能远高于其他类型的化学键,因此P O 键贡献了BiZn 2PO 6和BiCu 2PO 6陶瓷的大部分晶格能㊂可知品质因数会受到化学键影响,对BiCu 2PO 6研究发现进行离子取代试验中离子半径越小越难被取代㊂1030㊀陶㊀瓷硅酸盐通报㊀㊀㊀㊀㊀㊀第42卷2㊀P2O7系列2.1㊀A2P2O7(ABP2O7)磷酸盐陶瓷除了正磷酸盐(PO4)系列还有焦磷酸盐(P2O7)系列,常见的P2O7系低介电常数微波介质陶瓷有A2P2O7(A=Ca㊁Ba㊁Co)与ABP2O7(A=Ca㊁Sr㊁Ba;B=Zn㊁Cu),当下A2P2O7系列是研究员的主要研究对象㊂Chen等[20]研究发现结构上Co2P2O7中的磷与氧原子呈四面体配位,构成[P2O7]多面体,双四面体[P2O7]包含P O P和O P O自由基,对电介质性能产生影响㊂在1130㊁1150㊁1170ħ制备的陶瓷对应品质因数为29120㊁32820㊁33320GHz,研究发现这是由于不同温度下晶粒尺寸不同导致密度变化,最终引起品质因数的变化㊂通过设置不同温度梯度得出最佳制备温度为1160ħ,此时性能具体为:介电常数为6.76,品质因数为36400GHz,温度系数为-23.9ppm/ħ㊂纯相BaZnP2O7属于P-1三斜晶系结晶,其中Ba和Zn原子分别与9个和5个O原子配位,形成[BaO9]和[ZnO5]多面体㊂P原子显示出两个不同的晶体学位点,即P1和P2㊂P原子与氧四面体配位,形成完整的[PO4]四面体,P O键长度在1.492~1.607㊂[P1O4]和[P2O4]四面体通过共角O原子构成双四面体[P2O7]㊂Chen等[21]在870ħ下固相烧结4h得到介电常数为8.23㊁品质因数为56170GHz㊁温度系数为-28.7ppm/ħ的BaZnP2O7陶瓷㊂为了研究Sr的含量变化对Sr2P2O7陶瓷微波性能的影响,Guo等[22]最初在固相法制备Sr2P2O7时将原料中Sr/P(摩尔比)设置为1,此时粉末呈纯α-Sr2P2O7相㊂随着比例改变,正磷酸盐Sr3(PO4)2相的含量也同Sr/P增加而增加㊂当Sr/P小于0.060时,样品为(1-x)Sr2P2O7-x Sr3(PO4)2㊂当Sr/P为0.060时,在1125ħ烧结温度下获得良好的介电性能:介电常数为7.9,品质因数为17200GHz(在9.9GHz时)和温度系数为2.09ppm/ħ㊂Sr3(PO4)2的理论密度(4.530g/cm3)高于Sr2P2O7(3.675g/cm3),当Sr3(PO4)2相含量增加时,样品体积密度增长,导致性能改变㊂正磷酸盐体系和焦磷酸盐体系的低介电常数主要是由于P O键的共价性质,α-Sr3(PO4)2相的共价键数比焦磷酸盐相α-Sr2P2O7的共价键数少,故具有更大的介电常数,当Sr3(PO4)2含量增加时,陶瓷介电常数增加,温度系数增加㊂故当原料中Sr/P大于1时,可得到Sr2P2O7和Sr3(PO4)2混合相㊂2.2㊀AP2O7为了研究锰掺杂对TiP2O7微观结构和性能的影响㊂Wang等[23-24]对Mn掺入TiP2O7的浓度进行了实验,研究发现掺杂一定量的Mn可以减少(TiO)2P2O7杂质相出现,但会导致Mn0.5Ti2(PO4)3第二相型的出现,其数量随着Mn掺杂浓度的增加而增加㊂掺杂样品中这种含Mn2+的杂质相的出现可以解释为Mn的多价态的存在,Mn对Ti的取代受扩散过程控制,仅发生在Mn0.5Ti2(PO4)3中及其相邻的基体相,它们的组成可以确定为Mn0.5Ti2-x Mn y(PO4)3和Ti1-x Mn x P2O7㊂Mn在基体晶粒内的分布是不均匀的,其浓度随Mn0.5Ti2-x Mn y(PO4)3和TiP2O7基体相与晶界距离的增加而降低,孔隙率随着Mn掺杂量的增加而降低,介电常数和品质因数随着少量Mn掺杂显著提高㊂在1200ħ的空气中烧结2h后介电常数为14,品质因数为87304GHz,温度系数为19ppm/ħ,与空气中烧结相比,在氧气下烧结的Mn0.5Ti2-x Mn y(PO4)3杂质相明显减少,但对介电性能影响不大㊂表4㊀焦磷酸盐微波介质陶瓷的介电性能Table4㊀Dielectric properties of pyrophosphate microwave dielectric ceramics Raw material Temperature/ħεr Q f/GHzτf/(ppm㊃ħ-1)RefereneCo2P2O71160 6.7636400-23.9[20]BaZnP2O78708.2356170-28.7[21]Sr2P2O711257.917200 2.09[22](TiO)2P2O71200148730419[23]常见焦磷酸盐微波介质陶瓷的介电性能见表4,对比正磷酸盐和焦磷酸盐性能不难发现,焦磷酸盐的烧结温度与介电常数相对正磷酸盐要高,但焦磷酸盐在品质因数与温度系数上优于正磷酸盐㊂实际应用中可第3期温红娟等:低介电常数磷酸盐微波介质陶瓷的研究进展1031㊀根据不同需求选择对应的陶瓷㊂3㊀PO 4陶瓷的掺杂目前单相磷酸盐陶瓷的介电常数通常低于15,品质因数大于20000GHz,温度系数范围在-100~+100ppm /ħ㊂A /B 位离子掺杂使品质因数提高,介电常数降低㊂因此近年来研究者对离子置换进行了大量研究,使磷酸盐陶瓷的性能进一步提高㊂Peng 等[25]研究了Ni 2+㊁Co 2+㊁Mn 2+对LiZnPO 4陶瓷进行取代后样品的介电性能㊂在LiZnPO 4中掺入MnO 2探究性能变化,得到LiZnPO 4(LZP)和磷酸锂锰(LiMnPO 4,LMP)陶瓷的结构,如图5所示㊂图5㊀(a)LZP 陶瓷原始模型;(b),(c)Mn 2+取代[ZnO 4]四面体前后示意图;(d)LMP 陶瓷原始模型;(e),(f)Zn 2+取代[MnO 8]八面体前后示意图[25]Fig.5㊀(a)Primitive cell of LZP ceramics;(b),(c)schematic diagram of [ZnO 4]tetrahedron before and after Mn 2+substitution;(d)primitive cell of LMP ceramics;(e),(f)schematic diagram of [MnO 8]octahedron before and after Zn 2+substitution [25]通过掺杂适量Mn 2+,复合陶瓷的介电常数小幅度增加,品质因数增大,温度系数变化较小㊂通过加入Co 2+,陶瓷各项性能略微增加㊂掺杂适量的Ni 2+后复合陶瓷介电常数小幅度上升,品质因数增大,温度系数略微增大㊂同理适量的Mn 2+㊁Co 2+㊁Ni 2+添加可以改善LZP 陶瓷的致密化,降低烧结温度[26-28]㊂在LZP 陶瓷中加入LMP 陶瓷是提高烧结致密化水平和介电性能的有效方法,具体细节见表5㊂表5㊀B 位掺杂LiZnPO 4陶瓷的微波性能Table 5㊀Microwave properties of B-site doped LiZnPO 4ceramicsRaw material Temperature /ħεr Q f /GHz τf /(ppm㊃ħ-1)Reference LiZnPO 4850 5.328496-80.4[25]Li(Zn 0.96Mn 0.04)PO 4825 5.5875031-80.3[26]Li(Zn 0.93Co 0.07)PO 4850 5.4535687-76.8[27]Li(Zn 0.98Ni 0.02)PO 4825 5.5763951-79.5[28]随着Zn 2+逐渐被Mn 2+取代,[ZnO 4]四面体和[MnO 8]八面体的微观结构特征包括配位数㊁电子密度㊁键长和键布居数发生了变化㊂对离子取代前后键长和键布居数进行分析,发现属于[ZnO 4]四面体的阳离子几乎所有的键长都增加了,其所有键布居数都减少了㊂对于[MnO 8]八面体的变化,一半的键长值随着键布居数的减少而增加,另一半则随着键布居数的减少而减小㊂键布居数的减少对应于阳离子和氧离子之间共价性的减弱,而键布居数的增加对应于共价性的增强㊂Shi 等[12]详细研究了LZP 陶瓷的结构与性能之间的关1032㊀陶㊀瓷硅酸盐通报㊀㊀㊀㊀㊀㊀第42卷系,发现当拉曼位移(振动频率)随着烧结温度的升高而增强时,P O键的能量增加,键长相应减少,键长越短,键能越大㊂而拉曼位移的增加意味着P O键长度减少㊂较长的键长使极化更容易,进而导致介电常数升高㊂故得出随烧结温度提高,P O键长增加,介电常数也增大,而介电常数与拉曼位移呈负相关㊂品质因数与半峰全宽值成反比,但与填充率成正比㊂Dong等[27]在制备LiMgPO4中用Ni2+取代Mg2+,生成Li(Mg1-x Ni x)PO4㊂LiMgPO4具有正交橄榄石型结构,由于掺入较小的Ni2+代替Mg2+,Li(Mg1-x Ni x)PO4陶瓷的晶胞体积逐渐变小㊂在进行烧结试验中发现Ni2+取代Mg2+可降低陶瓷烧结温度㊂由于锂离子高温易挥发,故向LiMgPO4里加过量锂元素补充,950ħ下陶瓷的介电性能为:介电常数为6.6,品质因数为79100GHz,温度系数为-55ppm/ħ㊂掺杂Ni2+后, LiMg0.95Ni0.05PO4陶瓷在875ħ下烧结2h,可达到97.1%的最大相对密度,此时显示εr=6.91,Q f=98600GHz,τf=-55.3ppm/ħ㊂在制备LiMgPO4中用Co2+取代Mg2+,LiMg0.95Co0.05PO4在875ħ下烧结的样品密度最高,品质因数的变化趋势与相对密度的变化趋势相似㊂在875ħ下烧结后,LiMg0.95Co0.05PO4的最大品质因数为111200GHz,介电常数为6.97,温度系数为53.8ppm/ħ,根据Li(Mg1-x Co x)PO4陶瓷的致密化和介电性能的结果,得出Co2+取代Mg2+可以降低烧结温度并提高品质因数的结论[26-32]㊂在875ħ下LiMg0.95Co0.05PO4的最大品质因数为111200GHz,并且复合陶瓷通常不会和银制的电极材料发生反应㊂故LiMgPO4是LTCC候选材料㊂Zhang等[11]采用固相反应法合成了具有正交橄榄石结构的新型低烧成微波介质陶瓷LiMg1-x A x PO4(A=Mn㊁Ca,0.02<x<0.08)㊂理论上,Mn2+半径小于Mg2+,单位体积随Mn2+含量的增加而减小㊂但理论分析与实验结果有出入,原因是Mn2+的电负性大于Mg2+㊂Mn2+与O2-的电负性低于Mg2+和O2-的电负性,导致Mn O的键长大于Mg O,因此掺入适量的Mn2+会使性能发生变化㊂随着Mn2+增加,Li(Mg1-x Mn x)PO4的品质因数快速上升,在875ħ后下降㊂Li(Mg1-x Ca x)PO4陶瓷的品质因数表现出与Li(Mg1-x Mn x)PO4陶瓷相同的变化趋势㊂由于样品致密化的恶化,品质因数的巅峰是在800ħ,随温度升高品质因数降低㊂LiMgPO4陶瓷中Ca2+的溶解极限为x=0.06㊂由于第二相的存在,当温度超过875ħ,x>0.06时Li(Mg1-x Ca x)PO4的品质因数下降㊂陶瓷的温度系数随离子取代度的增加变化范围不是特别明显,这意味着Mn2+和Ca2+对LiMgPO4陶瓷温度系数的影响不大,综合情况见表6㊂表6㊀B位掺杂LiMgPO4陶瓷的微波性能Table6㊀Microwave properties of B-doped LiMgPO4ceramicsRaw material Temperature/ħεr Q f/GHzτf/(ppm㊃ħ-1)ReferenceLi(Mg0.95Ni0.05)PO4875 6.9198600-55.3[27]Li(Mg0.95Co0.05)PO4875 6.97111200-53.8[28]Li(Mg0.92Mn0.08)PO4875 6.3471412-57.4[11]Li(Mg0.92Ca0.08)PO4875 6.8171223-51.4[11]由于离子取代键长和键布居数变化,烧结陶瓷性能改变㊂并且离子间的键能量增加,键长相应减小,振动频率与键能成正比,键长较长则易极化,使介电常数增大,故振动频率与介电常数成反比㊂4㊀PO4陶瓷的复合由于部分磷酸盐陶瓷温度系数过低,研究员通过添加材料改变原料配比替换样品内部A/B位离子来改变性能,也可通过复合其他具有特殊性能的陶瓷弥补自身缺陷来提高某些性能㊂为了研究了LiZnPO4陶瓷应用于LTCC领域的可行性,Xia等[33-35]在实验中发现850ħ下LiZnPO4能达到最大品质因数,此时品质因数为28496GHz,温度系数为-80.4ppm/ħ,由于LiZnPO4温度系数较低且TiO2有较高的温度系数,因此Xia等加入TiO2平衡数值㊂在研究不同比例下TiO2掺杂对陶瓷性能影响的过程中发现掺杂0.17(体积分数)TiO2的LiZnPO4在950ħ下烧结4h后的介电常数为10.0,品质因数为10025GHz,温度系数为1.6ppm/ħ㊂TiO2和LiZnPO4晶体结构的巨大差异和良好稳定性抑制了LiZnPO4和TiO2之间的化学反应,掺杂后性能的变化如表7所示㊂添加TiO2的LiZnPO4陶瓷与银电极有良好的兼容性,因此LiZnPO4-TiO2复合陶瓷在LTCC领域应用前景较为广泛㊂第3期温红娟等:低介电常数磷酸盐微波介质陶瓷的研究进展1033㊀表7㊀不同TiO 2体积分数的LiZnPO 4-TiO 2材料在850ħ下燃烧4h 后的微波性能[33]Table 7㊀Microwave properties of LiZnPO 4-TiO 2materials with different TiO 2volume fractionafter burning at 850ħfor 4h [33]Volume fraction of TiO 2εr Q f /GHz τf /(ppm㊃ħ-1)0 5.528496-80.20.148.313844-24.00.158.811769-21.50.1710.010025 1.60.1910.7100527.80.2110.91073824.3㊀㊀Guo 等[36]研究了(1-x )SrZn 2(PO 4)2-x TiO 2复合微波介质陶瓷,发现在整个x 值范围内,只能获得SrZn 2(PO 4)2和TiO 2两相,并且在合适的烧结温度下,所有成分都可以获得较高的相对密度㊂在相组成比的变化过程中,介电常数涨幅较小,温度系数变化较宽㊂在含有混合金属离子的正磷酸盐中,AZn 2(PO 4)2(A =Sr㊁Ba)在结构上可归类为硅酸盐长石族,其中A 位元素对使用相同制备路线获得的这些相的晶体结构有明显的影响㊂在SrZn 2(PO 4)2的晶体结构中,四氧配位锌和磷四面体构成了一个三维网络,形成了一个由锶原子在中心的包围网络伪层结构㊂其中Sr 2+和Zn 2+虽然具有较高活性但被氧多面体包围,导致烧结过程反应较慢,这体现了SrZn 2(PO 4)2晶体结构中良好的相位可调性,可改善介电性能㊂掺杂后复合磷酸盐性能随温度和掺杂浓度的变化如图6所示㊂图6㊀不同烧结温度下样品εr ㊁Q f 与τf 随掺杂浓度的变化[36]Fig.6㊀Changes of εr ,Q f and τf of samples with doping concentration at different sintering temperatures [36]在磷酸盐复合陶瓷中,由于采用了较高的TiO 2含量,晶粒的过度生长会在一定程度上受到抑制㊂当采用合适的烧结温度时,通过将两种成分组合在一起,可以获得较高的相对密度㊂在较低的烧结温度下,TiO 2含量较低(x <0.3)的陶瓷中介电常数差异不明显,含TiO 2多的陶瓷高温下介电常数随着TiO 2含量的增加而不断增加[37-39],不足是品质因数会有一定的降低,优点是改进了温度系数,使性能更加稳定㊂因此选择合适的第二项进行掺杂是未来的一个研究方向㊂Wang 等[40]对Ba 3(PO 4)2-BaWO 4复合陶瓷进行了研究,发现Ba 3(PO 4)2和BaWO 4在1100ħ下烧结2h 后共存,介电常数和温度系数随BaWO 4含量增加而降低㊂随x 增加,(1-x )Ba 3(PO 4)2-x BaWO 4复合陶瓷的性能变化如图7所示㊂综合图7(a)~(d)可知在x =0.2,温度为1100ħ时性能最好,其中介电常数随着BaWO 4含量的增加缓慢降低㊂Ba 3(PO 4)2的温度系数为正数,BaWO 4的温度系数为负数,随着BaWO 4含量增加,样品温度系数逐渐接近0㊂此处介绍了常见的两种复合类型㊂第一种是TiO 2复合调节温度系数,常见于一些温度系数负值过高的微波介质陶瓷材料的应用,但同时也会对材料本身品质因数和介电常数造成影响,因此可根据实践需要,调整合适的配比㊂未来研究方向为:在稳定温度系数的基础上,尝试将介电常数和品质因数的性能影响降至最。

半导体low k材料

半导体低k材料是指在半导体制造过程中用于减少电路中金属线与绝缘层之间的电容和信号延迟的一类材料。

传统的绝缘层材料如二氧化硅在微小尺寸的芯片中会导致信号传输延迟和能耗增加,因此需要寻找低介电常数(低k值)的材料来替代。

这种材料通常被用于制造先进的集成电路和微处理器。

半导体低k材料的选择要考虑到多个因素。

首先是介电常数,即k值,这是衡量材料绝缘性能的重要参数,k值越低表示材料的绝缘性能越好。

其次是材料的机械性能,包括弹性模量、硬度和脆性等,因为在制造过程中需要考虑到材料的加工性能和稳定性。

此外,化学稳定性也是一个重要考量因素,特别是在芯片制造过程中需要进行多道化学处理的情况下。

最后,成本也是一个重要的考量因素,因为材料的选择不仅要考虑性能,还要考虑到成本效益。

在实际应用中,半导体低k材料主要有有机低k材料和无机低k材料两大类。

有机低k材料通常是碳氢化合物的聚合物,具有较低的介电常数和良好的加工性能,但其化学稳定性和机械性能相对较差。

无机低k材料则主要是氧化物、氮化物和氟化物等化合物,具有较好的机械性能和化学稳定性,但通常介电常数略高于有机低

k材料。

总的来说,半导体低k材料在微电子制造中起着至关重要的作用,不仅可以提高芯片的性能,还可以降低功耗和延迟,因此对于半导体行业来说,低k材料的研发和应用是一个重要的课题。

半导体器件中的l o w-k技术(总7页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--半导体集成电路中的low-k技术摘要:随着芯片集成度的不断提高,RC时延、串扰噪声和功耗等越来越成为严重的问题。

low-k(低介电常数)技术在这样的背景下产生并逐渐应用到集成电路工艺中。

low-k材料代替SiO2能够进一步提高芯片的速度,但在low-k材料带来巨大技术优势的同时,也带来了一些技术性难题。

研究新型low-k材料并提升其相应的性能,将极大的促进集成电路的发展。

关键词: 集成电路 low-k技术低介电常数多孔材料1 前言随着超大规模集成电路(Very Large Scale Integration,VLSI)的高速发展,芯片的集成度不断提高,特征尺寸不断减小。

金属互连的多层布线导致金属导线的电阻、线间电容和层间电容增大,从而使RC延迟时间、串扰噪声和功耗等增加,这些问题成为集成电路进一步发展的制约因素[1,2]。

为了解决上述问题,提高芯片的速度,一方面用采用Cu金属互连线代替Al金属,减少电阻(Cu电阻率为×10-8Ω·m,Al电阻率×10-8Ω·m)。

另一方面用low-k电介质(k<3)代替SiO2(k=~,降低金属互连层间绝缘层的介电常数k[3,4]。

90 nm 工艺要求k = ~;65 nm工艺要求k = ~;45 nm 工艺要求k = ~[3];32nm及以下工艺要求k值在之下[5]。

因此,low-k技术已经成为集成电路领域的重点研究内容之一。

2 low-k技术的优势图1 分布电容示意图low-k技术就是就是寻找介电常数(k)较小的材料作为芯片内部电路层之间的绝缘介质ILD(Inter Layer Dielectrics,层间电介质),防止各层电路的相互干扰,以提升芯片的稳定性和工作频率。

集成电路的速度由晶体管的栅延时和信号的传播延时共同决定,使用high-k材料可以有效地降低栅延时。

专题论述低介电常数聚酰亚胺的研究进展李艳青,唐旭东,董 杰(天津科技大学材料科学与化学工程学院,天津 300457) 摘 要:现代微电子工业要求层间绝缘材料具有较低的介电常数。

该文介绍了几种降低聚酰亚胺介电常数的方法,包括含氟聚酰亚胺、聚酰亚胺无机杂化复合材料和聚酰亚胺多孔材料,其中最为有效的措施是将含氟取代基引入到聚酰亚胺分子结构中。

关键词:低介电常数;聚酰亚胺;含氟;无机杂化;多孔材料中图分类号:T Q32317 文献标识码:A 文章编号:10062334X (2010)022*******收稿日期:2010-04-06作者简介:李艳青(1984-),河北廊坊人,硕士,研究方向为高分子新材料,已发表论文1篇。

聚酰亚胺(P I )是重复单元中含有酰亚胺基团的芳杂环高分子化合物,刚性酰亚胺结构赋予了聚酰亚胺独特的性能,如良好的力学性能、耐高温性能、尺寸稳定性、耐溶剂性等,成功应用于航空、航天、电子电器、机械化工等行业。

随着微电子工业的不断发展,对相关材料的耐热性能以及介电性能等提出了更高的要求,这为P I 材料在微电子领域内的应用起到了极大的推动作用。

聚酰亚胺虽然应用广泛,但也存在不溶不熔、亚胺化温度高、颜色较深、吸湿率偏高和介电常数偏高等缺点。

现代微电子工业为了达到更高的集成度,要求芯片尺寸越来越小,芯片中信号传输的延迟时间也会相应增加,这种延迟时间与层间绝缘材料的介电常数成正比。

为了提高信号的传输速度,必须将层间绝缘材料的介电常数降低至2.0~2.5,通常聚酰亚胺材料的介电常数为3.0~3.5,难以满足这一要求,为了降低聚酰亚胺的介电常数,人们对其进行了大量的改性工作,主要包括:引入含氟取代基、掺杂无机低介电材料、在聚酰亚胺基体材料中引入空隙,其中最为有效的措施之一是将含氟取代基引入到聚酰亚胺的分子结构中。

1 含氟聚酰亚胺为了降低P I 的介电常数,研究最多的是将含氟取代基引入到P I 分子结构中,通常引入氟元素可以将介电常数降低到2.3~2.9。

罗杰斯4450f介电常数全文共四篇示例,供读者参考第一篇示例:罗杰斯4450F是一种低损耗介电常数材料,具有优异的性能特点,被广泛应用于微波电路和射频设备中。

介电常数是衡量材料对电场响应的重要指标,对于微波电路的设计和性能至关重要。

在本文中,我们将探讨罗杰斯4450F介电常数的特性及其在微波电路中的应用。

介电常数是材料对电场的响应能力的量度,通常用εr表示。

对于微波电路而言,介电常数直接影响着信号的传输速度、衰减损耗、谐振频率等性能指标。

低介电常数的材料能够提高微波电路的工作频率,减小信号的传输损耗,提高性能稳定性。

而罗杰斯4450F是一种高性能的低介电常数材料,具有非常优越的性能表现。

罗杰斯4450F的介电常数范围在2.2到2.65之间,这意味着它具有非常低的介电常数。

这种低介电常数使得罗杰斯4450F适用于高频微波电路的设计,能够提高信号的传输速度,减小损耗。

罗杰斯4450F还具有稳定的介电常数,能够在不同工作条件下保持优异的性能表现。

除了低介电常数外,罗杰斯4450F还具有优异的耐高温性能、化学稳定性和机械性能。

这些特性使得它在复杂的工作环境下都能够稳定运行,不易受外界因素的影响。

罗杰斯4450F还具有较低的热膨胀系数和优良的尺寸稳定性,能够满足微波电路对于尺寸精度的要求。

在微波电路设计中,罗杰斯4450F通常被用于制作功分器、混频器、衰减器、滤波器等元件。

它能够提高微波电路的性能、稳定性和可靠性,使得整个系统的工作效率得到提升。

由于罗杰斯4450F具有优异的加工性能,能够实现精细的加工工艺,因此在微波电路的制造过程中也得到了广泛应用。

第二篇示例:罗杰斯4450F介电常数是一种优质的介电材料,被广泛应用于微波和射频领域。

该材料具有优异的介电性能和机械性能,能够满足高频电路设计的要求。

本文将介绍罗杰斯4450F介电常数的特性、应用领域以及未来发展趋势。

罗杰斯4450F是一种PTFE基介电材料,其介电常数为2.65,是一种低损耗介电材料。