PLL格式_频率合成实验

- 格式:doc

- 大小:380.50 KB

- 文档页数:7

科技与创新┃Science and Technology & Innovation·120·文章编号:2095-6835(2016)11-0120-02DDS 激励PLL 方式的频率合成器设计武志敏(河北诺亚人力资源开发有限公司,河北 石家庄 050081)摘 要:DDS+PLL 是目前频率合成技术的常用组合方式之一。

首先就DDS+PLL 的几种常用合成方式的特点进行了简单介绍,然后重点利用DDS 激励PLL 的方式,实现了一种低杂散低相噪的频率合成器的设计。

在自己的工作中证明了该方案的可实现性。

关键词:DDS ;PLL ;低杂散;低相位噪声;频率合成器中图分类号:TN97 文献标识码:A DOI :10.15913/ki.kjycx.2016.11.120现代通信技术的发展迅猛,使得电子对抗领域对频率源的准确度、换频时间以及杂散相位噪声等技术指标的要求越来越高。

一般我们经常使用DDS+PLL 的方法来实现高频率、小步进、低相噪的频率合成器设计。

以下是对DDS+PLL 的常见组合方式作一简介。

1 DDS+PLL 的频率合成方式 1.1 DDS 内插于PLL这种方式是把DDS 看作分频器插入PLL 。

正是因为DDS 的频率的分辨率是非常高的,因而可以实现宽频带、小步进频率的合成。

但是因为DDS 还可实现小数分频,所以会有部分频段出现杂散现象。

1.2 DDS 倍频于PLL此种方式是将DDS 作为PLL 倍频的参考信号,PLL 就成了N 倍频环。

此方式的优点是:电路设计简单,可以得到较高的频率输出。

因而适合应用在相对杂散、指标要求不是很高的分机以及系统中。

缺点是:因为PLL 用于直接倍频,所以在环路噪声带宽内的输出信号,相位噪声以及杂散指标,都将恶化20 dB 。

1.3 DDS 和PLL 直接混频此方式是将PLL 信号作为本振信号,将DDS 信号做上变频、混频后,再通过一级带通滤波器将信号输出。

模拟锁相环实验报告锁相环(PLL)是一种常见的控制系统,它可以将输入信号的频率和相位与参考信号匹配,从而实现精确的信号同步和频率锁定。

本次实验旨在通过模拟锁相环的实验,了解PLL的基本原理和实现方式,并探究其在频率合成和时钟恢复等应用中的优势和局限性。

一、实验原理1.1 PLL的基本原理PLL由相频比较器、环形控制器、振荡器和分频器等组成。

其基本原理如下:(1)将参考信号和输出信号输入相频比较器,得到误差信号;(2)将误差信号输入环形控制器,控制其输出的控制电压;(3)将控制电压输入振荡器,控制其输出的频率和相位;(4)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制。

通过不断比较和修正,PLL可以使输出信号的频率和相位与参考信号匹配,从而实现锁定。

1.2 实验器材本次实验采用的器材如下:信号发生器、示波器、多路开关、振荡器、计数器等。

1.3 实验步骤(1)将信号发生器产生的正弦波信号作为参考信号,通过示波器观测其频率和相位;(2)将信号发生器产生的方波信号作为输入信号,通过多路开关控制输入信号的频率和幅值;(3)将输入信号和参考信号输入相频比较器,得到误差信号;(4)将误差信号输入环形控制器,控制其输出的控制电压;(5)将控制电压输入振荡器,控制其输出的频率和相位;(6)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制;(7)通过计数器观测输出信号的频率和相位,调整环形控制器的参数,使输出信号与参考信号匹配。

二、实验结果在实验过程中,我们先设置参考信号的频率为1KHz,通过示波器观测其频率和相位,然后将信号发生器产生的方波信号作为输入信号,进行频率和幅值的调节,使其与参考信号匹配。

在调节的过程中,我们观测到输出信号的频率和相位逐渐趋近于参考信号的频率和相位,最终实现了同步锁定。

然后,我们进一步测试了PLL在频率合成和时钟恢复等应用中的性能。

我们将输入信号的频率和幅值进行变化,观测输出信号的变化情况。

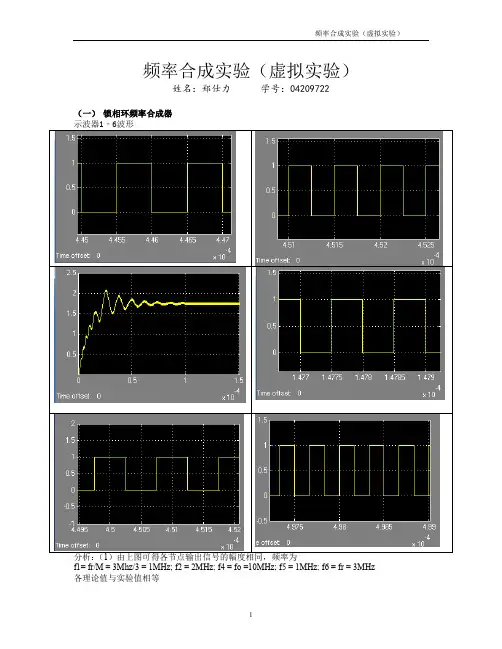

频率合成实验(虚拟实验)姓名:郑仕力学号:04209722(一)锁相环频率合成器f1= fr/M = 3Mhz/3 = 1MHz; f2 = 2MHz; f4 = fo =10MHz; f5 = 1MHz; f6 = fr = 3MHz 各理论值与实验值相等(2)示波器3中的VCO的控制电压的变化曲线,其从开始阶跃到固定值间经历的时间为1.4×10﹣4 s,即为环路的锁定时间。

稳定值为1.75V。

分析:(将synSen的初始值为3e6与5e6分别与初始情况作比较)(1)改变synSen的初始值,无论是增大还是减小,除示波器3外,其余示波器波形的周期幅度均没有变化,说明改变压控振荡器的压控灵敏度不会改变输出信号的频率。

(2)synSen的初始值为3e6,即相对4e6减小,示波器3中的电压最大值增大,稳定值也增大,环路锁定时间增大。

synSen的初始值为5e6,即相对4e6增大,示波器3中的电压最大值减小,稳定值也减小,环路锁定时间1.2×10﹣4 s,减小。

(3)对于基本单环频率合成器,捕获时间tp=4/ζwn=8Nτ1/τ2K0K d,压控灵敏度K0增大,捕获时间减小。

(二)小数频率合成器分析:(1)reference信号的频率为10MHz,divided synthesized信号的频率为10MHz,但相位延迟π/2,phase difference信号频率为20MHz。

(2)因为synM=0.3,synN=10,所以一个循环周期内的分频次数为P=10,一个循环周期内删除脉冲的个数为Q=3,10次分频中,必须进行7次10分频,3次11分频,则一个循环周期内总的平均分频比为10.3。

(3)合成信号的频率大于100MHZ,因为fout=fref*10.3。

《基于FPGA的PLL+DDS的频率合成器》篇一一、引言随着电子技术的发展,频率合成器作为现代通信、雷达、电子对抗等系统中的核心部件,其性能和稳定性要求越来越高。

FPGA(现场可编程门阵列)技术以其灵活、高速、低功耗等优势,在频率合成器的设计中得到了广泛应用。

本文将详细介绍基于FPGA的PLL(锁相环)+DDS(直接数字频率合成器)的频率合成器设计。

二、PLL+DDS原理概述PLL是一种能够跟踪输入信号频率并产生精确输出信号的电路。

DDS则是一种基于数字算法生成任意频率、相位和幅度的信号的技术。

将PLL和DDS相结合,可以实现高精度、高稳定性的频率合成。

在基于FPGA的PLL+DDS的频率合成器中,PLL用于提供稳定的参考频率,而DDS则用于生成所需的各种频率信号。

通过FPGA对PLL和DDS的控制,可以实现频率的快速切换和调整,满足不同应用场景的需求。

三、FPGA在频率合成器中的应用FPGA在频率合成器中的应用主要体现在以下几个方面:1. 控制逻辑设计:FPGA可以实现对PLL和DDS的控制逻辑设计,包括信号的输入、输出、频率切换等操作。

2. 高速数据处理:FPGA具有高速数据处理能力,可以实现对DDS生成的高速率数字信号的处理和传输。

3. 灵活性高:FPGA的现场可编程特性使得频率合成器的设计具有很高的灵活性,可以根据不同需求进行定制化设计。

四、基于FPGA的PLL+DDS的频率合成器设计基于FPGA的PLL+DDS的频率合成器设计主要包括以下几个部分:1. 参考频率源设计:采用高稳定度的晶体振荡器作为参考频率源,为PLL提供稳定的参考信号。

2. PLL模块设计:利用FPGA实现PLL模块的设计,通过调整环路参数实现精确的频率跟踪和相位锁定。

3. DDS模块设计:采用FPGA实现DDS模块的设计,生成所需的各种频率信号。

4. 信号处理与输出:通过FPGA对DDS生成的数字信号进行高速处理和传输,并输出到相应的设备或系统。

《基于FPGA的PLL+DDS的频率合成器》篇一一、引言随着通信技术的飞速发展,频率合成器作为通信系统中的关键部分,其性能的优劣直接影响到整个系统的性能。

FPGA(现场可编程门阵列)因其强大的并行处理能力和可定制性,被广泛应用于频率合成器的设计与实现。

本文将详细介绍基于FPGA的PLL(锁相环)+DDS(直接数字合成器)的频率合成器设计及其优势。

二、PLL与DDS的基本原理1. 锁相环(PLL)PLL是一种用于同步两个信号的电路,其基本原理是通过比较输入信号与参考信号的相位差,自动调整输出信号的相位和频率,以实现两者之间的同步。

PLL在频率合成器中起着核心作用,用于生成精确且稳定的频率信号。

2. 直接数字合成器(DDS)DDS是一种利用数字方式生成信号的电路,它通过将信号采样并进行编码调制,产生模拟的连续信号。

DDS在频率合成器中具有快速转换、低功耗和相位噪声小等优点。

三、基于FPGA的PLL+DDS频率合成器的设计基于FPGA的PLL+DDS频率合成器设计,是将PLL和DDS 的优势相结合,利用FPGA的高性能和灵活性实现高精度的频率合成。

设计过程中,首先需要根据应用需求确定频率合成器的性能指标,如输出频率范围、频率切换速度等。

然后,通过FPGA 实现PLL和DDS的功能模块,包括相位比较器、环路滤波器、数字波形存储器和D/A转换器等。

最后,通过FPGA内部的逻辑控制单元将PLL和DDS模块进行连接和协调,实现频率的合成与输出。

四、FPGA在频率合成器中的应用优势FPGA在频率合成器中的应用具有以下优势:1. 高性能:FPGA具有强大的并行处理能力,可以快速实现复杂的算法和逻辑控制,提高频率合成器的性能。

2. 灵活性:FPGA具有可定制性,可以根据应用需求灵活调整电路结构和功能模块,实现不同性能指标的频率合成器。

3. 低功耗:与传统的硬件电路相比,FPGA具有较低的功耗,有利于降低系统的能耗。

第23卷 第10期 电子测量与仪器学报 Vol. 23 No. 102009年10月JOURNAL OF ELECTRONIC MEASUREMENT AND INSTRUMENT· 91 ·本文于2008年11月收到。

一种基于DDS+PLL 结构的频率合成器的设计蒋 涛 唐宗熙 张 彪(电子科技大学电子工程学院, 成都 610054)摘 要: 讨论了一种输出频带宽、跳频速度快、相位噪声低、频率分辨率高的频率合成器的设计方法。

该设计采用DDS+PLL 结构, 在对单片机的输出信号进行电平转换后采用并行数据控制方式对DDS 芯片进行置数, 并通过仿真软件设计了环路滤波器和DDS 后级低通滤波器, 改善了输出信号的相位噪声和杂散性能。

基于该方法研制实现了输出频率范围为700~1200 MHz 的宽带频率合成器, 实验结果表明该频率合成器输出功率大于+4 dBm, 环路锁定时间为14 µs, 输出信号相位噪声优于 −94 dBc/Hz@1kHz, 近端杂散抑制度大于−59 dBc 。

关键词: DDS ;锁相环;宽带中图分类号: TN74 文献标识码: A 国家标准学科分类代码: 510.101Design of frequency synthesizer based on DDS+PLLJiang Tao Tang Zongxi Zhang Biao(Electronic Engineering School of UESTC, Chengdu 610054, China)Abstract: A method to develop a frequency synthesizer with wide band, fast frequency switching speed, high fre-quency resolution and low phase noise is discussed. This method is based on the DDS+PLL structure. Parallel pro-gramming mode is used and the signal from the MCU is been switched to control DDS. The loop filter is optimized to have low phase noise performance and the computer emulation technology is used to design the lowpass filter. A fre-quency synthesizer sweeping from 700MHz to 1200MHz is been made. Experimental result shows that the output power is over +4dBm, frequency switching time is 14µs, phase noise is better than −94dBc/Hz@1kHz and the spurious suppression is more than −59dBc.Keywords: DDS; phase locked loop; wide band1 引 言频率合成器是电子系统的心脏, 是决定电子系统性能的关键设备, 随着雷达、电子对抗、卫星通信、航空航天等技术的发展, 各种系统对频率合成器的频谱纯度、频率稳定度、频率分辨率和工作带宽等指标也提出了越来越高的要求。

基于锁相环(PLL)L波段的频率合成技术赵慧娟【摘要】Frequency synthesizer is the core component of the electronic equipment,the performance of the performance of the overall performance of the electronic equipment.In this paper,a phase locked loop frequency technique based on phase locked loop (PLL) L band is studied.Its design scheme uses MC145152 to realize the phase locked loop,the external loop filter LPF and the voltage controlled oscillator VCO and other devices to achieve,with a strong research and design value.%频率合成器是电子设备的核心部件,其性能的优劣影响电子设备的整体性能。

本文研究了一种基于锁相环(PLL)L波段的锁相频率技术。

其设计方案使用MC145152来实现锁相环路,外加环路滤波器LPF和压控振荡器VCO等器件来实现,具有较强的研究设计价值。

【期刊名称】《电子测试》【年(卷),期】2016(000)001【总页数】4页(P24-27)【关键词】频率合成;锁相环;压控振荡器【作者】赵慧娟【作者单位】九州职业技术学院,江苏徐州,221116【正文语种】中文人类进入信息社会和知识经济发展的时代,信息产业是未来发展的重点,将为社会创造巨大的经济效益。

因此,信息产业的兴衰,将是21世纪衡量和再现一个民族创新和发展能力、生存和竞争能力的重要标志。

基于FPGA的PLL频率合成器设计频率合成技术是现代通信的重要组成部分,它是将一个高稳定度和高准确度的基准频率经过四则运算,产生同样稳定度和准确度的任意频率。

频率合成器是电子系统的心脏,是影响电子系统性能的关键因素之一。

本文结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,能够方便地应用于锁相环教学中,有一定的实用价值。

1 PLL频率合成器的基本原理频率合成器主要有直接式、锁相式、直接数字式和混合式4种。

目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。

本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

锁相频率合成器是由PLL构成的。

一个典型的锁相频率合成器的原理框图如图1所示。

它的工作过程可以简单描述为:鉴相器输出电流的平均直流值乘以环路滤波器的阻抗,形成VCO的输入控制电压。

VCO是一种电压—频率变换装置,具有一个比例常数。

环路滤波器的控制电压调整了VCO的输出相位,除以N后,等于比较频率的相位。

因为相位是频率的积分,所以这个过程同样适用于频率,输出频率可表示为:公式1只有在PLL处于锁定状态下才成立,而在PLL重新调整到锁定状态的中间过程不成立。

在实际应用中,R值是固定的,N值是可变的[2],XTAL为输入信号的频率。

2 系统设计整个系统的功能主要由FPGA芯片EPF10K10 LC84-4控制相关硬件实现。

本系统的原理框图如图2所示。

工作过程中,FPGA控制可预置的N/N+0.5的变化,当N/N+0.5变化时,输出信号频率响应跟着输入信号变化。

同时FPGA也实现了键盘扫描与液晶显示的功能。

2.1 系统硬件设计硬件上,如图3所示。

该系统部分主要由7大部分组成:外部系统时钟、4×4键盘控制电路、FPGA处理芯片、EPC2LC20型EPROM芯片、PLL芯片CD4046及其外围电路、液晶1602显示模块、示波器。

●应用与设计1引言频率源是现代射频和微波电子系统的心脏,其性能直接影响整个电子系统的功能,成为非常重要的部件。

频率源分为二大类:自激振荡源和合成频率源。

常见的自激振荡源有晶体振荡器、腔体振荡器、介质振荡器、压控振荡器、YIG振荡器和波形发生器等。

这些频率源的输出频率范围、调谐带宽、近端相噪等各不相同。

合成频率源的主要优点是频率稳定度高,尤其是相位噪声低,有的甚至比原子钟的相噪还低,使用灵活、控制方便、性能优越。

而缺点是成本高、技术难度大。

现代工程设计中对频率源的频率稳定度、精确度、频率范围等技术指标的要求越来越高。

要满足现代电子系统的这些要求在很多情况下必须使用频率合成技术。

频率合成是指将高精度和高稳定度的标准信号频率通过一系列的算术运算,产生具有相同稳定度和精确度的大量离散频率的技术。

锁相式频率源具有频率稳定度高、频谱纯、寄生杂波小及相位噪声低等优点,已被广泛用于各种通信和雷达系统。

笔者采用分频锁相频率合成技术设计了1.8GHz锁相频率源。

2锁相环技术的原理实现频率合成的方法可分为直接合成法与间接合成法。

二种频率合成技术的特点见表1。

锁相环(PLL)是由鉴相器(PD),环路滤波器采用PLL技术的合成频率源设计钟催林,肖化武,李军红(南华大学电气工程学院,湖南衡阳421000)摘要:介绍分频锁相频率合成技术。

通过对锁相环工作过程及相位噪声等的基本原理的分析,采用PLL技术成功设计了1.8GHz锁相频率源。

在该锁相源中分频鉴相器采用ADI公司的ADF4118,VCO采用M/A-COM公司的ML081100-01850,低通环路采用三阶RC低通滤波器。

其相位噪声为-75dBc/kHz、杂散抑制为-85dBc。

实验测试获得了较好的技术指标,能满足现代移动通信C网和G网射频子系统对本振源的要求。

关键词:分频锁相;频率合成;相位噪声;本振源中图分类号:TN741文献标识码:A文章编号:1006-6977(2006)05-0012-03Designofsynthesisfrequencesourceusingphase-lockedlooptechnologyZHONGCui-lin,XIAOHua-wu,LIJun-hong(SchoolofElectricalEngineering,NanhuaUniversity,Hengyang421000,China)Abstract:Thetechnologyoffrequencydivisionphase-lockedfrequencysynthesisisintroduced.Thefre-quencysourcewiththephase-lockedtechnologyissuccessfullydesignedthroughanalysisofthebasicprinciplephase-lockedloopandphasenoise.Inthesource,ADF4118wastakenasfrequencydivisionandphasediscriminationdevice,andML081100-0185wastakenasVCOdevice,whilethree-orderRCfilterwastakenaslow-passcyclecircuit.Theexperimenttestindicatesthattherequirementisgood.ThesourcecanmeettothedemandsoflocaloscillatorinradiofrequencysubsystemofmodernmobilecommunicationGSMandCDMAnetwork.Keywords:frequencydivisonandphase-locked;frequencysynthesis;phasenoise;localoscillatorsource图1锁相环路基本组成(LF)和压控振荡器(VCO)组成的自动相位控制系统,如图1所示。

频率合成实验(虚拟实验)姓名:刘文学号: 04009616(一)锁相环频率合成器示波器1‐6波形初始值设为4e7(40MHz/V)分析:30M参考频率经过3分频fr即为10M,fo经过10倍分频等于fr,所以fo就是100m,如图所示。

示波器1为示波器6的波形经过3分频后的方波,频率为1MHz。

压控振荡器上的控制电压的变化情况:从0开始震荡到1.75。

示波器4上的方波频率为10MHz。

经过N分频后和参考频率异或形成示波器2中的方波。

低通滤波器的作用是平滑平滑VCO的控制电压。

如果将低通滤波器的带宽减小,那么环路锁定时间会增加,锁定后控制电压更稳定。

将synSen 的初始值设为3e6(3MHz/V),示波器1‐6波形将synSen 的初始值设为5e6(5MHz/V),示波器1‐6波形分析:(将synSen的初始值为3e6与5e6与初始情况作比较)两种情况稳定后结果均与synSen为4e6时相同,捕捉时间也基本相同,这是由于PLL换频时间仅与参考信号频率有关。

但由VCO控制信号波形可以看出,30M参考频率经过3分频fr即为10M,fo经过10倍分频等于fr,所以fo就是100m,如图所示。

由于灵敏度不同导致需要的压控电压不同,如图3M的压控电压明显大于5M时的压控电压。

synSen为3e6时,捕捉过程控制信号波动较大,稳定后控制信号波动也较大,这是由于VCO压控灵敏度小导致同样的频偏需要的控制电压更高。

synSen为5e6时,捕捉过程信号波动较小,稳定后信号波动也较小。

(二)小数频率合成器分析:小数分频既是双模分频,十分之七个循环周期的时间,进行3分频,其余时间进行4分频,导致3.3倍分频。

输入信号频率为10MHz。

由图像可以看出,输出信号频率约为103.1MHz,分频比为10.31,与要求基本相符。

从波形中我们可以看到,由于相位累加器每次大约约累计1/3*2π的相位,使得Carry信号频率大约1/3输入信号。

基于PLL 的B3G 频率合成器的研究与设计冯建武北京邮电大学电信工程学院,北京(100876)E-mail :jianwu.feng.bupt@摘 要:本文首先介绍了频率合成技术的概念,并针对直接式、间接式和直接数字式三种频率合成技术的特点选择了更适合B3G 频率合成器应用的间接式PLL 频率合成技术;随后针对B3G 频率合成器的指标要求,对电路进行了详细设计,并着重分析了参考频率输入、中频输出、射频输出电路的设计;最后,给出了B3G 频率合成器电路的最终测试结果和改进措施。

关键词:频率合成器,PLL,B3G 中图分类号:TN929.531. 频率合成技术概述频率合成是指以一个或数个参考频率为基准,在某一频段内,综合产生并输出多个工作频率点的过程。

基于这个原理制成的频率源称为频率合成器。

在通信领域内,频率合成器主要用于产生收发信机的本振信号,是收发信机的关键组成部分[1]。

频率合成的方法主要有直接式、间接式和直接数字式三种基本类型。

直接式是最早出现的一种频率合成器,它是由一个或多个晶体振荡器经过开关转换,倍频,分频,混频,滤波后的各种频率进行一定的组合,从而产生所需频率的装置;应用锁相环路的频率合成方法称为间接式,锁相频率合成器利用了相位反馈控制原理来稳频,在对频率切换速度要求不高,但对相位噪声、杂散抑制要求较高时,锁相频率合成有其特殊的优势;最新的频率合成方法是直接数字式,它用数字计算机和数模变换器来产生信号,完成直接数字频率合成[2]。

锁相频率合成器利用了相位反馈控制原理来稳频,相位噪声低、杂散抑制度高。

数字锁相频率合成器除了体积小,具有较低的相噪的优点外,还具有良好的窄带跟踪滤波特性,对输入信号寄生干扰抑制能力强,不易错锁以及选择或改变波道方便等优点,在通信中得到了广泛应用[3]。

其结构框图如图1所示。

图 1 数字锁相频率合成器基本方框图在B3G 频率合成器设计中,由于不需要频繁的改变频率合成器的输出频率,但对相位噪声、杂散抑制的要求较高,所以最终选择了应用锁相环路(PLL)的频率合成方法。

频率合成实验(虚拟实验)

(一)锁相环频率合成器

示波器1‐6波形

由示波器1的波形可以看出前置分频器输出频率为1Mhz,通过计算输出方波波形的频率,可得出fout=fr*synN/SynM的关系。

通过示波器3的波形可看出,低通滤波器滤除了鉴相器输出的无用的高频成分和其它干扰分量。

通过环路的调节,输入参考信号和下分频器的输出信号之间相位差达到最小。

当环路趋近于锁定,滤波器输出稳定的控制电压用这个电压去控制VCO,最终使其输出频率稳定不再变化,此时输入参考时钟信号和下分频模块的输出信号之间频率相等,相位差不随时间变化,达到锁定状态。

由上图可得各节点输出信号的幅度相同,频率为f1=fr/M=3Mhz/3=1MHz;f2=2MHz;f4=fo=10MHz;f5=1MHz;f6=fr=3MHz。

各理论值与实验值相等.

示波器 3中的 VCO的控制电压的变化曲线,其从开始阶跃到固定值间经历的时间为1.4×

10^(-4) s,即为环路的锁定时间。

稳定值为1.75V。

分析:(将synSen的初始值为3e6与5e6与初始情况作比较)

(1)改变synSen的初始值,无论是增大还是减小,除示波器3外,其余示波器波形的周期幅度均没有变化,说明改变压控振荡器的压控灵敏度不会改变输出信号的频率。

(2)synSen的初始值为3e6,即相对4e6减小,示波器3中的电压最大值增大,稳定值也增大,环路锁定时间增大。

synSen的初始值为5e6,即相对4e6增大,示波器3中的电压最大值减小,稳定值也减小,环路锁定时间1.2×10﹣4 s,减小。

(3)对于基本单环频率合成器,捕获时间tp=4/ζwn=8Nτ1/τ2K0K d,压控灵敏度K0增大,捕获时间减小。

(二)小数频率合成器

分析:

reference信号的频率为10MHz,divided synthesized信号的频率为10MHz,但相位延迟π/2,phase difference信号频率为20MHz。

小数分频既是双模分频,十分之七个循环周期的时间,进行3分频,其余时间进行4分频,导致3.3倍分频。

因为synM=0.3,synN=10,所以一个循环周期内的分频次数为P=10,一个循环周期内删除脉冲的个数为Q=3,10次分频中,必须进行7次10分频,3次11分频,则一个循环周期内总的平均分频比为10.3。