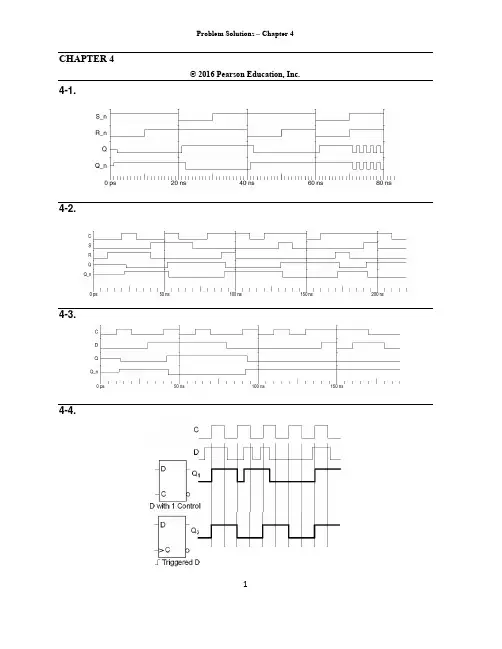

《逻辑与计算机设计基础》(原书第五版)课后习题答案-chapter10_solutions-5th

- 格式:pdf

- 大小:561.62 KB

- 文档页数:11

计算机网络第五版答案第一章概述1-01 计算机网络向用户可以提供那些服务?答:连通性和共享1-02 简述分组交换的要点。

答:(1)报文分组,加首部(2)经路由器储存转发(3)在目的地合并1-03 试从多个方面比较电路交换、报文交换和分组交换的主要优缺点。

答:(1)电路交换:端对端通信质量因约定了通信资源获得可靠保障,对连续传送大量数据效率高。

(2)报文交换:无须预约传输带宽,动态逐段利用传输带宽对突发式数据通信效率高,通信迅速。

(3)分组交换:具有报文交换之高效、迅速的要点,且各分组小,路由灵活,网络生存性能好。

1-04 为什么说因特网是自印刷术以来人类通信方面最大的变革?答:融合其他通信网络,在信息化过程中起核心作用,提供最好的连通性和信息共享,第一次提供了各种媒体形式的实时交互能力。

1-05 因特网的发展大致分为哪几个阶段?请指出这几个阶段的主要特点。

答:从单个网络APPANET向互联网发展;TCP/IP协议的初步成型建成三级结构的Internet;分为主干网、地区网和校园网;形成多层次ISP结构的Internet;ISP首次出现。

1-06 简述因特网标准制定的几个阶段?答:(1)因特网草案(Internet Draft) ——在这个阶段还不是 RFC 文档。

(2)建议标准(Proposed Standard) ——从这个阶段开始就成为 RFC 文档。

(3)草案标准(Draft Standard)(4)因特网标准(Internet Standard)1-07小写和大写开头的英文名字 internet 和Internet在意思上有何重要区别?答:(1) internet(互联网或互连网):通用名词,它泛指由多个计算机网络互连而成的网络。

;协议无特指(2)Internet(因特网):专用名词,特指采用 TCP/IP 协议的互联网络区别:后者实际上是前者的双向应用1-08 计算机网络都有哪些类别?各种类别的网络都有哪些特点?答:按范围:(1)广域网WAN:远程、高速、是Internet的核心网。

逻辑与计算机设计基础第五版逻辑与计算机设计是现代计算机科学的基础课程之一,它包含了逻辑学和计算机设计的基本原理与方法。

本文将介绍《逻辑与计算机设计基础第五版》这本教材的内容和意义。

逻辑学是研究思维规律和推理方法的学科,它对于计算机科学的发展具有重要的理论基础作用。

《逻辑与计算机设计基础第五版》从逻辑学的基本概念和原理入手,介绍了命题逻辑、谓词逻辑、命题演算与谓词演算等内容。

通过学习这些内容,读者可以了解逻辑学的基本知识,掌握逻辑推理的方法和技巧,从而提高自己的思维能力和解决问题的能力。

计算机设计是指设计和构造计算机硬件和软件的过程。

《逻辑与计算机设计基础第五版》以计算机硬件设计为主线,介绍了数字电路的基本原理和设计方法。

它从二进制系统、布尔代数和逻辑门开始,逐步讲解了组合逻辑电路和时序逻辑电路的设计与分析。

通过学习这些内容,读者可以了解计算机硬件的工作原理,掌握数字电路的设计和分析方法,从而能够设计和构造简单的计算机硬件系统。

除了逻辑学和计算机设计的基本原理和方法,本书还介绍了一些与计算机科学密切相关的内容,如数据表示与运算、存储器和输入输出设备、指令系统和汇编语言、计算机组成与体系结构等。

这些内容为读者进一步学习和研究计算机科学的相关领域奠定了坚实的基础。

《逻辑与计算机设计基础第五版》在编写过程中遵循了逻辑与计算机设计的基本原理,确保了内容的准确性和严谨性。

本书采用了简洁明了的语言,避免了晦涩难懂的数学公式和计算公式,使读者更好地理解和掌握相关知识。

此外,本书还配有丰富的例题和习题,供读者练习和巩固所学知识。

《逻辑与计算机设计基础第五版》是一本理论与实践相结合的教材,它既介绍了逻辑学和计算机设计的基本原理和方法,又通过实例和习题的方式帮助读者掌握相关技能。

对于计算机科学专业的学生和从事计算机相关工作的人员来说,它是一本必不可少的参考书。

阅读本书可以帮助读者建立起扎实的逻辑思维和计算机设计的基础,为进一步学习和研究计算机科学奠定坚实的基础。

第1章计算机系统概述1.1、图1.3中的理想机器还有两条I/O指令:0011 = 从I/O中载入AC0111 = 把AC保存到I/O中在这种情况下,12位地址标识一个特殊的外部设备。

请给出以下程序的执行过程(按照图1.4的格式):1.从设备5中载入AC。

2.加上存储器单元940的内容。

3.把AC保存到设备6中。

假设从设备5中取到的下一个值为3940单元中的值为2。

答案:存储器(16进制内容):300:3005;301:5940;302:7006步骤1:3005->IR;步骤2:3->AC步骤3:5940->IR;步骤4:3+2=5->AC步骤5:7006->IR:步骤6:AC->设备61.2、本章中用6步来描述图1.4中的程序执行情况,请使用MAR和MBR扩充这个描述。

答案:1. a. PC中包含第一条指令的地址300,该指令的内容被送入MAR中。

b. 地址为300的指令的内容(值为十六进制数1940)被送入MBR,并且PC增1。

这两个步骤是并行完成的。

c. MBR中的值被送入指令寄存器IR中。

2. a. 指令寄存器IR中的地址部分(940)被送入MAR中。

b. 地址940中的值被送入MBR中。

c. MBR中的值被送入AC中。

3. a. PC中的值(301)被送入MAR中。

b. 地址为301的指令的内容(值为十六进制数5941)被送入MBR,并且PC增1。

c. MBR中的值被送入指令寄存器IR中。

4. a. 指令寄存器IR中的地址部分(941)被送入MAR中。

b. 地址941中的值被送入MBR中。

c. AC中以前的内容和地址为941的存储单元中的内容相加,结果保存到AC中。

5. a. PC中的值(302)被送入MAR中。

b. 地址为302的指令的内容(值为十六进制数2941)被送入MBR,并且PC增1。

c. MBR中的值被送入指令寄存器IR中。

6. a. 指令寄存器IR中的地址部分(941)被送入MAR中。

课后练习题答案Chapter 11.1×√×√√×√××√1.2b c1.3ad1.4semicolon printf math.h \nChapter 22.1 ×√××√√×√××√×2.2 typedef 255 external constChapter 33.1 ×√××√√×××√√√3.2 integer modula 6 logical sizeof paratheses typeconversion precedence3.3 F F T F F F3.4 F T T T F3.5 (b) (c)3.6 0 -2 7 10.25 false 3 3 13.10 0 1 1 1 13.11d}1003.121101113.13 13.14 2003.15 x<=y3.16 TRUE3.192143.20-4040Chapter 44.1 ×√√√√√××√√√×4.2 %hd %x ctype.h %l %*d [^] blank 6 - %e4.4 (a) scanf(“%d %c %d”, &a, &b, &c); (b)scanf(“%d %f %s”, &a, &b, &c);(c) scanf(“%d-%d-%d”, &a, &b, &c); (d) scanf(“%d %s %d”, &a, &b, &c);4.5 (a)10x1.230000 (b)1234x 1.23 (c)1234 456.000000 (d) “123.40 ”(e) 1020 1222(乱码)4.7 (a)1988 x (b)乱码(c)120 乱码(d)乱码 x4.8 (a)1275 -235.740000(b) 1275-235.740000(c) 0 0.000000(d) 1275xxxx-235.74(e)Cambridge(f)1275 Cambridge4.10 1988 无无Chapter 55.1 √×√××××××√5.2 && switch break if-else x=y5.4 (a)x = 2; y = 0; (b) x = 1; y = 0;5.5 (a) if (grade <= 59)if (grade >= 50)second = second + 1;(b) if (number > 100) printf(“out of range”);else if (number < 0) printf(“out of range”);else sum = sum + number;(c)if (T > 200) printf(“admitted”);else if (M > 60){if (M > 60) printf(“admitted”);}else printf(“not admitted”);5.6 F T F T5.8 (a) x > 10 (b) (x != 10)||(y ! = 5) || (z >= 0)(c) (x + y != z) || (z > 5) (d) (x > 5) || (y != 10) || (z >= 5)5.9 (a) x = 5; y = 10; z = 1 (b) x = 5; y = 10; z = 1(c) x = 5; y = 0; z =0 (d) 无变化5.10 (a) x= 0; y = 2; z = 0; (b) x = 1; y = 2; z = 0;5.12 85.13 Delhi Bangalore END5.1424485.15 0 0 25.16 255.17 Number is negative5.18 ABC5.19 105.20 无输出Chapter 66.1 √√√××√×√√×6.2 n continue infinite indefinite-repetition-loop counter-variable 6.9 (a) 43210 (b)4321 (c)55555…55555(d)10 86.11 (a)无数次 x = 10; x = 5; x = 10; x = 5; x = 10;…(b)5次 m = 3, m = 5, m = 7, m = 9, m = 11(c)无数次, i 恒为0(d)4次 m = 11 n = 9; m = 12 n = 11; m = 13, n = 13; m = 14, n = 15;6.13(a)for (n = 1; n <= 32; n = n * 2) printf("%d ", n);(b)for (n = 1; n <= 243; n = n * 3) printf("%d ", n);(c)for (n = -4; n <= 4; n = n + 2) printf("%d ", n);(d)sum = 0;for (i = 2; i <= 16; i = sum){sum = sum + i;n = n - i;printf("%d %d %d \n", i, sum, n);}6.16 100 90 80 70 60 50 40 30 20 10 06.17 m = 20时陷入死循环,程序无输出6.18 16.19 16.20 死循环,延长时间用Chapter 77.1 √×√××√√√√××√7.2 index/subscript run-time dynamic multi-dimensional sorting7.14 157.15 HLOWRDChapter 88.1 ×√√√×√××√×××√×√8.2 %[ a-z,A-Z] strcpy 3 stdlib gets strlen strstr strcmp s1-s2 puts8.6 (a) The sky is the limit.(b) The sky is(c) T(d) The sky is the limit(e)8410410132115107121321051153211610410132108105109105116(f)输出1 2 3 4 5 6 7 8 9…21这些ASCII码对应的字符,无显示符号(g)%(h)U8.7 (d)8.8 78.9 (a)he(b)heorshe(c)5 78.11 puneChapter 99.1 √×××√×××√√√×××√×√√××9.2 actual-parameter local-variable int data-type variable-name scope recursive static type auto9.8 abceg9.9 abcdeg9.12 (a) 5 (b) 4 (c)3 (d)09.13 (a) 5 4 4 0 (b) 5.0 4.0 3.0 0.679.14 题目错,设z = 5;结果为:200 10009.15 1009.16 x = 3; y = 0Chapter 1010.1 ×√√√√×√√×√√√××√10.2 typedef union tag_name pointer memberChapter 1111.1 √×√√√√×√××11.2 address * * 0 null赠送以下资料5以内的加减法口算练习题姓名得分2+2= 3+2= 0+2= 0+1= 3-1= 2+1= 2+3= 1+4= 1-0= 2+2= 0-0= 3+2= 3-1= 2-1= 2+2= 4-3= 3+2= 2+2= 5-4= 3-1= 0+4= 4+1= 1+0= 0+0= 5-2= 3+2= 4-3= 2+2= 1+2= 5-2= 1+2= 2-0= 1+2= 4+1= 2+2= 2-0= 1-1= 2+2= 2-0= 1-0= 3+0= 4-2= 2-0= 3-0= 0+1= 4-1= 4+1= 3-1= 4-3= 2-0= 3-1= 1+3= 2-0= 1-0= 3+0= 1+2= 5-4= 1-1= 2+0= 3-1= 2-0= 0+1= 1+4= 2+3= 2-1= 3-1= 0+0= 2+2= 2-0= 3-1= 1+0= 1+2= 2+2= 1+3= 5-4= 0+2= 2+3= 1-0=5-2= 3-3= 1+2= 2-1= 3-3= 3-0= 4-4= 5-4= 2+2= 3-2= 3-0= 3+1= 2+1= 3-3= 4-4= 2-0= 4-0= 3-2= 3-0= 4-3= 5-2= 5+0=家长签名。

第1章计算机系统概述1.1 列出并简要地定义计算机的四个主要组成部分。

主存储器,存储数据和程序;算术逻辑单元,能处理二进制数据;控制单元,解读存储器中的指令并且使他们得到执行;输入/输出设备,由控制单元管理。

1.2 定义处理器寄存器的两种主要类别。

用户可见寄存器:优先使用这些寄存器,可以使机器语言或者汇编语言的程序员减少对主存储器的访问次数。

对高级语言而言,由优化编译器负责决定把哪些变量应该分配给主存储器。

一些高级语言,如C语言,允许程序言建议编译器把哪些变量保存在寄存器中。

控制和状态寄存器:用以控制处理器的操作,且主要被具有特权的操作系统例程使用,以控制程序的执行。

1.3 一般而言,一条机器指令能指定的四种不同操作是什么?处理器-寄存器:数据可以从处理器传送到存储器,或者从存储器传送到处理器。

处理器-I/O:通过处理器和I/O模块间的数据传送,数据可以输出到外部设备,或者从外部设备输入数据。

数据处理:处理器可以执行很多关于数据的算术操作或逻辑操作。

控制:某些指令可以改变执行顺序。

1.4 什么是中断?中断:其他模块(I/O,存储器)中断处理器正常处理过程的机制。

1.5 多中断的处理方式是什么?处理多中断有两种方法。

第一种方法是当正在处理一个中断时,禁止再发生中断。

第二种方法是定义中断优先级,允许高优先级的中断打断低优先级的中断处理器的运行。

1.6 存层次的各个元素间的特征是什么?存储器的三个重要特性是:价格,容量和访问时间。

1.7 什么是高速缓冲存储器?高速缓冲存储器是比主存小而快的存储器,用以协调主存跟处理器,作为最近储存地址的缓冲区。

1.8 列出并简要地定义I/O操作的三种技术。

可编程I/O:当处理器正在执行程序并遇到与I/O相关的指令时,它给相应的I/O模块发布命令(用以执行这个指令);在进一步的动作之前,处理器处于繁忙的等待中,直到该操作已经完成。

中断驱动I/O:当处理器正在执行程序并遇到与I/O相关的指令时,它给相应的I/O模块发布命令,并继续执行后续指令,直到后者完成,它将被I/O 模块中断。

《大学计算机》习题解答(2017.3)说明:1、部分思考题并无标准答案,需要学生在教材、校园网、因特网中查找相关资料;2、思考题能自圆其说者为“中”;言之有理者为“良”;举例说明者为“优”;3、思考题、简答题均以短小要点形式答题,不论有多少要点,答对3个均视为全部正确;各章习题参考答案第1章计算与计算思维1-1 简要说明计算机发展的三个历史阶段。

答:(1)古代计算机工具(2)中世纪计算机(3)现代计算机1-2 简要说明九九乘法口诀算法有哪些优点。

答:(1)建立了一套完整的算法规则;(2)具有临时存储功能,能连续运算;(3)出现了五进制;(4)制作简单,携带方便。

1-3 简要说明计算机集群系统有哪些特点。

答:(1)将多台计算机通过网络组成一个机群;(2)以单一系统模式管理;(3)并行计算;(4)提供高性能不停机服务;(5)系统计算能力非常高;(6)具有很好的容错功能。

1-4 简要说明各种类型计算机的主要特点。

答:(1)大型机计算机性能高。

(2)微机有海量应用软件,优秀的兼容能力,低价高性能。

(3)嵌入式计算机要求可靠性好。

1-5 简要说明图灵机的重要意义。

答:(1)图灵机证明了通用计算理论;(2)图灵机引入了读写、算法、程序、人工智能等概念;(3)复杂的理论问题可以转化为图灵机进行分析。

(4)图灵机可以分析什么是可计算的,什么是不可计算的。

1-6 简要说明冯诺依曼“存储程序”思想的重要性。

答:(1)为程序控制计算机提供了理论基础;(2)程序和数据的统一;(3)实现了程序控制计算机;(4)提高运算效率;(5)为程序员职业化提供了理论基础。

1-7 简要说明什么是计算思维。

答:周以真认为:计算思维是运用计算机科学的基础概念去求解问题、设计系统和理解人类行为,它涵盖了计算机科学的一系列思维活动。

1-8 举例说明计算思维的应用案例。

答:(1)复杂性分析:如战争分析、经济分析、算法分析等。

(2)抽象:如数据类型、数学公式等。

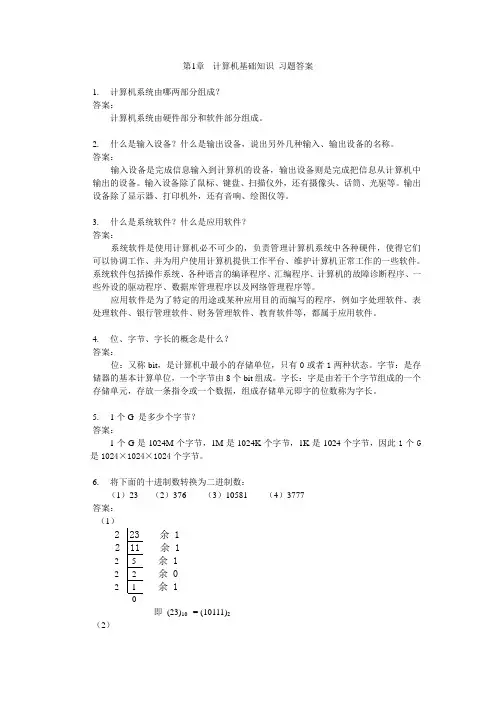

第1章计算机基础知识习题答案1.计算机系统由哪两部分组成?答案:计算机系统由硬件部分和软件部分组成。

2.什么是输入设备?什么是输出设备,说出另外几种输入、输出设备的名称。

答案:输入设备是完成信息输入到计算机的设备,输出设备则是完成把信息从计算机中输出的设备。

输入设备除了鼠标、键盘、扫描仪外,还有摄像头、话筒、光驱等。

输出设备除了显示器、打印机外,还有音响、绘图仪等。

3.什么是系统软件?什么是应用软件?答案:系统软件是使用计算机必不可少的,负责管理计算机系统中各种硬件,使得它们可以协调工作、并为用户使用计算机提供工作平台、维护计算机正常工作的一些软件。

系统软件包括操作系统、各种语言的编译程序、汇编程序、计算机的故障诊断程序、一些外设的驱动程序、数据库管理程序以及网络管理程序等。

应用软件是为了特定的用途或某种应用目的而编写的程序,例如字处理软件、表处理软件、银行管理软件、财务管理软件、教育软件等,都属于应用软件。

4.位、字节、字长的概念是什么?答案:位:又称bit,是计算机中最小的存储单位,只有0或者1两种状态。

字节:是存储器的基本计算单位,一个字节由8个bit组成。

字长:字是由若干个字节组成的一个存储单元,存放一条指令或一个数据,组成存储单元即字的位数称为字长。

5.1个G 是多少个字节?答案:1个G是1024M个字节,1M是1024K个字节,1K是1024个字节,因此1个G 是1024×1024×1024个字节。

6.将下面的十进制数转换为二进制数:(1)23 (2)376 (3)10581 (4)3777答案:(1)2 23 余 12 11 余 12 5 余 12 2 余 02 1 余 1即(23)10 = (10111)2(2)2 376 余 02 188 余 02 94 余 02 47 余 12 23 余 12 11 余12 5 余12 2 余02 1 余1即(376)10 = (101111000)2 (3)2 10581 余 12 5290 余 02 2645 余 12 1322 余 02 661 余 12 330 余02 165 余12 82 余02 41 余12 20 余02 10 余02 5 余12 2 余02 1 余1即(10581)10 = (101)2 (4)2 3777 余 12 1888 余 02 944 余 02 472 余 02 236 余 02 118 余02 59 余12 29 余12 14 余02 7 余12 3 余12 1 余1即(3777)10 27.将下面的二进制数转换为十进制数:答案:(1)(1101)2 =1×23+1×22+0×21+1×20 =(13)10(2)(10011101)2 =1×27+0×26+0×25+1×24+1×23+1×22+0×21+1×20 =(157)10(3)(11111111)2 =1×27+1×26+1×25+1×24+1×23+1×22+1×21+1×20 =(255)10(4)()2 =0×215+1×214+0×213+1×212+1×211+0×210+1×29+0×28+1×27+0×26+1×25+1×24+0×23+0×22+1×21+1×20=(23219)108.内存储器和外存储器的主要区别是什么?答案:主要区别是内存储器读写速度很快,外存储器读写速度相对较慢;内存储器数据在断电后将被清除,外存储器中的数据可以永久保存;内存储器的容量相对较小,而外存储器的容量可以很大。

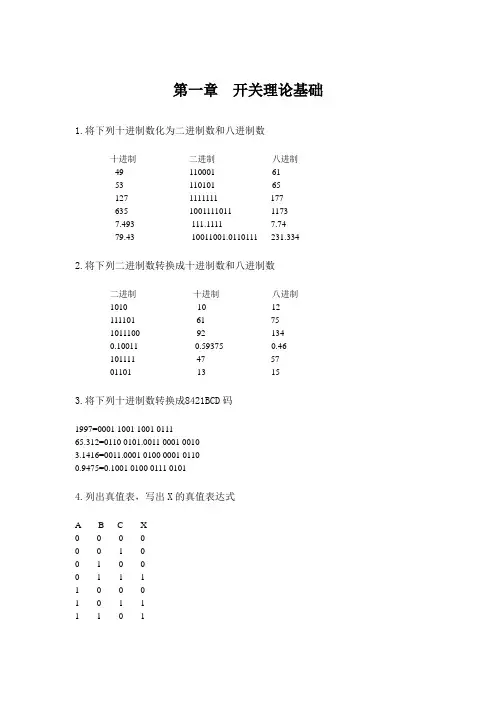

第一章开关理论基础1.将下列十进制数化为二进制数和八进制数十进制二进制八进制49 110001 6153 110101 65127 1111111 177635 1001111011 11737.493 111.1111 7.7479.43 10011001.0110111 231.3342.将下列二进制数转换成十进制数和八进制数二进制十进制八进制1010 10 12111101 61 751011100 92 1340.10011 0.59375 0.46101111 47 5701101 13 153.将下列十进制数转换成8421BCD码1997=0001 1001 1001 011165.312=0110 0101.0011 0001 00103.1416=0011.0001 0100 0001 01100.9475=0.1001 0100 0111 01014.列出真值表,写出X的真值表达式A B C X0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1 X=A BC+A B C+AB C+ABC5.求下列函数的值当A,B,C为0,1,0时:A B+BC=1(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,1,0时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,0,1时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=06.用真值表证明下列恒等式(1) (A⊕B)⊕C=A⊕(B⊕C)A B C (A⊕B)⊕C A⊕(B⊕C)0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 0 01 0 0 1 11 0 1 0 01 1 0 0 01 1 1 1 1所以由真值表得证。

(2)A⊕B⊕C=A⊕B⊕CA B C A⊕B⊕C A⊕B⊕C0 0 0 1 10 0 1 0 00 1 0 0 00 1 1 1 11 0 0 0 01 0 1 1 11 1 0 1 11 1 1 0 07.证明下列等式(1)A+A B=A+B证明:左边= A+A B=A(B+B)+A B=AB+A B+A B=AB+A B+AB+A B=A+B=右边(2)ABC+A B C+AB C=AB+AC证明:左边= ABC+A B C+AB C= ABC+A B C+AB C+ABC=AC(B+B)+AB(C+C)=AB+AC=右边(3)EDCCDACBAA)(++++=A+CD+E证明:左边=EDCCDACBAA)(++++=A+CD+A B C+CD E=A+CD+CD E=A+CD+E=右边(4)C B A C B A B A ++=CB C A B A ++证明:左边=CB AC B A B A ++=CB AC AB C B A B A +++)(=C B C A B A ++=右边8.用布尔代数化简下列各逻辑函数表达式(1) F=A+ABC+A C B +CB+C B = A+BC+C B(2) F =(A+B+C )(A+B+C) = (A+B)+C C = A+B(3) F =ABC D +ABD+BC D +ABCD+B C = AB+BC+BD(4) F=C AB C B BC A AC +++= BC(5) F=)()()()(B A B A B A B A ++++=BA 9.将下列函数展开为最小项表达式(1) F(A,B,C) = Σ(1,4,5,6,7)(2) F(A,B,C,D) = Σ(4,5,6,7,9,12,14)10.用卡诺图化简下列各式(1)CAB C B BC A AC F +++=0ABC00 01 11 1011111化简得F=C(2)CB A D A B A DC AB CD B A F++++=111111ABCD 00 01 11 1000011110化简得F=DA B A +(3) F(A,B,C,D)=∑m (0,1,2,5,6,7,8,9,13,14)1111111111AB CD 00 01 11 1000011110化简得F=DBC D C A BC A C B D C ++++(4) F(A,B,C,D)=∑m (0,13,14,15)+∑ϕ(1,2,3,9,10,11)Φ1ΦΦ1ΦΦ1Φ1AB CD 00 01 11 1000011110化简得F=ACAD B A ++11.利用与非门实现下列函数,并画出逻辑图。

1CHAPTER 1© 2016 Pearson Education, Inc.1-1.(a)(1) Calm:(2) 10 mph(3) 100 mphor(b) The microcomputer requires a table or equation for converting from rotations/second to miles/hour. The pulses produced by the rotating disk must be counted over a known period of time, and the table or equation used to convert the binary count to miles per hour.1-2.–34° quantizes to –30° => 1 V => 0001+31° quantizes to +30° => 7 V => 0111 +77° quantizes to +80° => 12 V => 1100 +108° quantizes to +110° => 15 V => 11111-3.*Decimal, Binary, Octal and Hexadecimal Numbers from (16)to (31)1-4.1020301281282131,0723232233,554,4328828,589,934,592=⨯==⨯==⨯=K Bits M Bits G Bits21-5.220 = (1,000,00010 + d ) where d = 48,576 1Tb = 240 = (220)2 = (1,000,000 + d )2= (1,000,000)2 + 2(1,000,000) d + d 2 = 1,000,000,000,000 + 97,152,000,000 + 2,359,627,776 = 1,099,511,627,7761-6.112511212047252133,554,4311 Bits 1 Bits ⇒-=⇒-=1-7.*63202641013275321142(1001101)222277(1010011.101)22222283.625(10101110.1001)2222222174.5625----=+++==+++++==++++++=1-8.1 1 0 0 0 0 0 0 0 0 0 1 0 11-9.*1-10.*a)0.45 × 8 = 3.6 =>0.60 × 8 = 4.8 =>0.80 × 8 = 6.4 =>0.20 × 8 = 3.2 =>10= (16612.3463)8b) (1938.257)10 = (792.41CB)16c) (175.175)10 = (10101111.001011)21-11.*a) (673.6)8= (110 111 011.110)2= (1BB.C)16b) (E7C.B)16= (1110 0111 1100.1011)2= (7174.54)8c) (310.2)4= (11 01 00.10)2= (64.4)81-12.a) 1010 b) 0110 c) 1111001×1100 ×1001 ×0111010000 0110 11110010000 0000 0000001010 0000 11110011010 0110 11110011111000 0110110 11110010000000110110110101341-13.+1000110110101101010000000010000110001101011-----Quotient = 10001R emainder = 1 1-14.(a) 6 × 123 + 8 × 122 + 7 × 121 + 4 = 11608 (b)12 1-15.a)0 1 2 3 4 5 6 7 8 9 A BCDEFGHIJb) 20c) 21012010(.)1120122018201620(4658.8)BCI G -=⨯+⨯+⨯+⨯=1-16.*a) (BEE)r = (2699)1021021114142699111426850r r r r r ⨯+⨯+⨯=⨯+⨯-=By the quadratic equation: r = 15 or ≈ –16.27 ANSWER: r = 15 b) (365)r = (194)102102365194361890r r r r r ⨯+⨯+⨯=⨯+⨯-=By the quadratic equation: r = – 9 or 7 ANSWER: r = 751-17.Errata: The text has an error: 1480 should be 1460. This will be corrected in future printings.Noting the order of operations, first add (34)r and (24)r101010(34)34(24)24(34)(24)58r r r r r r r r r r =⨯+⨯=⨯+⨯+=⨯+⨯Now, multiply the result by (21)r101021(21)(58)10218⨯+⨯⨯⨯+⨯=⨯+⨯+r r r r r r Next, set the result equal to (1480)r and reorganize.21321321010218146161580⨯+⨯+=⨯+⨯+⨯⨯-⨯-⨯-⨯=r r r r r r r r r Finally, find the roots of this cubic polynomial. Solutions are: r = 8, – 1, – 1ANSWER: The chicken has 4 toes on each foot (half of 8).1-18.*a) (0100 1000 0110 0111)BCD = (4867)10= (1001100000011)2 b) (0011 0111 1000.0111 0101)BCD= (378.75)10=(101111010.11)21-19.*(694)10 = (0110 1001 0100)BCD (835)10=(1000 0011 0101)BCD1001 0100 +0011 +0101 1100 1001 +0110 +00001 001010011-20.*(a)101 1000111 1000Move R 011 1100 0 100 column > 0111Subtract 3 −0011011 1001 0Subtract 3 −001101 1001Move R 0 1100 110 100 column > 0111Subtract 3 −00110 1001 110Move R 0100 1110Move R 010 01110Move R 01 001110Move R 0 1001110 Leftmost 1 in BCD numbershifted out: Finished(b) 102101 1000011 1001 0111Move R 001 1100 1011 1 101 and 100 columns > 0111Subtract 3 −0011 -0011001 1001 1000 1Move R 00 1100 1100 01 101 and 100 columns > 0111Subtract 3 −0011 −001100 1001 1001 01Move R 0 0100 1100 101 100 column > 0111Subtract 3 −00110 0100 1001Move R 0010 0100 1101Move R 001 0010 01101Move R 00 1001 001101 100 column > 0111Subtract 3 −001100 0110 001101Move R 0 0011 0001101Move R 0001 10001101Move R 000 110001101 Leftmost 1 in BCDnumber shifted out: Finished 1-21.(a) 10210110011110001st Move L 1 1110002nd Move L 11 110003rd Move L 111 1000 100 column > 100Add 3 00111010 10004th Move L 1 0101 000 100 column > 100Add 3 00111 1000 0005th Move L 11 0000 006th Move L 110 00000 101 column > 100Add 3 00111001 0000 07th Move L 1 0001 00000 Least significant bit in binary number moved in:Finished(b) 103102101100011100101111st Move L 0 11100101112nd Move L 01 1100101113rd Move L 011 100101114th Move L 0111 0010111 100 column > 100Add 3 001161010 00101115th Move L 1 0100 0101116th Move L 10 1000 10111 100 column > 100Add 3 001110 1011 101117th Move L 101 0111 0111 101 & 100 columns > 100Add 3 0011 00111000 1010 01118th Move L 1 0001 0100 1119th Move L 10 0010 1001 11 100 column > 100Add 3 001110 0010 1100 1110th Move L 100 0101 1001 1 101 &100 columns > 100Add 3 0011 0011100 1000 1100 111th Move L 1001 0001 1001 Least significant bit in binary number moved in: Finished1-22.From Table 1-5, complementing the bit B6 will switch an uppercase letter to a lower case letter and vice versa.1-23.a) The name used is Brent M. Ledvina. An alternative answer: use both upper and lower case letters.0100 0010 B 0101 0010 R 0100 0101 E0100 1110 N 0101 0100 T 0010 0000 (SP)0100 1101 M 0010 1110 . 0010 0000 (SP)0100 1100 L 0100 0101 E 0100 0100 D0101 0110 V 0100 1001 I 0100 1110 N0100 0001 Ab) 0100 0010 1101 0010 1100 01010100 1110 1101 0100 1010 00000100 1101 0010 1110 1010 00001100 1100 1100 0101 0100 01000101 0110 1100 1001 0100 11100100 00011-24.1000111 G1101111 o01000001000011 C1100001 a1110010 r1100100 d1101001 i1101110 n1100001 a (Errata: This number appears as 110001, which would be “1”)1101100 l1110011 s0100001 !781-25.*a) (11111111)2b) (0010 0101 0101)BCD c) 011 0010 011 0101 011 0101ASCIId)0011 00101011 01011011 0101ASCII with Odd Parity1-26.a) U+0040 = 01000000b) U+00A2 = 11000010 10100010c) U+20AC = 11100010 10000010 10101100d)U+1F6B2 = 11110000 10011111 10011010 101100101-27.Binary Numbers from (32)to (47) with Odd and Even Parity1-28.Gray Code for Hexadecimal Digits1-29.(a) Wind Direction Gray CodeDirectionCode WordN 000 S 110 E 011 W 101 NW 100 NE 001 SW 111 SE0109(b) Wind Direction Gray Code (directions in adjacent order)DirectionCode WordN 000 NE 001 E 011 SE 010 S 110 SW 111 W 101 NW100As the wind direction changes, the codes change in the order of the rows of this table, as suming that the bottom row is “next to” the top row. From the table, the codes that result due to a wind direction change always change in a single bit.1-30.+The percentage of power consumed by the Gray code counter compared to a binary code counter equals:Number of bit changes using Gray code Number of bit changes using binary codeAs shown in Table 1-6, and by definition, the number of bit changes per cycle of an n-bit Gray code counter is 1 per count = 2n .Number of bit changes using Gray code = 2nFor a binary counter, notice that the least significant bit changes on every increment. The second least significant bit changes on every other increment. The third digit changes on every fourth increment of the counter, and so on. As shown in Table 1-6, the most significant digit changes twice per cycle of the binary counter.Number of bit changes using binary code 11222n n -+++(1)110221(21)122nni i n n i i ++==⎡⎤==-=--=-⎢⎥⎣⎦∑∑ % Power (1)210022n n +=⨯-。

浙江大学计算机学院实验教学中心逻辑与计算机设计基础实验2010~2011秋冬9掌握二进制计数器/定时器的工作原理与设计方法掌握用计数器进行分频的概念和方法实验设备装有ISE的计算机系统1台Spartan III 实验板1套实验材料无设计一个数字钟,使用60进制和24(12)进制计数器,实现24小时内时间的实时显示。

60进制计数器用10进制与6进制计数器的组合来实现;24(12)进制可用类似方法实现。

采用4个计数器分别实现分钟的个位、分钟的十位、小时的个位、小时的十位计数。

数字钟的初值通过初始化语句来实现,用数码管前两位显示小时的十位和个位,后两位显示分钟的十位和个位。

把时钟加到多功能计算器中。

计数器是复杂数字系统和计算机硬件系统中的一个基本部件,是计数、分频、定时、同步和时基等电路的核心,在计算机、网络、通信等设备中经常使用到。

本实验以计数器为例,采用行为级描述的方法设计时序电路,实现各种常用的计数器和定时器。

•60进制计数器用10进制与6进制计数器的组合来实现•24进制计数器用4进制与6进制计数器的组合来实现module m_gen_min (clk_sec, clk_hour, min_low, min_high);input wire clk_sec;output reg clk_hour;output reg [3:0] min_low, min_high;reg [15:0] cnt;always @(posedge clk_sec) begin if (clk_hour == 1)clk_hour = 0;if (cnt == 59) begin cnt = 0;if (min_low == 9) begin min_low = 0; /* base 10 */if (min_high == 5) begin min_high = 0; /* base 6*/clk_hour = 1;end else min_high = min_high + 1;end else min_low = min_low + 1;end else cnt = cnt + 1;endendmodule分钟的生成以秒脉冲为时钟信号,将10进制和6进制组合成60进制,并产生小时脉冲信号。

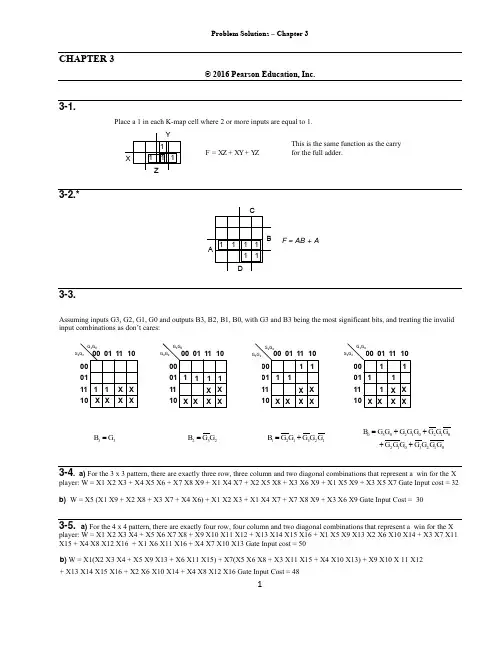

第二章布置习题参考解

2-1 用真值表验证XYZ=X+Y+Z 三变量DeMorgan定律

2-2 用代数化简来证明下列布尔方程的性质

a)

c)

2-3 用代数化简来证明下列布尔方程的性质

2-6 化简下列布尔表达式,使表达式中包含的因子最少

2-10

a)

c)

2-11

2-12

2-13

2-14

2-15

2-16

2-19

2-24

(a) 用两个三态缓冲器和一个非门实现函数H=XY+XZ。

(b) 用两个缓冲器和两个非门互联实现异或门。

2-33

(a) 把三个三态缓冲器的输出连在一起,增加一些逻辑(门)实现函数F=ABC+ABD+ABD C、D以及D是三态缓冲器的输入,A、B通过逻辑电路产生使能输入。

(b) 对于(a) 中设计的三态缓冲器的输出是不是没有冲突?如果不是,更改必要的设计,使设计的电路没有冲突。

上述设计没有三态输出冲突。

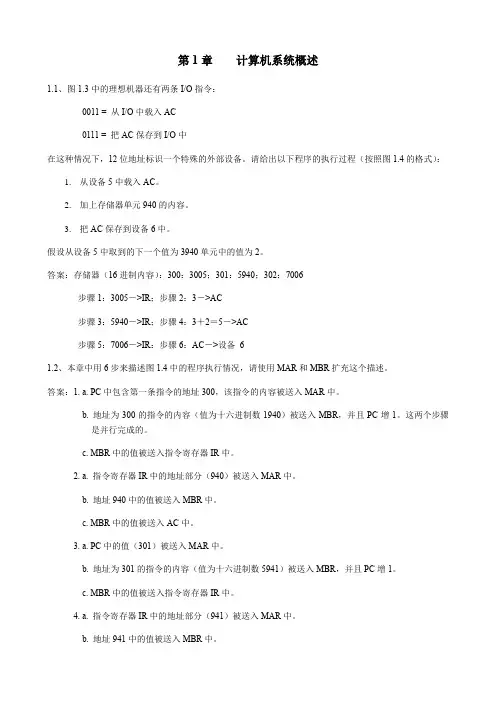

CHAPTER 10© 2016 Pearson Education, Inc.10-1.a) Maximum frequency = 1/pipe stage delay = 1/0.8 ns = 1.25 GHz.b) The latency time = 0.8 ns × 3 = 2.4ns.c) The maximum throughput is 1 instruction per cycle or 1.25 billion instructions per second.10-2.*a) The latency time = 0.5 ns × 8 = 4.0 ns.b) The maximum throughput is 1 instruction per cycle or 2 billion instructions per second.c) The time required to execute is 10 instruction + 8 pipe stages -1 = 17 cycles *0.5ns = 8.5ns 10-3.10-4.Register Indirect: Load, Store, JMRRegister, Immediate: ADI, SBI, ANI, ORI, XRI, AIU, SIURelative: BZ, BNZ, JMP, JMLNone: NOPRegister: All instructions not listed above10-5.a) Right, SH = 0F = 15 = 0 + 12 + 347 lines = 0000 3DF3 CB4A, 35 lines = 0 0003 DF3C, 32 lines = 0000 7BE7b) Left, SH = 1D = 29 Rt. Rotate = 64 29 = 35 = 32 + 0 + 347 lines = 4B4A 0000 0000, 35 lines = 2000 0000, 32 lines = 4000 00001Cycle 1: PC = 10FCycle 2: PC-1 = 110, IR = 4418 2F0116Cycle 3: PC-2 = 110, RW = 1, DA = 01, MD = 0, BS = 0, PS = X, MW = 0, FS = 2, SH = 01, MA = 0, MB =1, CS=1 BUS A = 0000 001F, BUS B = 0000 2F01Cycle 4: RW = 1, DA = 01, MD = 0, D0 = 0000 2F20, D1 = XXXX XXXX, D2 = 0000 00000Cycle 5: R1 = 0000 2F2010-7.Cycle 1: IF PC = 10FCycle 2: DOF PC-1 = 110,IR = 1A61 001DCycle 3: EX PC-2 = 110,RW = 1, DA = 06, MD = 2, BS = 0, PS = X, MW = 0, FS =D, SH = 1D, MA = 0, MB = 0 BUS A = 01AB CDEF, BUS B = XXXX XXXXCycle 4: RW = 1, DA = 06, MD = 0, D0 = 0000 0000, D1 = XXXX XXXX, D2 = 0000 0000Cycle 5: R6 = 0000 000010-8.Cycle 1: PC = 10FCycle 2: PC-1 = 110, IR = CA71 9400Cycle 3: PC-2 = 110, RW = 1, DA = 07, MD = 2, BS = 0, PS = 0, MW = 0, FS = 5, MA = 0, MB = 0, CS = 0 BUS A = 0000 F001, BUS B = 0000 000FCycle 4: RW = 1, DA = 07 MD = 0, D0 = 0000 EFF2, D1 = XXXX XXXX, D2 = 0000 0000Cycle 5: R7 = 0000 000010-9.Cycle 1: PC = 10FCycle 2: PC-1 = 110, IR = 8A21 635ACycle 3: PC-2 = 110, RW = 1, DA = 02, MD = 0, BS = 0, PS = X, MW = 0, FS=5, SH = 1A, MA= 0, MB = 1, CS=0 BUS A = 0A5F BC2B, BUS B = 0000 635ACycle 4: RW = 1, DA = 02, MD = 0, D0 = 0AF5 58D1, D1 = XXXX XXXX, D2 = 0000 00000Cycle 5: R2 = 0AF5 58D110-10.+Answer not given; varies depending on synthesis software used.10-11.*MOVA R7, R6SUB R8, R8, R6 AND R8, R8, R7MOV A R7, R6 SUB R8, R8, R6 AND R8, R8, R73SUB R7, R7, R2 BNZ R7, 000F AND R8, R7, R4 OR R4, R8, R210-13*a)MOV R7,R6 SUB R8,R8,R6NOPAND R8,R8,R7R6b)SUB R7,R7,R2NOPBNZ R7,000FNOP NOPAND R8,R7,R4NOPOR R4,R8,R2F210-14.OR R4, R8, R2SUB R7, R7, R2 AND R8, R7, R4BNZ R7, 000FIF PC: 0000 0001DOF PC−1: XXXXXXXX IR: XXXXXXXXEX PC−2: XXXXXXXX A: XXXXXXXX B: XXXXXXXX RW: X DA: XX MD: X BS: X PS: X MW: X FS: X MB: X CS: X WB D0: XXXXXXXX D1: XXXXXXXX D2: XXXXXXXX RW: X DA: XX MD: XTime Cycle 2IF PC: 0000 0002DOF PC−1: 0000 0002 IR: 0A73 8800EX PC−2: XXXXXXXX A: XXXXXXXX B: XXXXXXXX RW: X DA: XX MD: X BS: X PS: X MW: X FS: X MB: X CS: X WB D0: : XXXXXXXX D1: XXXXXXXX D2: XXXXXXXX RW: X DA: XX MD: XTime Cycle 3IF PC: 0000 0003DOF PC-1: 0000 0003 IR: 9003800FEX PC-2: 0000 0002 A: 0000 0030 B: 0000 0010 RW: 1 DA: 07 MD: 0 BS: 0 PS: X MW: 0 FS: 5 MB: 0 CS:X WB D0: XXXXXXXX D1: XXXXXXXX D2: XXXXXXXX RW: X DA: XX MD: XTime Cycle 4IF PC: 0000 0003DOF PC−1: 0000 0003 IR: 9003 800FEX PC−2: 0000 0002 A: 0000 0030 B: XXXXXXXX RW: 0 DA: 00 MD: X BS: 0 PS:X MW: 0 FS: 0 MB: 1 CS: X WB D0: 0000 0020 D1: XXXXXXXX D2: 0000 0000 RW: 1 DA: 07 MD: XTime Cycle 5IF PC: 0000 0004 R7: 0000 0020DOF PC-1: 0000 0004 IR: 1083 9000EX PC-2: 0000 0003 A: 0000 0020 B: XXXXXXXX RW: 0 DA: 00 MD: X BS: 1 PS:1 MW: 0 FS: 0 MB: 1 CS: X WB D0: 0000 0030 D1: XXXXXXXX D2: 0000 0000 RW: 0 DA: 00 MD: X PC: 0000 0012Time Cycle 6IF PC: 0000 0012DOF PC-1: 0000 0004 IR: 12440800EX PC-2: 0000 0003 A: 0000 0020 B: 0000 0020 RW: 1 DA: 08 MD: 0 BS: 0 PS:X MW: 0 FS: 8 MB: 0 CS: X WB D0: 0000 0020 D1:XXXXXXXX D2: 0000 0000 RW: 0 DA: 00 MD: XTime Cycle 7IF PC: 0000 0012DOF PC-1: 0000 0004 IR: 12440800EX PC-2: 0000 0004 A: XXXXXXXX B: 0000 0010 RW: 0 DA: 00 MD: 0 BS: 0 PS:X MW: 0 FS: 8 MB: 0 CS: X WB D0: 0000 0020 D1: XXXXXXXX D2: 0000 0000 RW: 1 DA: 08 MD: 0Time Cycle 8IF PC: 0000 0013 R8: 0000 0020DOF PC-1: 0000 0013 IR: XXXXXXXXEX PC-2: 0000 0004 A: 0000 0020 B: 0000 0010 RW: 1 DA: 04 MD: 0 BS: 0 PS: X MW: 0 FS: 9 MB: 0 CS: X WB D0: XXXXXXXX D1: XXXXXXXX D2: XXXXXXXX RW: 0 DA: 00 MD: 0Time Cycle 9IF PC: 0000 0014DOF PC-1: 0000 0014 IR: XXXXXXXXEX PC-2: 0000 0013 A: XXXXXXXX B: XXXXXXXX RW: X DA: XX MD: X BS: X PS: X MW: X FS: X MB: 0 CS: X WB D0: 0000 0020 D1: XXXXXXXX D2: 0000 0000 RW: 1 DA: 04 MD: 0Time Cycle 10IF R4: 0000 0020Fields not specified above have fixed values throughout or are unused: MA = 0, D’, and SH. Based on the register contents, the branch is taken. The data hazards are avoided, but due to the control hazard, the last two instructions are erroneously executed.IF PC: 0000 0001DOF PC-1:XXXXXXXX IR: XXXXXXXXEX PC-2:XXXXXXXX A: XXXXXXXX B: XXXXXXXX RW:X DA:XX MD:X BS:X PS:X MW:X FS:X MB:X MA:X CS:X D’:XWB D0: XXXXXXXX D1:XXXXXXXX D2:XXXXXXXX RW:X DA:XX MD:XTime Cycle 2IF PC: 0000 0002DOF PC-1:0000 0002 IR: 0A73 8800EX PC-2:XXXXXXXX A: XXXXXXXX B: XXXXXXXX RW:X DA:XX MD:X BS:X PS:X MW:X FS:X MB:X MA:X C S:X D’:XWB D0: XXXXXXXX D1:XXXXXXXX D2:XXXXXXXX RW:X DA:XX MD:XTime Cycle 3IF PC: 0000 0003DOF PC-1:0000 0003 IR: 9003 800FEX PC-2:0000 0002 A: 0000 0030 B: 0000 0010 RW:1 DA:07 MD:0 BS:0 PS:X MW:0 FS:5 MB:0 MA:0 CS:X D’:XWB D0: XXXXXXXX D1:XXXXXXXX D2:XXXXXXXX RW:X DA:XX MD:XTime Cycle 4IF PC: 0000 0004DOF PC-1:0000 0004 IR:1083 9000EX PC-2:0000 0003 A: 0000 0020 B: XXXXXXXX RW:0 DA:XX MD:X BS:1 PS:1 MW:0 FS:0 MB:1 MA:2 CS:1 D’:1WB D0: 0000 0020 D1:XXXX XXXX D2:0000 0000 RW:1 DA:07 MD: 0 PC: 0000 0012Time Cycle 5IF PC: 0000 0013 R7: 0000 0020DOF PC-1: 0000 00013 IR: 1244 0800EX PC-2: 0000 0004 A: 0000 0020 B: 0000 0020 RW: 1 DA: 08 MD: 0 BS: 0 PS: X MW: 0 FS: 8 MB:0 MA:0 CS:X D’:XWB D0: 0000 0020 D1: XXXXXXXX D2: 0000 0000 RW: 0 DA: 00 MD: 0Time Cycle 6IF PC: 0000 0014DOF PC-1: 0000 0014 IR: XXXX XXXXEX PC-2: 0000 0013 A: 0000 0020 B: 0000 0010 RW: 1 DA: 04 MD: 0 BS: 0 PS: X MW: 0 FS: 9 MB:0 MA:0 CS:X D’:XWB D0: 0000 0010 D1: XXXX XXXX D2: 0000 0000 RW: 1 DA: 08 MD: 0Time Cycle 7IF PC: 0000 0014 R7: 0000 0020DOF PC-1: 0000 0014 IR: XXXX XXXXEX PC-2: 0000 0013 A:XXXX XXXX B: XXXX XXXX RW: X DA: XX MD:X BS: X PS:X MW:X FS:X MB:X CS:X D’:XWB D0: 0000 0010 D1: XXXX XXXX D2: 0000 0000 RW: 1 DA: 04 MD:0Time Cycle 8R4: 0000 0010Fields not specified above have fixed values throughout or are unused: SH. Based on the register contents, the branch is taken. The data hazards are avoided, but due to the control hazard, the last two instructions are erroneously executed.510-18.IM IMC0CSCS10-19.*3:04AX3:04 DXDXDXDXDX7Z1(a) Branch if overflowR M P M L MAction Address MZ CA W DX D BS S W F S C MA B AX BX CS(b) Branch if greater than zeroR M P M L MAction Address MZ CA W DX D BS S W F S C MA B AX BX CS(c) Compare Less ThanR M P M L MAction Address MZ CA W DX D BS S W F S C MA B AX BX CS(a) PushR M P M L M(b) PopR M P M L MAction Address MZ CA W DX D BS S W FS C MA B AX BX CS10-23.*(a) Add with carryR M P M L MAction Address MZ CA W DX D BS S W FS C MA B AX BX CS(a) Subtract with borrowR M P M L MAction Address MZ CA W DX D BS S W FS C MA B AX BX CS9(a) Add Memory IndirectR M P M L MAction Address MZ CA W DX D BS S W FS C MA B AX BX CS(b) Add to memoryR M P M L MAction Address MZ CA W DX D BS S W FS C MA B AX BX CS10-25.*Memory Scalar Add (Assume R[SB] > 0 to simplify coding)R M P M L MAction Address MZ CA W DX D BS S W FS C MA B AX BX CSProblem Solutions – Chapter 1010-26.Memory Vector Add (Assume R[SB] > 0 to simplify coding)R M P M L MAction Address MZ CA W DX D BS S W FS C MA B AX BX CS10-27.(a)R[DR] ←(R[SA][31:24] + R[SB][31:24],R[SA][23:16] + R[SB][23:16],R[SA][15:8] + R[SB][15:8],R[SA][7:0] + R[SB][7:0])(b) The function unit requires an additional Add operation in which the carries entering bits 0, 8, 16, and 24 are set to 0. All potential condition codes produced by the operation, including carries from bits 7, 15, 23 and 31 are ignored.10-28.(a) For 16-bit words, the operation can produce a 128-bit result containing 128/16 = 8 minimum words.(b) For each SPE, there are 128/8 = 16 average bytes produced. Using the eight SPEs, 8 × 16 = 1286 average bytes can be produced.11。