基于VHDL的数字电路综合设计

- 格式:docx

- 大小:37.65 KB

- 文档页数:4

电子科技大学UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA数字逻辑设计实验报告实验题目:4B5B编码器学生:指导老师:一、实验容4B/5B编码是百兆以太网中线路层编码类型之一,该试验需要实现用5bit 的二进制数来表示4bit二进制数。

二、实验要求1、功能性要求:能够实现4B5B编码,即输入4bit数据时能输出正确的5bit编码结果。

2、算法要求:利用卡诺图对编码真值表进行化简,得出其逻辑表达式,并基于此进行硬件设计。

3、设计性要求:使用代码及原理图两种设计方式来进行设计。

采用基本门结构化描述。

能够编写Test Bench文件,并利用Modelsim进行仿真。

三、实验原理及设计思路1、实验原理:在IEEE 802.9a等时以太网标准中的4B:5B编码方案,因其效率高和容易实现而被采用。

这种编码的特点是将欲发送的数据流每4bit作为一个组,然后按照4B/5B编码规则将其转换成相应5bit码。

5bit码共有32种组合,但只采用其中的16种对应4bit码的16种,其他的16种或者未用或者用作控制码,以表示帧的开始和结束、光纤线路的状态(静止、空闲、暂停)等。

4B5B编码表如下:2、设计思路:(1)整体思路:对已知的编码真值表,首先利用卡诺图对其进行化简,得出其逻辑表达式,再用基本门结构将其实现。

(2)卡诺图与表达式:设输入的4位编码为:ABCD,输出的5位编码为:VWXYZ,则分别画出其卡诺图并得出表达式如下:1.V:V=A+B’D’+B’C 2.W:W=B+A’C’.3.X:X=C+A’B’D’4.Y:Y=A’B+AB’+C’D’+AC’.5.Z:Z=D(3)基本门结构设计:由上述表达式可见,用到的基本门有:非门、2输入与门、3输入与门、2输入或门、3输入或门、4输入或门,用not、and、or将其一一表示出即可。

四、程序设计.1、顶层模块:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity main isPort ( a : in STD_LOGIC;b : in STD_LOGIC;c : in STD_LOGIC;d : in STD_LOGIC;v : out STD_LOGIC;w : out STD_LOGIC;x : out STD_LOGIC;y : out STD_LOGIC;z : out STD_LOGIC);end main;architecture Behavioral of main is COMPONENT notiPORT(i : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT and2iPORT(i1 : IN std_logic;i2 : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT and3iPORT(i1 : IN std_logic;i2 : IN std_logic;i3 : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT or2iPORT(.i1 : IN std_logic;i2 : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT or3iPORT(i1 : IN std_logic;i2 : IN std_logic;i3 : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT or4iPORT(i1 : IN std_logic;i2 : IN std_logic;i3 : IN std_logic;i4 : IN std_logic;o : OUT std_logic);END COMPONENT;signal nota,notb,notc,notd,v1,v2,v3,w1,w2,x1,x2,y1,y2,y3,y4,vv,ww,xx,yy,zz : std_logic;begin--not--Inst_noti_nota: noti PORT MAP(i => a,o => nota);Inst_noti_notb: noti PORT MAP(i => b,o => notb);Inst_noti_notc: noti PORT MAP(i => c,o => notc);.Inst_noti_notd: noti PORT MAP(i => d,o => notd);--v--v1<=a;Inst_and2i_v2: and2i PORT MAP(i1 => notb,i2 => notd,o => v2);Inst_and2i_v3: and2i PORT MAP(i1 => notb,i2 => c,o => v3);Inst_or3i_vv: or3i PORT MAP(i1 => v1,i2 => v2,i3 => v3,o => vv);--w--w1<=b;Inst_and2i_w2: and2i PORT MAP(i1 => nota,i2 => notc,o => w2);Inst_or2i_ww: or2i PORT MAP(i1 => w1,i2 => w2,o => ww);--x--. x1<=c;Inst_and3i_x2: and3i PORT MAP(i1 => nota,i2 => notb,i3 => notd,o => x2);Inst_or2i_xx: or2i PORT MAP(i1 => x1,i2 => x2,o => xx);--y--Inst_and2i_y1: and2i PORT MAP(i1 => nota,i2 => b,o => y1);Inst_and2i_y2: and2i PORT MAP(i1 => a,i2 => notb,o => y2);Inst_and2i_y3: and2i PORT MAP(i1 => notc,i2 => notd,o => y3);Inst_and2i_y4: and2i PORT MAP(i1 => a,i2 => notc,o => y4);Inst_or4i_yy: or4i PORT MAP(i1 => y1,i2 => y2,i3 => y3,.i4 => y4,o => yy);--z--zz<=d;--not--Inst_noti_v: noti PORT MAP(i => vv,o => v);Inst_noti_w: noti PORT MAP(i => ww,o => w);Inst_noti_x: noti PORT MAP(i => xx,o => x);Inst_noti_y: noti PORT MAP(i => yy,o => y);Inst_noti_z: noti PORT MAP(i => zz,o => z);end Behavioral;2、非门:entity noti isPort ( i : in STD_LOGIC;o : out STD_LOGIC);end noti;architecture Behavioral of noti is begino <= not i;end Behavioral;3、2输入与门:entity and2i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;o : out STD_LOGIC);end and2i;architecture Behavioral of and2i is begino <= i1 and i2;end Behavioral;4、3输入与门:entity and3i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;i3 : in STD_LOGIC;o : out STD_LOGIC);end and3i;architecture Behavioral of and3i isbegino<=i1 and i2 and i3;end Behavioral;5、2输入或门:entity or2i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;o : out STD_LOGIC);end or2i;architecture Behavioral of or2i is begino<=i1 or i2;end Behavioral;6、3输入或门:entity or3i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;i3 : in STD_LOGIC;o : out STD_LOGIC);end or3i;architecture Behavioral of or3i isbegino <= i1 or i2 or i3;end Behavioral;7、4输入或门:entity or4i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;i3 : in STD_LOGIC;i4 : in STD_LOGIC;o : out STD_LOGIC);end or4i;architecture Behavioral of or4i isbegino<=i1 or i2 or i3 or i4;end Behavioral;五、仿真与硬件调试1、仿真:(1)顶层仿真:1.仿真文件:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY test1 ISEND test1;ARCHITECTURE behavior OF test1 IS-- Component Declaration for the Unit Under Test (UUT) COMPONENT mainPORT(a : IN std_logic;b : IN std_logic;c : IN std_logic;d : IN std_logic;v : OUT std_logic;w : OUT std_logic;x : OUT std_logic;y : OUT std_logic;z : OUT std_logic);END COMPONENT;--Inputssignal a : std_logic := '0';signal b : std_logic := '0';signal c : std_logic := '0';signal d : std_logic := '0';--Outputssignal v : std_logic;signal w : std_logic;signal x : std_logic;signal y : std_logic;signal z : std_logic;-- No clocks detected in port list. Replace <clock> below with -- appropriate port nameBEGIN-- Instantiate the Unit Under Test (UUT)uut: main PORT MAP (a => a,b => b,c => c,d => d,v => v,w => w,x => x,y => y,z => z);-- Stimulus processstim_proc: processbegina<='0';b<='0';c<='0';d<='0';wait for 100 ns;a<='0';b<='0';c<='0';d<='1';wait for 100 ns;a<='0';b<='0';c<='1';d<='0'; wait for 100 ns;a<='0';b<='0';c<='1';d<='1'; wait for 100 ns;a<='0';b<='1';c<='0';d<='0'; wait for 100 ns;a<='0';b<='1';c<='0';d<='1'; wait for 100 ns;a<='0';b<='1';c<='1';d<='0'; wait for 100 ns;a<='0';b<='1';c<='1';d<='1'; wait for 100 ns;a<='1';b<='0';c<='0';d<='0'; wait for 100 ns;a<='1';b<='0';c<='0';d<='1'; wait for 100 ns;a<='1';b<='0';c<='1';d<='0'; wait for 100 ns;a<='1';b<='0';c<='1';d<='1'; wait for 100 ns;a<='1';b<='1';c<='0';d<='0'; wait for 100 ns;a<='1';b<='1';c<='0';d<='1'; wait for 100 ns;a<='1';b<='1';c<='1';d<='0'; wait for 100 ns;a<='1';b<='1';c<='1';d<='1'; -- insert stimulus herewait;end process;END;2.仿真结果:(2)非门仿真:(3)2输入与门仿真:(4)2输入或门仿真:(5)3输入或门仿真:(6)4输入或门仿真:2、硬件调试:(1)管脚配置:NET "a" LOC = P6; #sb1NET "b" LOC = P141;NET "c" LOC = P136;NET "d" LOC = P129;NET "v" LOC = P122;NET "w" LOC = P123;NET "x" LOC = P124;NET "y" LOC = P125;NET "z" LOC = P126;(2)调试结果:如上图所示,4B码为“0000”,其对应的5B码为“11110”。

基于vhdl和multisim的病房呼叫系统数电课设病房呼叫系统是一种用于病房内患者呼叫护士的设备。

本文将介绍基于VHDL 和Multisim的病房呼叫系统的数字电路设计。

1. 系统概述病房呼叫系统是一种用于病房内患者呼叫护士的设备。

系统由患者端和护士端组成。

患者端包括呼叫按钮和显示屏,护士端包括显示屏和报警器。

当患者按下呼叫按钮时,护士端的显示屏将显示患者的呼叫信息,并触发报警器发出声音。

2. 系统设计系统的设计基于VHDL和Multisim。

VHDL用于编写数字电路的行为描述,Multisim用于模拟和验证电路的功能。

2.1 患者端设计患者端包括一个呼叫按钮和一个显示屏。

呼叫按钮用于患者发起呼叫请求,显示屏用于显示患者的呼叫信息。

2.1.1 呼叫按钮设计呼叫按钮是一个触发器,当患者按下按钮时,触发器输出逻辑高电平。

我们可以使用VHDL编写一个简单的触发器模块,如下所示:```vhdlentity CallButton isport (clk : in std_logic;button : in std_logic;call_req : out std_logic);end CallButton;architecture Behavioral of CallButton isbeginprocess(clk)beginif rising_edge(clk) thenif button = '1' thencall_req <= '1';elsecall_req <= '0';end if;end if;end process;end Behavioral;```2.1.2 显示屏设计显示屏用于显示患者的呼叫信息。

我们可以使用VHDL编写一个显示屏模块,如下所示:```vhdlentity Display isport (clk : in std_logic;call_req : in std_logic;display_msg : out std_logic_vector(7 downto 0) );end Display;architecture Behavioral of Display issignal counter : integer range 0 to 9 := 0;beginprocess(clk)beginif rising_edge(clk) thenif call_req = '1' thencounter <= 9;elsif counter > 0 thencounter <= counter - 1;end if;end if;end process;process(counter)begincase counter iswhen 0 =>display_msg <= "00000001"; -- 显示“呼叫”when 1 =>display_msg <= "00000010"; -- 显示“请稍候”when 2 =>display_msg <= "00000100"; -- 显示“正在处理”when 3 =>display_msg <= "00001000"; -- 显示“护士已派出”when others =>display_msg <= "00000000"; -- 不显示任何信息end case;end process;end Behavioral;```2.2 护士端设计护士端包括一个显示屏和一个报警器。

基于VHDL的数字电路设计数字电路是电子信息领域中最重要的一部分,控制着现代社会各种各样的设备的运行。

为了满足各种不同的应用需求,数字电路被设计成了多种多样的形态。

其中,基于VHDL的数字电路设计方式得到了广泛的应用。

VHDL是一种硬件描述语言,是用来描述数字电路的语言。

本文将着重探讨基于VHDL的数字电路设计的流程和步骤,以及在实际设计中的应用。

一、VHDL简介VHDL全称是VHSIC硬件描述语言(VHSIC Hardware Description Language),VHSIC即:超高速集成电路(Very-high-speed integrated circuit)。

VHDL是一种硬件描述语言,它是用来描述数字电路的语言,可以描述数字电路功能、电路结构和电路时序特性等。

在数字电路设计中,VHDL是最重要的一种设计语言。

VHDL是一种结构化的硬件描述语言,包括有三个层次:一是建模层次,主要是用户对数字电路的需求,这一层次不直接与具体的电路有关;二是结构化层次,是用户根据需求所建立的结构化的电路模型;三是行为层次,是用户描述数字电路的最终形态。

二、数字电路设计的流程数字电路设计的流程如下:1. 分析功能需求,确定电路功能和处理流程,针对不同的应用要求,从而确定数字电路的类型和规格。

2. 设计实现电路,采用FPGA(Field Programmable Gate Array)或ASIC (Application Specific Integrated Circuit)等芯片,使用VHDL编写代码,使用VHDL进行模拟验证,并对设计进行等效性检查。

3. 对电路进行综合,将VHDL代码转化为对应的生成目标电路的结构级综合器,主要用于对电路进行优化和管脚分配等方面的处理。

4. 进行电路设计验证,生成电路功能模拟信号,通过波形查看器、时钟分析器等工具进行验证测试。

5. 编写VHDL管理器,通过代码编写实现电路的管理和控制,包括对电路的自测试、故障诊断和运行状态监测等。

基于VHDL的矩阵键盘及显示电路设计摘要:为了有效防止机械式键盘按键抖动带来的数据错误,这里在Quartus ?开发环境下,采用VHDL 语言设计了一种能够将机械式4 ×4 矩阵键盘的按键值依次显示到8 个7 段数码管上的矩阵键盘及显示电路。

仿真结果表明,所设计的矩阵键盘及显示电路成功地实现了按键防抖和按键数据的准确显示。

以ACEX1K系列EP1K30QC208 芯片为硬件环境,验证了各项设计功能的正确性。

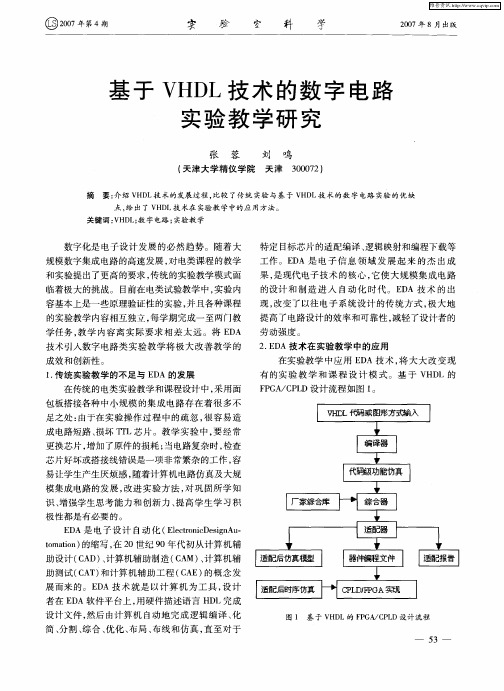

FPGA/ CPLD 在数字系统设计中的广泛应用,影响到了生产生活的各个方面。

在FPGA/ CPLD 的设计开发中,V HDL 语言作为一种主流的硬件描述语言,具有设计效率高, 可靠性好, 易读易懂等诸多优点。

作为一种功能强大的FPGA/ CPLD 数字系统开发环境,Altera 公司推出的Quart us ?,为设计者提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程,为使用V HDL 语言进行FPGA/ CPLD 设计提供了极大的便利。

矩阵键盘作为一种常用的数据输入设备,在各种电子设备上有着广泛的应用,通过7 段数码管将按键数值进行显示也是一种常用的数据显示方式。

在设计机械式矩阵键盘控制电路时,按键防抖和按键数据的译码显示是两个重要方面。

本文在Quart us ?开发环境下,采用V HDL语言设计了一种按键防抖并能连续记录并显示8 次按键数值的矩阵键盘及显示电路。

1 矩阵键盘及显示电路设计思路矩阵键盘及显示电路能够将机械式4 ×4矩阵键盘的按键值依次显示到8 个7段数码管上,每次新的按键值显示在最右端的第0 号数码管上,原有第0,6号数码管显示的数值整体左移到第1,7号数码管上显示,见图1 。

总体而言,矩阵键盘及显示电路的设计可分为4 个部分:(1) 矩阵键盘的行及列的扫描控制和译码。

该设计所使用的键盘是通过将列扫描信号作为输入信号,控制行扫描信号输出,然后根据行及列的扫描结果进行译码。

本文由风中思念7贡献pdf文档可能在WAP端浏览体验不佳。

建议您优先选择TXT,或下载源文件到本机查看。

一、概述VHDL与数字电路设计一、概述二、VHDL语言三、用VHDL设计逻辑电路传统数字电路设计方法 EDA设计方法 PLD器件设计流程文本设计输入—VHDL程序设计数字电子技术的基本知识回顾组合逻辑电路编码器、译码器、数据选择器、加法器、数值比较器等传统设计方法传统的设计方法是基于中小规模集成电路器件进行设计(如74系列及其改进系列、CC4000系列、 74HC系列等都属于通用型数字集成电路),而且是采用自底向上进行设计:(1)首先确定可用的元器件;(2)根据这些器件进行逻辑设计,完成各模块;(3)将各模块进行连接,最后形成系统;(4)而后经调试、测量观察整个系统是否达到规定的性能指标。

时序逻辑电路同步时序逻辑电路异步时序逻辑电路寄存器、移位寄存器、计数器、序列信号发生器 EDA设计方法EDA(Electronics Design Automation)即电子设计自动化技术,是利用计算机工作平台,从事电子系统和电路设计的一项技术。

EDA技术为电子系统设计带来了这样的变化:(1)设计效率提高,设计周期缩短;(2)设计质量提高;(3)设计成本降低;(4)能更充分地发挥设计人员的创造性;(5)设计成果的重用性大大提高,省去了不必要的重复劳动。

自顶向下的设计方法数字电路的EDA设计是基于PLD进行设计的,支持自顶向下的设计方法:(1)首先从系统设计入手,在顶层进行功能划分和结构设计;(2)然后再逐级设计底层的结构;(3)并在系统级采用仿真手段验证设计的正确性;(4)最后完成整个系统的设计,实现从设计、仿真、测试一体化。

传统设计方法 vs EDA设计方法传统设计方法自底向上手动设计软硬件分离原理图设计方式系统功能固定不易仿真难测试修改模块难移植共享设计周期长PLD器件设计流程(1)PLD开发系统包括硬件和软件两部分。

VHDL硬件描述语言与数字逻辑电路设计第三版课程设计本次课程设计旨在帮助大家深入理解VHDL硬件描述语言和数字逻辑电路设计的相关知识,提高大家的实践能力和设计能力。

本文将对课程设计的要求和实现方法进行详细说明。

课程设计要求本次课程设计要求大家完成一个基于VHDL的数字逻辑电路设计,包括以下要求:1.手动编写VHDL程序,对指定的数字电路进行仿真分析,并输出相应的波形图。

2.设计一个数字电路,要求该电路可完成特定的逻辑功能,例如加法器、多路选择器等。

3.基于现实的场景需求,完成一个实际的数字电路设计。

例如,实现一个音乐播放器控制器、机器人控制器等。

设计步骤步骤一:了解VHDL语言和数字逻辑电路设计原理在进行数字电路设计之前,需要先理解VHDL语言和数字逻辑电路设计原理。

VHDL语言是一种硬件描述语言,主要用于描述数字逻辑电路。

数字逻辑电路由基本的逻辑单元组成,包括与门、或门、非门等,通过组合这些逻辑单元可以实现更复杂的逻辑电路设计。

步骤二:选择仿真工具选择一款仿真工具进行仿真分析。

常见的仿真工具有ModelSim、Xilinx ISE 等。

步骤三:编写VHDL程序编写VHDL程序,对指定的数字电路进行仿真分析。

根据实际需要,可以选择不同的VHDL语言结构进行编写。

步骤四:仿真分析在仿真工具中进行仿真分析,根据VHDL程序模拟出相应的波形图。

步骤五:设计数字电路基于数字逻辑电路设计原理,设计出特定的数字电路。

需要首先确定电路所需要的逻辑功能,然后根据这个功能设计出合适的电路。

步骤六:实现实际场景需求参考现实的场景需求,设计出一个实际的数字电路,并进行调试测试。

VHDL程序编写规范在编写VHDL程序时,需要遵循一定的编写规范,以保证程序的可读性和可维护性。

1.命名规范:变量和信号的命名应具有较好的描述性,易于理解和记忆。

2.缩进规范:代码缩进应该统一,便于代码的阅读和理解。

3.注释规范:代码中应加入必要的注释,解释各个模块的功能和作用。

基于VHDL的数字电路综合设计

一、引言

数字电路设计是计算机科学中的一个重要领域,也是电子工程中的核心内容之一。

在数字电路设计中,经常会用到VHDL语言进行功能仿真和硬件实现,本文将介绍基于VHDL的数字电路综合设计。

二、VHDL语言简介

VHDL是VHSIC硬件描述语言(Very High Speed Integrated Circuit Hardware Description Language)的缩写,是一种描述数字系统的硬件设计语言。

VHDL支持复杂的设计和测试,并具有高度的可重用性和可扩展性,因此被广泛应用于数字电路设计。

VHDL语言包含结构体、函数、过程、运算符等元素,允许用户在设计过程中进行各种模拟和优化,支持从最基本的逻辑门直到复杂的微处理器设计。

同时,VHDL可以在不同的电脑平台上使用,并且可以与其他软件工具进行无缝集成。

三、数字电路综合设计流程

数字电路综合设计是指将高级语言的描述转换为符合硬件描述语言规范的电路图。

数字电路综合设计流程如下:

1.设计规范:对电路进行功能分析和描述,包括输入、输出、功能、时序等方面。

2.编写VHDL代码:根据设计规范编写VHDL代码,包括模块实例化、输入输出端口定义、内部信号定义、电路描述等。

3.逻辑综合:将VHDL代码进行逻辑综合,将代码转换为门级电路,通常采用的软件工具是DC综合器。

4.布局布线:将逻辑综合得到的门级电路进行布局布线,得到网表电路。

5.时序分析:对网表电路进行时序分析,保证电路能够在设定的时间内完成给定的操作。

6.物理综合:根据时序分析结果对网表电路进行物理综合,将电路布局在芯片上,并定义技术参数。

7.后仿真:对综合后的电路进行后仿真,验证电路设计是否符合原始设计要求。

四、综合设计工具的选择

数字电路综合设计需要使用多种工具,主要涉及到硬件描述语言编写工具、逻辑综合工具、布局布线工具、笔画校验工具和后仿真工具等。

常见的综合设计工具有:

1.VHDL编译器和仿真器:VHDL编译器和仿真器是支持VHDL语言的电路设计工具,可以实现VHDL语言的编写和电路仿真功能。

2.Xilinx ISE:Xilinx ISE是Xilinx公司推出的综合设计软件,可以进行逻辑综合、布局布线和后仿真等操作。

3.Mentor Graphics:Mentor Graphics是一家跨国公司,提供电子设备自动化设计解决方案,包括硬件描述语言编写工具、逻辑综合工具、布局布线工具、仿真器等。

四、VHDL的应用

VHDL语言在数字电路设计领域中应用广泛,主要表现在以下几个方面:

1.硬件描述语言:VHDL语言主要用于描述数字系统中的运算模块、控制单元、接口电路等硬件元素。

2.仿真和验证:VHDL语言可以进行系统建模和仿真检验,提供高级测试和验证功能。

3.硬件加速:VHDL可以在 FPGA、ASIC等硬件平台上使用,加速数字电路设计的速度和性能。

4.嵌入式系统设计:VHDL可以用于嵌入式系统设计,支持对复杂嵌入式电路进行描述和仿真。

五、结论

数字电路综合设计是数字电路设计的重要环节,基于VHDL语言进行综合设计具有广泛的应用前景。

在数字电路设计中,需要了解VHDL语言的语法规则和常用工具,根据设计规范进行电路描述,进行逻辑综合、布局布线和后仿真等操作。

VHDL语言的发展和应用为数字电路设计提供了强有力的支撑,也为信息产业的发展提供了新的思路和空间。