vlsi circuit design 10 multipliers hit

- 格式:ppt

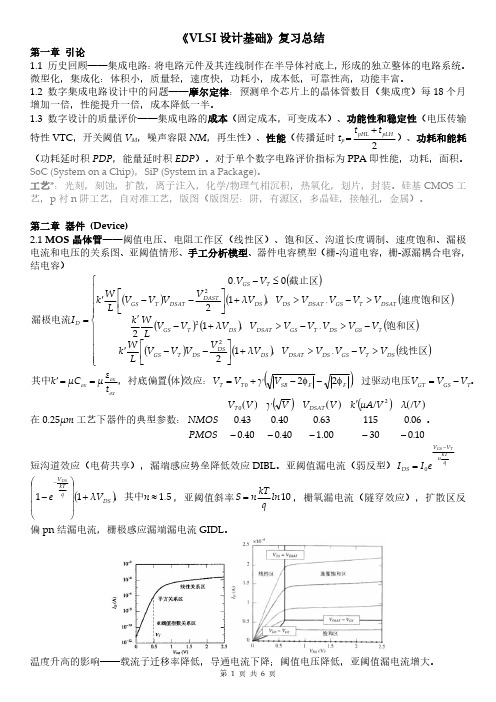

- 大小:379.00 KB

- 文档页数:15

详解Multisim 10仿真实验步骤时间:2010-06-22 04:19:17 来源:作者:一、实验目的熟悉并掌握Multisim10对单片机的仿真过程。

加深对单片机硬件以及软件理论知识的理解。

二、实验原理1、Multisim10美国国家仪器公司下属的ElectroNIcs Workbench Group在今年年初发布了Multisim 10。

新版的Multisim10,加入了MCU模块功能,可以和8051等单片机进行编程联调,该软件元件丰富,界面直观,虚拟仪器的逼真度达到了让人相当高的程度,是电子设计、电路调试、虚拟实验必备良件。

工程师们可以使用Multisim 10交互式地搭建电路原理图,并对电路行为进行仿真。

Multisim提炼了SPICE仿真的复杂内容,这样工程师无需懂得深入的SPICE技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更适合电子学教育。

通过Multisim和虚拟仪器技术,PCB设计工程师和电子学教育工作者可以完成从理论到原理图捕获与仿真再到原型设计和测试这样一个完整的综合设计流程。

下面将简单介绍一下Multisim10刚加进来的MCU模块的使用方法。

双击桌面上的multisim10图标,由于软件比较大,需要等待一定的时间才能进入以下界面(图一):图一Multisim10界面和Office工具界面相似,包括标题栏、下拉菜单、快捷工具、项目窗口、状态栏等组成。

标题栏用于显示应用程序名和当前的文件名。

下拉菜单提供各种选项。

快捷工具分为:文件工具按钮,器件工具按钮,调试工具按钮,这些按钮在下拉菜单中都有,并经常用到,现在放在工具栏里是为了方便使用。

项目窗口中的电路窗口是用来搭建电路的,Design Toolbox工具栏是用来显示全部工程文件和当前打开的文件。

状态栏用于显示程序的错误和警告,如果有错误和警告那还还需要重新修改程序。

直到没有错误为止才能正常加载程序。

在电路窗口的空白处点击鼠标右键,将出现如下菜单(图二):图二菜单包括:放置元件(place component)、连接原理图(place schematic)、放置图形(place graphic)、标注(place comment)等,这里我们最常用到的只有第一个放置元件:点击菜单中第一个选项或者按“CTRL+W”会出现以下元器件选择对话框(图三):图三在Group中选择我们需要的器件的类别,在Family中选择我们需要的器件,点击“OK”即可。

模拟及数模混淆集成电路设计剖析The Design and Analysis of the Analog and Mixed-SignalIntegrated Circuits课程代号:学时:36学分: 2开课学期:开科学院:教课方式:查核方式:预修课程:的课程秋天计算机学院讲解,课程试验,讲堂议论笔试,报告VLSI 设计、模拟电路等与微电子专业方向有关课程的地位、作用和任务本课程是微电子专业硕士学位研究生的一门重要的专业基础课。

VLSI 设计是微电子学科的一个重要领域,它波及到系统构造设计、微电子设计、工艺、制造、测试、封装等各个学科方向,拥有很强的实践应用特点。

本课程研究和议论硬件描绘语言的一般特点、硬件构造的建模方法、硬件构造的描绘、模拟考证及自动逻辑综合方法,使学生系统、全面地认识最初进的VLSI 设计方法-描绘、模拟考证、综合的设计方法,VLSI 设计及工艺的发展趋向,各设计阶段的优化设计思想及详细的优化方法,娴熟掌握VLSI 的设计描绘的编码风格。

教课内容和要求第一章VLSI 的设计流程及硬件描绘语言掌握 VLSI 设计的各个阶段、基本流程, VLSI 设计描绘与综合在 VLSI 设计实现过程中的地位和作用;认识硬件描绘语言的发展历史、几个常常使用的硬件描绘语言的基本特点。

第二章Verilog 语言的基本因素掌握 Verilog 语言的基本因素、基本模块构造。

认识采纳Verilog 语言进行硬件描绘的基本方法,硬件描绘的基本形式。

第三章硬件构造建模方法掌握给定硬件构造的硬件描绘方式,认识层次式设计方法及其硬件描绘方法。

第四章系统行为描绘掌握算法级、存放器传输( RTL )级、逻辑级行为功能的基本描绘方法,认识硬件描绘、逻辑模拟考证、逻辑综合的一致性方法。

第五章电路构造描绘掌握 MOS 电路级电路构造的描绘方法,议论电路信号的强度关系。

认识一般电路构造的建模方法。

第六章硬件描绘的基本编码风格详尽议论硬件描绘的编码风格,即用于模拟考证的描绘方式及用于综合的描绘方式的编码风格。

现代VLSI设计-基于IP核的设计第四版教学设计介绍现代VLSI(Very Large Scale Integration)设计是电子工程领域中的一个重要分支,指的是使用现代化的电路设计软件和设计流程来实现大规模集成电路的设计。

这种设计方法能够极大地提高电路设计的效率和准确性,同时也可以减少电路设计的成本。

近年来,随着计算机科学的蓬勃发展,IP(Intellectual Property)核的概念也越来越受到关注。

IP核是可重用的、自成体系的设计模块,可以用于较复杂的数字电路设计。

很多公司和团队使用IP核进行更高效、更可靠的VLSI设计。

本教学设计将重点介绍基于IP核的现代VLSI设计方法。

教学目标本教学设计旨在让学生掌握以下技能和知识:1.理解现代VLSI设计的基本概念和设计流程。

2.掌握IP核的设计和使用方法。

3.熟悉IP核库的结构和组成。

4.了解现代FPGA(Field Programmable Gate Array)芯片的原理和应用。

教学内容和方法教学内容本教学设计分为以下几个部分:1.现代VLSI设计概述2.IP核的设计和使用方法3.IP核库的结构和组成4.现代FPGA芯片的原理和应用教学方法本教学设计采用以下教学方法:1.讲授课程内容。

2.分组讨论和演示。

3.实验操作。

对于每个部分的具体教学方法和安排,下面给出详细说明。

1. 现代VLSI设计概述在这个部分,我们将对现代VLSI设计的基本概念和设计流程进行讲授。

主要内容包括:1.电路设计的基本流程。

2.现代VLSI设计的主要特点和优势。

3.现代VLSI设计的主要挑战和解决方案。

这个部分的教学方法是讲授,通过讲解让学生了解现代VLSI设计的基本概念和设计流程。

2. IP核的设计和使用方法在这个部分,我们将介绍IP核的设计和使用方法。

主要内容包括:1.IP核的基本概念和使用场景。

2.IP核的设计方法和过程。

3.IP核的验证和测试方法。

这个部分的教学方法是分组讨论和演示。

BrochureMore information from /reports/2175408/VLSI Digital Signal Processing Systems. Design and ImplementationDescription:Digital audio, speech recognition, cable modems, radar, high–definition television–these are but a few of the modern computer and communications applications relying on digital signal processing (DSP) and theattendant application–specific integrated circuits (ASICs). As information–age industries constantly reinventASIC chips for lower power consumption and higher efficiency, there is a growing need for designers whoare current and fluent in VLSI design methodologies for DSP.Enter VLSI Digital Signal Processing Systems–a unique, comprehensive guide to performance optimizationtechniques in VLSI signal processing. Based on Keshab Parhi's highly respected and popular graduate–levelcourses, this volume is destined to become the standard text and reference in the field. This text integratesVLSI architecture theory and algorithms, addresses various architectures at the implementation level, andpresents several approaches to analysis, estimation, and reduction of power consumption.Throughout this book, Dr. Parhi explains how to design high–speed, low–area, and low–power VLSI systemsfor a broad range of DSP applications. He covers pipelining extensively as well as numerous othertechniques, from parallel processing to scaling and roundoff noise computation. Readers are shown how toapply all techniques to improve implementations of several DSP algorithms, using both ASICs andoff–the–shelf programmable digital signal processors.The book features hundreds of graphs illustrating the various DSP algorithms, examples based on digitalfilters and transforms clarifying key concepts, and interesting end–of–chapter exercises that help matchtechniques with applications. In addition, the abundance of readily available techniques makes this anextremely useful resource for designers of DSP systems in wired, wireless, or multimedia communications.The material can be easily adopted in new courses on either VLSI digital signal processing architectures orhigh–performance VLSI system design.An invaluable reference and practical guide to VLSI digital signal processing.A tremendous source of optimization techniques indispensable in modern VLSI signal processing, VLSIDigital Signal Processing Systems promises to become the standard in the field. It offers a rich trainingground for students of VLSI design for digital signal processing and provides immediate access tostate–of–the–art, proven techniques for designers of DSP applications–in wired, wireless, or multimediacommunications.Topics include:* Transformations for high speed using pipelining, retiming, and parallel processing techniques* Power reduction transformations for supply voltage reduction as well as for strength or capacitancereduction* Area reduction using folding techniques* Strategies for arithmetic implementation* Synchronous, wave, and asynchronous pipelining* Design of programmable DSPs.Contents:Introduction to Digital Signal Processing Systems.Iteration Bound.Pipelining and Parallel Processing.Retiming.Unfolding.Folding.Systolic Architecture Design.Fast Convolution.Algorithmic Strength Reduction in Filters and Transforms.Pipelined and Parallel Recursive and Adaptive Filters.Scaling and Roundoff Noise.Digital Lattice Filter Structures.Bit–Level Arithmetic Architectures.Redundant Arithmetic.Numerical Strength Reduction.Synchronous, Wave, and Asynchronous Pipelines.Low–Power Design.Programmable Digital Signal Processors.Appendices.Index.Ordering:Order Online - /reports/2175408/ Order by Fax - using the form belowOrder by Post - print the order form below and send toResearch and Markets,Guinness Centre,Taylors Lane,Dublin 8,Ireland.Fax Order FormTo place an order via fax simply print this form, fill in the information below and fax the completed form to 646-607-1907 (from USA) or +353-1-481-1716 (from Rest of World). If you have any questions please visit/contact/Order Information Please verify that the product information is correct.Product Format Please select the product format and quantity you require:* Shipping/Handling is only charged once per order.Contact InformationPlease enter all the information below in BLOCK CAPITALSProduct Name:VLSI Digital Signal Processing Systems. Design and Implementation Web Address:/reports/2175408/Office Code:SC4975PH QuantityHard Copy (HardBack):USD 182 + USD 29 Shipping/HandlingTitle:MrMrsDrMissMsProf First Name:Last Name:Email Address: *Job Title:Organisation:Address:City:Postal / Zip Code:Country:Phone Number:Fax Number:* Please refrain from using free email accounts when ordering (e.g. Yahoo, Hotmail, AOL)Payment InformationPlease indicate the payment method you would like to use by selecting the appropriate box.Please fax this form to:(646) 607-1907 or (646) 964-6609 - From USA+353-1-481-1716 or +353-1-653-1571 - From Rest of World Pay by credit card:You will receive an email with a link to a secure webpage to enter yourcredit card details.Pay by check:Please post the check, accompanied by this form, to:Research and Markets,Guinness Center,Taylors Lane,Dublin 8,Ireland.Pay by wire transfer:Please transfer funds to:Account number833 130 83Sort code98-53-30Swift codeULSBIE2D IBAN numberIE78ULSB98533083313083Bank Address Ulster Bank,27-35 Main Street,Blackrock,Co. Dublin,Ireland.If you have a Marketing Code please enter it below:Marketing Code:Please note that by ordering from Research and Markets you are agreeing to our Terms and Conditions at /info/terms.asp。

VLSI设计基础第三版课程设计一、概述VLSI(Very Large-Scale Integration)是指集成电路技术中的一种技术,这种技术可以使几千个甚至几百万个电子元件集成在一个芯片上。

VLSI的发展使得集成电路的组织、设计、制造变得更加简单和经济。

因此,本课程旨在让学生了解VLSI的基础概念、设计方法和制造流程,同时通过实践,帮助学生掌握VLSI设计的基础知识和技能。

二、教学目标1. 理论目标•掌握VLSI设计的基本概念、原理和方法;•了解VLSI设计流程和制造工艺;•理解芯片设计中的时序、布局和布线等内容;•熟悉ASIC和FPGA的原理和应用。

2. 实践目标•熟悉VLSI设计工具的使用;•学会使用一些流行的VLSI仿真工具;•实现一个小型VLSI设计项目,加深对VLSI设计过程的理解。

第一部分:VLSI设计原理1.VLSI概述2.VLSI设计流程3.VLSI芯片设计的基本概念4.芯片布局设计5.芯片布线设计6.阵列设计基础7.数字信号处理器的设计8.软件定义电台的设计9.ASIC设计基础10.FPGA的基本原理和应用第二部分:VLSI设计实践1.FPGA的简单应用2.Verilog HDL及其模块化设计方法3.VHDL语言及其模块化设计方法4.门级元件的设计和实现5.组合逻辑和时序逻辑的设计6.测试的方法和技巧7.系统级仿真本课程将采用以下教学方法:1.理论授课:讲解VLSI设计的基本概念、原理和方法;2.实验实践:通过一些实践操作,将理论知识具体化;3.设计实践:要求学生进行一些小型VLSI设计项目。

五、教学要求1. 学生要求本课程面向电子信息类等专业的学生,建议先修读模拟电子技术、数字电子技术等课程。

因为本课程需要学生具备一定的电路基础知识和编程能力。

2. 教师要求本课程需要教师具备丰富的VLSI设计经验,熟悉VLSI设计流程和常用工具,能够灵活运用各种学习资源,耐心指导学生进行设计项目。

《VLSI电路设计》---项目设计传输门全加器设计指导老师:组长:目录一.项目设计方案 (2)1.1一位全加器简介: (2)1.2一位全加器的真值表: (2)1.3镜像CMOS全加器电路图: (3)1.4镜像CMOS全加器的棍棒图: (4)1.5镜像CMOS全加器的优化棍棒图: (4)1.6镜像CMOS全加器的欧拉路径: (5)1.7镜像CMOS全加器的网表: (5)二.项目设计完成情况 (7)1. HSPICE前仿真: (7)2.版图: (8)3.DRC/LVS/PEX完成情况: (8)4.HSPICE后仿真情况: (9)5.全加器面积及性能: (9)6.项目展望: (10)附录一 (10)附录二 (10)一.项目设计方案1.1一位全加器简介:全加器是算术运算电路运算中的基本单元,也是构成多位加法器的基本单元,介于加法器在算术运算电路当中的重要作用,使得全加器的设计显得十分重要。

通常情况下,我们采用两种结构构成全加器电路,一种是由两个半加器组成,另一种为镜像结构。

全加器的基本符号如图1-1所示。

其中,A 、B 为加法器的输入,Cin 进位输入,Sum 为输出,Cout 进位输出。

1-1 全加器基本符号全加器的逻辑表达式为:Cout=AB+BC in +AC inSum=ABC in +Cout(A+B+C in )1.2一位全加器的真值表:FULL ADDER A B Cin CoutSum1-2 全加器真值表1.3镜像CMOS 全加器电路图:1-3 镜像全加器电路图当D 为高时,!Cout 被置为Vdd,清除进位;当G 为高时,!输入 输出 A B Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1Cout被置为0,产生进位。

当P为1时,输入进位反向传递到!Cout,同时,可以分析求和电路,当A,B,Cin同时为0,!S为1,和为0;当A,B,Cin同时为1,!S为0,和为1;当A,B,Cin既有1也有0时,!S的输出由!Cout取反决定。

vlsi设计基础复习题VLSI设计基础复习题VLSI(Very Large Scale Integration)是集成电路设计的一种技术,它将数百万个晶体管集成到一个芯片上。

随着技术的进步,VLSI设计已经成为现代电子工程中不可或缺的一部分。

为了帮助大家复习VLSI设计的基础知识,下面将提供一些复习题。

1. 什么是VLSI设计?VLSI设计是指将大量晶体管集成到一个芯片上的过程。

它涉及到电路设计、物理设计和验证等多个方面,旨在实现高性能、低功耗和小尺寸的集成电路。

2. 请解释一下VLSI设计中的RTL是什么意思?RTL(Register Transfer Level)是指VLSI设计中的一种抽象级别。

它描述了数字电路中寄存器之间的数据传输和操作。

RTL级别的设计通常用硬件描述语言(如Verilog或VHDL)表示。

3. 请列举一些常用的VLSI设计工具。

常用的VLSI设计工具包括EDA工具(如Cadence、Synopsys和Mentor Graphics)、物理设计工具(如IC Compiler和Innovus)以及验证工具(如ModelSim和VCS)等。

4. 请解释一下VLSI设计中的时序和组合逻辑。

时序逻辑是指电路输出的状态取决于输入信号的顺序和时钟信号的触发边沿。

而组合逻辑是指电路输出的状态仅取决于当前的输入信号。

5. 请解释一下时钟和时钟频率在VLSI设计中的作用。

时钟在VLSI设计中用于同步电路的操作。

它通过提供一个统一的时间基准来确保电路中的各个部分按照预期的顺序和时序进行操作。

时钟频率表示时钟信号的频率,通常以赫兹(Hz)为单位。

6. 请解释一下VLSI设计中的布线和布局。

布线是指将逻辑电路中的信号线连接到芯片上的物理导线。

布局是指将电路中的各个组件(如晶体管和电容器)放置在芯片上的过程。

7. 请解释一下VLSI设计中的功耗优化技术。

功耗优化技术旨在减少集成电路的功耗,以提高电池寿命和减少散热需求。

RELEASE NOTESNI Circuit Design SuiteVersion 10.0These release notes contain system requirements for NI Circuit Design Suite 10.0,as well as information about product tiers, new features, documentation resources,and other changes since Multicap 9.0, Multisim 9.0, and Ultiboard 9.0.NI Circuit Design Suite includes the following familiar Electronics Workbenchsoftware products: NI Multisim, NI Ultiboard, and the NI Multisim MCU Module(formerly MultiMCU).ContentsInstalling NI Circuit Design Suite 10.0 (2)Minimum System Requirements (2)Installation Instructions (2)Product Activation (3)What’s New in NI Circuit Design Suite 10.0 (3)Mouse-Click Support for Interactive Components (3)Convergence Assistant (4)Increased Quality and Breadth of the Component Database (4)New Components from Leading Manufacturers (4)Generic Power Simulation Parts (4)Bipolar Sources (4)Graphical LCD (5)Single Symbol Representations of Standard Logic Components (5)Enhancements to Passive Components (5)Extended SPICE Modeling Capabilities (5)Parameterized SPICE models (5)Improved Support of Behavioral Sources (5)Support for BSIM 4 Parameters (6)Enhanced Data Visualization (6)Advanced Functionality of Static Probes (6)Add Traces to Grapher after Running Analyses (6)Display Initial Conditions on the Schematic (6)Current Probe Instrument (6)Enhanced Analysis Capabilities (6)Extended Language Support and File Management in the MCU Module (7)Improvements to Speed and Quality of NI Ultiboard (7)Advanced Options for Exported Data Interpolation (7)Miscellaneous Features (8)Unicode Characters (8)NI Installation and License Management (8)Product Tier Details (8)Documentation (14)Installing NI Circuit Design Suite 10.0This section describes the system requirements and installation procedures forNI Circuit Design Suite.Minimum System RequirementsTo run NI Circuit Design Suite 10.0, National Instruments recommends that yoursystem meet the following requirements:•Windows 2000 Service Pack 3 or later, or Windows XP•Pentium 4 class microprocessor or equivalent (Pentium III class minimum)•512 MB of memory (256 MB minimum)• 1.5 GB of free hard disk space (1 GB minimum)•Open GL® capable 3D graphics card recommended (SVGA resolution videoadapter with 800×600 video resolution minimum, 1024×768 or higherpreferred)•To develop custom LabVIEW based instruments for use in Multisim,LabVIEW 8.0.x or higher is requiredInstallation InstructionsThe NI Circuit Design Suite 10.0 installer installs all products in the suite:Multisim, Ultiboard, and the Multisim MCU Module.National Instruments recommends that you close all open applications before youinstall NI Circuit Design Suite.Unless you specify another location during installation, the NI Circuit DesignSuite installation program copies files to <Program Files>\NationalNI Circuit Design Suite Release Instruments\Circuit Design Suite10.0 after you complete thefollowing steps:1.Insert the NI Circuit Design Suite CD into the CD-ROM drive. If the CDstartup screen is not visible, select Run from the Windows Start menu and runsetup.exe from your CD.2.Follow the instructions in the dialog boxes.Product ActivationWhen you run a product in the NI Circuit Design Suite for the first time, it willprompt you to activate a license for that product.Note: To run the Multisim MCU Module, place a component from the MCUModule group on a Multisim circuit or open a Multisim file that contains acomponent from the MCU Module group.If you do not activate a valid license, the product will run in Evaluation Mode andcontinue to prompt you to activate a license on each subsequent run. EvaluationMode is valid for 30 days following the first run of the product.For information about how to activate your software product, please refer to theActivation Instructions for National Instruments Products Note to Users includedwith your NI Circuit Design Suite 10.0 package.What’s New in NI Circuit Design Suite 10.0This document describes the following new features ofNI Circuit Design Suite 10.0:•Mouse-Click Support for Interactive Parts•Convergence Assistant•Increased Quality and Breadth of the Component Database•Extended SPICE Modeling Capabilities•Enhanced Data Visualization•Extended Analysis Capabilities•Extended Programming and File Management in the MCU Module•Improvements to Speed and Quality of NI Ultiboard•Advanced Options for Exported Data Interpolation•Miscellaneous FeaturesMouse-Click Support for Interactive ComponentsNI Multisim 10.0 lets you use your mouse to control interactive componentsduring simulation. You can click on switches to toggle them, push keypad buttonswith the mouse, and adjust the value of the variable components, such asNational Instruments Corporation3NI Circuit Design Suite Release Notespotentiometers, with a slider bar. You may also continue to use keyboard controlsfor these devices.Convergence AssistantThe Convergence Assistant adjusts simulation settings when a "Time Step TooSmall" error occurs during interactive simulation. The assistant adjusts theminimum number of parameters required in order to allow convergence of thesimulation. The assistant adjusts the following parameters:1.Initial Condition2.TMAX3.RELTOL4.RSHUNT5.ITL16.Integration method7.GMINIncreased Quality and Breadth of the Component DatabaseNI Multisim 10.0 has a number of new additions and improvements to thecomponent database. These include: around 1,000 new components from leadingmanufacturers, generic power simulation parts, new bipolar sources, a GraphicalLCD, single symbol representations of standard logic components, andimprovements to passive components.New Components from Leading ManufacturersNI Multisim 10.0 has approximately 1,000 new components with models fromAnalog Devices, Texas Instruments, and Linear Technologies. These additionsinclude symbols, models, and IPC-standard landpatterns. Components includeoperational-amplifier, comparator, and voltage reference models.Generic Power Simulation PartsNI Multisim 10.0 includes models for all power simulation parts found in the"Switch-Mode Power Supply SPICE Cookbook" by Christophe Basso. Thesecomponents include Buck, Boost, Buck-Boost, and PWM controllers. Theirmodels include voltage and current mode controlled devices, and models foraverage and detailed transient operation.Bipolar SourcesNew bipolar pulse sources include both current and voltage sources.NI Circuit Design Suite Release Graphical LCDA Graphical LCD is available for users who purchase the MCU Module inconjunction with NI Multisim. The command system for the Graphical LCDfollows the Toshiba T6963C. The graphical LCD is a two-color device with 256 x256 pixel display resolution. This device supports three modes of operation:text-only, graphics-only, and mixed text and graphics.Single Symbol Representations of Standard LogicComponentsIn addition to the multi-section component representation of standard logiccomponents such as logic gates and flip-flops, the component database nowincludes single symbol representations of common components. Thesesingle-symbol representations show the power and ground pins of these devices.Enhancements to Passive ComponentsYou can now change the value of any resistor, capacitor, or inductor placed on theschematic without replacing it. You can also assign a landpattern to any passivecomponent. You can assign information about the type of component, for instancemetal-oxide, and this information propagates to the Bill of Materials. Thetolerance of the components is automatically available for Monte-Carlo and WorstCase analyses, and you can edit the tolerances in the spreadsheet.An advanced non-linear inductor model lets you define the inductor characteristicsbased on datasheet values.Extended SPICE Modeling CapabilitiesNI Multisim 10.0 introduces enhancements to its SPICE modeling capabilities,including parameters in SPICE subcircuit models, improved support of behavioralsources, and support for BSIM 4 parameters.Parameterized SPICE modelsYou may now define parameters in the .subcircuit line of SPICE macro-models inNI Multisim. The definition of parameters is as follows..subckt<subckt_name><node_list>PARAMS:param_name=value,...You may then use the parameter name in place of a value in the macro-model. Thevalue of the parameter is editable in the component dialog on the schematic.Improved Support of Behavioral SourcesBehavioral sources now support nested instances of IF statements.National Instruments Corporation5NI Circuit Design Suite Release NotesSupport for BSIM 4 ParametersNI Multisim 10.0 supports the standard BSIM 4 parameters for MOSFET models.BSIM 4 supports up to 400 parameters. More information about BSIM 4 isavailable at /~bsim3/bsim4.html.Enhanced Data VisualizationNI Multisim 10.0 includes a number of improvements to the way you configureand view results. These include: advanced functionality of the static probes, theability to add traces to the Grapher after running a simulation, the ability to displaythe initial conditions of components on the schematic, a current probe instrument,and improvements to the memory and register displays of MCUs.Advanced Functionality of Static ProbesPlaced (static) probes now include a reference designator, which allows you toselect another probe as a reference net. In previous versions of NI Multisim, allprobes referenced ground. You can also use probe reference designators to selectwhich traces to view in analyses.Add Traces to Grapher after Running AnalysesYou can add traces to the Grapher view after running an analysis, and select whattype of data you want NI Multisim to store.Display Initial Conditions on the SchematicYou can choose to display the initial conditions of capacitors and inductors on theschematic.Current Probe InstrumentThe current probe instrument is a virtual representation of a real current probe thatconnects to an oscilloscope. You connect one end of the probe to a net on theschematic and the other to the input to an oscilloscope. You can set the ratio ofamps to volts displayed on the instrument. Note that the units remain in volts onthe oscilloscope.Enhanced Analysis CapabilitiesNI Multisim 10.0 now allows you to evaluate more expressions before and afterrunning analyses. The definitions of the expressions are:1.avg(X) — Running average of the vector X2.avg(X, d) — Running average of the vector X over dNI Circuit Design Suite Release 3.envmax(X, n) — Upper envelope of the vector X where n is the number ofpoints on either side of a peak that must be less than the value for a peak to beidentified4.envmin(X, n) — Lower envelope of the vector X where n is the number ofpoints on either side of a peak that must be less than the value for a peak to beidentified5.grpdelay(X) — Group delay of X with results in seconds6.rms(X) — Running RMS average of vector X7.integral(X) — Running integral of vector X8.sgn(X) — The sign or signum of a real number. It is -1 for a negative number,0 for the number zero, and 1 for a positive number.Extended Language Support and File Management in the MCU ModuleThe MCU Module, formerly MultiMCU, supports C-code in addition to Assemblylanguage. It has a code manager that lets you use multiple files to define theoperation of the microcontrollers in the design. You can have header files and uselibraries. You can also load in externally assembled binary files and view them indisassembled format.Improvements to Speed and Quality of NI UltiboardNI Ultiboard 10.0 contains enhancements to the quality of the product that includeimprovements to the speed of trace-placment and the ability to select whether ornot to plate through-holes. Exported Gerber files do not contain mosaics in thepolygons. Quality improvements in the landpatterns include: pin mappings fromsymbols to IC pin-outs and landpattern shapes and sizes in the database. All newlandpatterns follow IPC standards.Advanced Options for Exported Data InterpolationWhen exporting simulation data from NI Multisim to other NI data formats suchas LVM or TDM files, you can choose the interpolation technique that best suitsthe signal. You can also control the interpolation method used when sendingsimulation data to NI LabVIEW based instruments running inside of NI Multisim.The interpolation methods include:•Coerce•Linear Interpolation•Spline InterpolationNational Instruments Corporation7NI Circuit Design Suite Release NotesMiscellaneous FeaturesSome of the other features added to the new suite include Unicode charactersupport and NI installation and license management.Unicode CharactersAll products in NI Circuit Design Suite 10.0 support Unicode characters. Thisfeature allows you to use Cyrillic and Asian fonts inside the products.NI Installation and License ManagementAll products in NI Circuit Design Suite adhere to the standard method used toinstall and activate National Instruments software. You can activate the softwareautomatically via the internet, or manually via a web browser, phone call, oremail.Product Tier DetailsThe following lists the schematic capture functionality available in MultisimStudent and Education editions:Functionality Student EducationCustomizable GUI X XScreen-capture utility X XComments on schematic X XCircuit annotations X XModeless part placement and wiring X XFast retrieval parts bins X XAuto and manual wiring X XVirtual wiring by node name X XRubber banding on part move X XFast auto-connect passives X XSubcircuits X X3-dimensional breadboarding X XVirtual NI ELVIS X XEmbedded questions - view and respond X XNI Circuit Design Suite Release Functionality Student EducationForward/Back annotation with Ultiboard X XCross-probing with Ultiboard X XBus-vector connect XSpreadsheet view XDesign constraints for layout XAdvanced search XZoom to selected part XCorporate database XUser defined fields XXSave components to database fromworkspaceMultiple circuits open XEmbedded questions - create and edit XElectrical rules check XGraphically mark no-connect pins XHierarchical designs XMultisheet designs XProject manager XReports - including bill of materials XPin and gate swap XExport to Mentor PADS layout XDevice library Partial CompleteMaximum components in design50UnlimitedNational Instruments Corporation9NI Circuit Design Suite Release NotesThe following lists the simulation functionality available in Multisim Student andEducation editions:Functionality Student EducationInteractive simulation X XFully mixed-mode A/D simulation X XStandard SPICE 3X5/XSPICE X XEnhanced model support X XPSPICE model simulation* X XSpeed/Accuracy tradeoffs X XSimulation advisor X XConvergence assistant X XVirtual, interactive, animated parts X XMouse click support for interactive parts X XRated components X XInsert faults into components X XMeasurement Probes X XComponent Wizard X XNI measurement data file sources X XNI measurement data file export X XX XNI LabVIEW VIs as instruments andsourcesMicrophone & speaker X XCircuit restrictions X XGrapher & Postprocessor X XRF design kit X XCircuit wizards XC-Code modeling XDescription box synced with simulation XLadder diagrams/components XModel makers XNI Circuit Design Suite Release Load and save simulation profiles XVirtual Instruments 2222Analyses1018Co-simulation of MCUs Add On Add On* Does not support all PSpice syntaxThe following lists the layout functionality available in Ultiboard Student andEducation editions:Functionality Student EducationPush and Shove trace placement X XReal-time & from copper ratsnest X XReal-time polygon update with voiding X XForward/Backward annotation X XCross-probing with Multisim X XReal-time DRC X X64 layers and 1 nanometer resolution X XComprehensive Footprint Wizard X XEnhanced 3D visualization with print X XUser annotations X XFull screen mode XGerber, DXF, IPC-D-356A, SVG output XDimensions on PCB and Landpatterns XDimensions in Database Manager XNet bridges X3D visualization inside circuit board XTurn off ratsnest for selected nets XGridless follow-me placement XLoad and save technology files XPolar Grids XNational Instruments Corporation11NI Circuit Design Suite Release NotesCustomizable layer viewing XSplit power-planes XKeep-in/Keep-out areas XPlace components in array XUnplace all components XRuler bar alignments and measurements XAuto-alignment XSave PCB Design as a component XPermanent grouping XPin & gate swapping XMultiple clearances XJump to Error XEquispace trace support XDifferential Impedance Calculator XTransmission Line Calculator XMicrovias XTest point insertion XAutomatic tear-dropping XPin necked trace support XAutomatic jumper insertion XCopy Route & Replica Place functions XIn-place footprint editor XMechanical CAD XExport 3D info in 3D IGES, DXF formats XCopper amount report XTest point report XCustomization of report generation XMultiple open documents XNI Circuit Design Suite Release National Instruments Corporation 13NI Circuit Design Suite Release NotesThe following lists the autorouting functionality available in Ultiboard Student and Education editions:Number of pins supported 3501,000Spreadsheet viewLimitedCompleteFunctionalityStudentEducationFully customizable cost factors X X Progressive Routing X X Interactive autorouting X X Constraint driven routingX X Manual pre-placement: components, vias, tracesX X Auto Block Capacitor recognition X X SMD mirroring X X Trace rubberbandingX X Follows keep-in/keep-out criteria X X Pin number limit3501,000Maximum number of layers24DocumentationNI Circuit Design Suite 10.0 includes a complete documentation set featuringprinted and electronic resources for your reference.The following printed and electronic resource is available:•Getting Started with NI Circuit Design Suite GuideThe following electronic resources are available in PDF files:•Multisim User Guide•Multisim Component Reference Guide•Multisim for Educators Guide•Multisim MCU Module User Guide•Ultiboard User GuideTo access the User Guides, select Start > All Programs > National Instruments >Circuit Design Suite 10.0 > Documentation and then select the file of interest.The following online help files are available from the installed software Helpmenu and from the Start Menu:•Multisim Education Edition Help File•Ultiboard Help FileTo access the Help Files, select Start > All Programs > National Instruments >Circuit Design Suite 10.0 > Documentation and then select the file of interest.The following online help files are available from the installed software Helpmenu:•Component Reference Education Edition Help File•Multisim Symbol Editor Help File•Multisim Title Block Editor Help FileNI Circuit Design Suite Release National Instruments, NI, , and LabVIEW are trademarks of National Instruments Corporation.Refer to the Terms of Use section on /legal for more information about National Instrumentstrademarks. Ultiboard is a registered trademark and Multisim and Electronics Workbench aretrademarks of Electronics Workbench. Other product and company names mentioned herein aretrademarks or trade names of their respective companies.374480A-01 Jan07© 2007 National Instruments Corp. All rights reserved.。

《VLSI电路设计》---项目设计传输门全加器设计指导老师:组长:目录一.项目设计方案 (2)1.1一位全加器简介: (2)1.2一位全加器的真值表: (2)1.3镜像CMOS全加器电路图: (3)1.4镜像CMOS全加器的棍棒图: (4)1.5镜像CMOS全加器的优化棍棒图: (4)1.6镜像CMOS全加器的欧拉路径: (5)1.7镜像CMOS全加器的网表: (5)二.项目设计完成情况 (7)1. HSPICE前仿真: (7)2.版图: (8)3.DRC/LVS/PEX完成情况: (8)4.HSPICE后仿真情况: (9)5.全加器面积及性能: (9)6.项目展望: (10)附录一 (10)附录二 (10)一.项目设计方案1.1一位全加器简介:全加器是算术运算电路运算中的基本单元,也是构成多位加法器的基本单元,介于加法器在算术运算电路当中的重要作用,使得全加器的设计显得十分重要。

通常情况下,我们采用两种结构构成全加器电路,一种是由两个半加器组成,另一种为镜像结构。

全加器的基本符号如图1-1所示。

其中,A 、B 为加法器的输入,Cin 进位输入,Sum 为输出,Cout 进位输出。

1-1 全加器基本符号全加器的逻辑表达式为:Cout=AB+BC in +AC inSum=ABC in +Cout(A+B+C in )1.2一位全加器的真值表:FULL ADDER A B Cin CoutSum1-2 全加器真值表1.3镜像CMOS 全加器电路图:1-3 镜像全加器电路图当D 为高时,!Cout 被置为Vdd,清除进位;当G 为高时,!输入 输出 A B Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1Cout被置为0,产生进位。

当P为1时,输入进位反向传递到!Cout,同时,可以分析求和电路,当A,B,Cin同时为0,!S为1,和为0;当A,B,Cin同时为1,!S为0,和为1;当A,B,Cin既有1也有0时,!S的输出由!Cout取反决定。