Quartus II 的bdf文件生成bsf 、v 、 vhdl文件

- 格式:docx

- 大小:135.34 KB

- 文档页数:2

彻底掌握Quartus II——基础篇2015-05-30下面介绍Quartus II 13.0最基础的日常使用方法,其它版本差别非常小。

如何新建工程就不说了,但是要注意,工程目录和工程名不要有中文和空格,还有,要有一个设计文件(如,.v、.vhd、.bsf文件)的名称要跟工程名一样,不然会有警告。

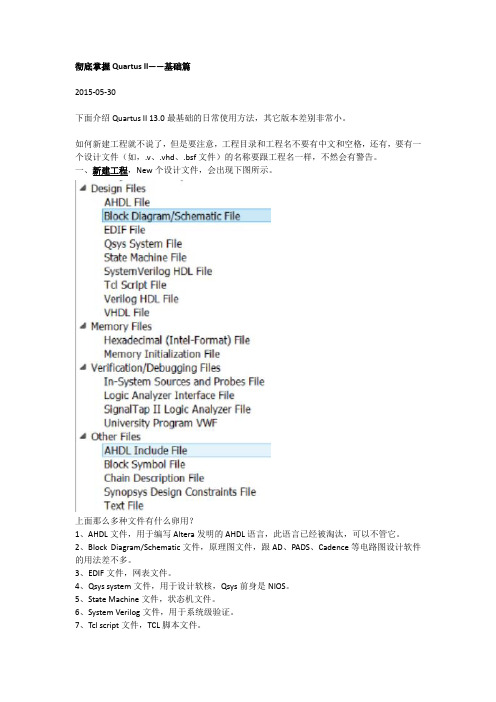

一、新建工程,New个设计文件,会出现下图所示。

上面那么多种文件有什么卵用?1、AHDL文件,用于编写Altera发明的AHDL语言,此语言已经被淘汰,可以不管它。

2、Block Diagram/Schematic文件,原理图文件,跟AD、PADS、Cadence等电路图设计软件的用法差不多。

3、EDIF文件,网表文件。

4、Qsys system文件,用于设计软核,Qsys前身是NIOS。

5、State Machine文件,状态机文件。

6、System Verilog文件,用于系统级验证。

7、Tcl script文件,TCL脚本文件。

8和9、常用的HDL文件(包括verilog和VHDL)10是十六进制文件,11是MIF文件,用于ROM或RAM的初始化。

12、Probe文件,用于观察FPGA内部某一信号,一般用Signaltap13、逻辑分析仪接口文件,暂时不知道有什么用。

14、VWF文件,用于调用quartus自带的仿真工具QSIM15、AHDL头文件,可以不管它。

16、原理图的Symbol文件,用于编辑原理图Symbol,跟你用电路图设计软件时,画原理图库差不多。

17、JTAG链描述文件,给一个或多个芯片下载代码时用的。

18、Synopsys约束文件,时序约束用的SDC文件。

19、txt文件。

就算quartus支持那么多种文件,但常用的没几个,一般是原理图.bdf文件或者纯文本的.v 或.vhd文件,就算后面需要用逻辑分析仪或者时序约束,也是可以用quartus自动给你生成的。

特别要注意一下,不同类型的文件,名字最好不一样。

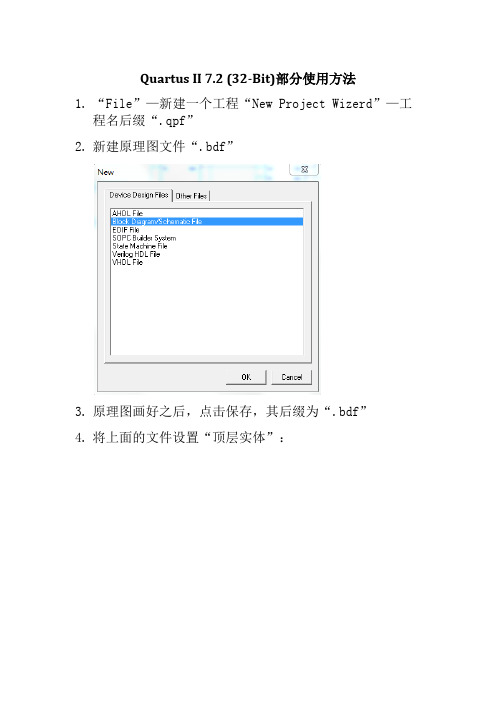

Quartus II 7.2 (32-Bit)部分使用方法

1.“File”—新建一个工程“New Project Wizerd”—工

程名后缀“.qpf”

2.新建原理图文件“.bdf”

3.原理图画好之后,点击保存,其后缀为“.bdf”

4.将上面的文件设置“顶层实体”:

5.接下来,编译:点击“Start Compliation”

6.把该文件(此处是半加器)变成一个元件符号(文件后

缀为.bsf),以备高层次的全加器设计所需

7.新建建波形(只对输出端进行波形输入设置)文件,

以.vwf存盘

8.选择要模拟的.bdf原理图文件,找寻以下按钮

9.点击上图所示按钮进入一下界面:

10.Simulation mode下拉按钮中选择“功能仿真”或者

“时序仿真”; Simulation input中选择波形文件;

点击“Generate Function Simulation Netlist”;点

击左下方Start,即可显示运行结果成功与否,图如下。

11.点击右下方按钮Report,即可生成波信仿真输出结果,

图如下:

12.。

Quartus Ⅱ入门教程(一个Verilog 程序的编译和功能仿真)Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

接下来我们对这种智能的EDA 工具进行初步的学习。

使大家以后的数字系统设计更加容易上手。

●快捷工具栏:提供设置(setting ),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

● 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

第二步:新建工程(file>new Project Wizard1 工程名称:2添加已有文件(没有已有文件的直接跳过next )3 选择芯片型号(我们选择MAX3000A 系列下的EPM3256AQC208-10芯片) (注:如果不下载到开发板上进行测试,这一步可以不用设置)4 选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None ,然后next )5 工程建立完成(点finish )第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序以实现一个与门和或门为例,Verilog描述源文件如下:module test(a,b,out1,out2);input a,b;Output out1,out2;assign out1=a&b;assign out2=a | b;endmodule然后保存源文件;第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis))点击确定完成语法检查第六步:(锁定引脚,点击工具栏的(pin planner ))(注:如果不下载到开发板上进行测试,引脚可以不用分配)双击location各个端口的输入输出第七步:整体编译(工具栏的按钮(start Complilation))第八步:功能仿真(直接利用quratus进行功能仿真)1将仿真类型设置为功能仿真(Assignments>setting>Simulator Settings>下拉>Function)2 建立一个波形文件:(new>Vector Waveform File )然后导入引脚(双击Name 下面空白区域>Node Finder>list>点击):接下来设置激励信号(单击>选择>Timing>Multiplied by 1)设置b 信号源的时候类同设置a 信号源,最后一步改为然后要先生成仿真需要的网表(工具栏processing>Generate Functional Simulation Netlist)接下来开始仿真(仿真前要将波形文件保存,点击工具栏开始仿真):实用标准文案文档观察波形,刚好符合我们的逻辑。

quartus⽣成的各⽂件含义Source files (always under source control)*.bdf Schematic*.bsf Symbols*.inc AHDL include*.lai Logic analyzer interface*.mif Memory init*.ptf SOPC file (old but recommended)*.qip MegaWizard IP*.sopc SOPC file*.tcl Scripts*.tdf AHDL source*.v Verilog source*.vhd VHDL source*.vwf Simulation stimuliAssignments & settings (always under source control)Name.cdf Programming chain settings编程设置⽂件Name.qdf Default assignments⾃动更新,保存全局assignments。

Name.qpf Project fileName.qsf Assignments (except timing)⾃动更新,也可以作为导⼊⽂件,但是⽂件名不要⼀样。

Name.sdc Timing constrains. This file should never be written directly by TimeQuest, since it might get randomly rearranged. Write to a separate file and copy-paste into main file. Name.srf Message supressionsOutput files (normally under source control)NOTE: Do not generate rbf or ttf files unless they are usedName.pof Programming fileName.rbf Programming file (normally not present)Name.sof Programming fileName.ttf Output in text format (normally not present)Special cases (consider source control)\db\*.* Improves quartus compilation time. Lots of files. If and only if incremental compilation will be used this should be under source control.\simulation\*.* This folder is for ModelSim. Quartus Simulator works without this folder. If ModelSim is used this should be under source control.Report files (normally not under source control)*.done Date*.qarlog Log of project archiving*.rpt Reports*.summary Report summariesGenerated files (never under source control)\timing\*.* No settings, just generated timing stuffName.qws GUI settings (window positions is a user rather than project option)*.cmp Component declarations*.dpf -⼏乎不变,为⼀个xml⽂件,当assignment pins时就会产⽣*.eqn Equations*.html -*.jpg Images generated by some megawizards?*.pin -*.ppf -Backup files (never under source control)*.bak Backup of single files*.qar Quartus archive补充:.v ------------------ verilog ⽂件.vhd ----------------- vhdl ⽂件.qpf ----------------- quartus ⼯程⽂件.vwf ----------------- ⽮量波形⽂件.bsf ----------------- 块符号⽂件.rpt ----------------- 报告⽂件.qsf ----------------- quartus配置⽂件.summary ----------- summary.pin ----------------- 引脚⽂件.sdo ----------------- delay.vo ------- ----------- gate level.qws ----------------- ⼯作区⽂件.pof ----------------- 编程对象⽂件.sof ------------------ SRAM对象⽂件.qar ------------------⼯程归档⽂件.SDK -----------------system development kit.mif ------------------memory initial file.ISO ----------------- 是ISO9660标准下的⽂件形式.srec ----------------S record.tdf ------------------text design file.gdf -----------------graphic desing fileHAL------------------Nios II运⾏库(或者称为硬件抽象层(HAL)) .tcl-------------------tool command language。

一、填空题1、目前国际上较大的PLD器件制造公司有Altera 和Xilinx 公司。

2、当前最流行并成为IEEE标准的硬件描述语言包括VHDL 和V erilog HDL 。

3、高密度可编程逻辑器件HDPLD包括EPLD 、CPLD 和FPGA 。

4、PLD从集成密度上可分为LDPLD 和HDPLD两类,其中HDPLD包括__EPLD_ ____、__ CPLD_____和___FPGA _____三种。

5、EDA设计流程包括设计准备、设计输入、设计处理和器件编程四个步骤。

6、图形文件的扩展名是_.bdf__;QuartusII所建工程的扩展名是_.qpf_;自建元件图形符号文件的扩展名_.bsf__;Verilog HDL所编程序的扩展名为__.v__ 。

7、图形文件的扩展名是 .bdf ;矢量波形文件的扩展名是.vwf ;自建元件图形符号文件的扩展名 .bsf 。

8、可编程逻辑器件的优化过程主要是对__速度__和___资源___的处理过程即时间优化和面积优化。

9、EDA设计输入主要包括__图形输入__、__ 文本输入和__ 波形__输入。

10、设计处理的最后一步是产生可供器件编程使用的数据文件,对CPLD来说是产生熔丝图文件即JEDEC文件,对于FPGA来说是产生位流数据文件Bitstream 。

11、EDA设计输入主要包括图形输入、文本输入和波形输入。

12、设计优化主要包括面积优化和速度优化。

13、Verilog HDL语言的扩展名为 .v 。

14、EDA的中文名称是电子设计自动化。

15、EDA仿真分为功能仿真又称前仿真、系统级仿真或行为仿真,用于验证系统的功能;时序仿真又称后仿真、电路级仿真,用于验证系统的时序特性、系统性能。

16、一般把EDA技术的发展分为_ __CAD____、__ CAE_____和___EDA____三个阶段。

17、阻塞型赋值符号为= ,非阻塞型赋值符号为<= 。

Quartus II 简单操作流程操作流程分五个步骤:设计准备——>设计输入——>设计处理——>设计校验——>器件编程具体在每个步骤要注意的事项:1.编辑插入元器件,在工作区双击即可弹出“insert symbol”对话框。

原理图文件扩展名为.bdf,VHDL设计文件扩展名为.vhd,Verilog HDL设计文件扩展名为.v选择目标器件,assignment | device…,可在family处选择max7000s,然后选择具体芯片型号EPM7128SLC84-152.编译仿真文件扩展名为.vwf设置顶层实体,尤其是同一个工程文件夹里有两个及以上实体设计文件时,project | set as top-level entity。

若编译后有错误,可双击错误,返回设计文件的错误处,然后修改、保存,并再次编译。

但要注意,排错时务必从第一个错误开始排除,且排一个错后就编译一次,因为后面的错误也许是因为前面的错误引起的。

3.仿真首先设置系统参数:仿真时间edit | end time…;网格大小edit | grid sizes…,建议设置200ns。

插入节点:在name栏双击,弹出insert node or bus 对话框,点“node finder…”,在弹出的对话框中,filter栏选择“pins:all”,然后点list,左下方框里就会出现前面编译过的设计文件的输入输出端口,然后根据需要选择即可。

单个选择,全部选择。

设置节点参数:排在上面的是高位,依次是低位,一般情况下,用得最多。

若输入端是总线,可设置成二进制、八进制、十进制和十六进制,可在点设置参数时选择,也可双击仿真区中的value at栏对应节点修改。

当节点位数多时,可全部选中要折叠的端口后单击右键点“group”折叠,反之点“ungroup”打开。

当同一个工程文件夹里有两个及以上实体仿真文件时,要在settings…里面的simulator选项卡中的simulation input 文本框中选择需要仿真的文件。

一、填空题1、目前国际上较大的PLD器件制造公司有Altera 和Xilinx 公司。

2、当前最流行并成为IEEE标准的硬件描述语言包括VHDL 和V erilog HDL 。

3、高密度可编程逻辑器件HDPLD包括EPLD 、CPLD 和FPGA 。

4、PLD从集成密度上可分为LDPLD 和HDPLD两类,其中HDPLD包括__EPLD_ ____、__ CPLD_____和___FPGA _____三种。

5、EDA设计流程包括设计准备、设计输入、设计处理和器件编程四个步骤。

6、图形文件的扩展名是_.bdf__;QuartusII所建工程的扩展名是_.qpf_;自建元件图形符号文件的扩展名_.bsf__;Verilog HDL所编程序的扩展名为__.v__ 。

7、图形文件的扩展名是 .bdf ;矢量波形文件的扩展名是.vwf ;自建元件图形符号文件的扩展名 .bsf 。

8、可编程逻辑器件的优化过程主要是对__速度__和___资源___的处理过程即时间优化和面积优化。

9、EDA设计输入主要包括__图形输入__、__ 文本输入和__ 波形__输入。

10、设计处理的最后一步是产生可供器件编程使用的数据文件,对CPLD来说是产生熔丝图文件即JEDEC文件,对于FPGA来说是产生位流数据文件Bitstream 。

11、EDA设计输入主要包括图形输入、文本输入和波形输入。

12、设计优化主要包括面积优化和速度优化。

13、Verilog HDL语言的扩展名为 .v 。

14、EDA的中文名称是电子设计自动化。

15、EDA仿真分为功能仿真又称前仿真、系统级仿真或行为仿真,用于验证系统的功能;时序仿真又称后仿真、电路级仿真,用于验证系统的时序特性、系统性能。

16、一般把EDA技术的发展分为_ __CAD____、__ CAE_____和___EDA____三个阶段。

17、阻塞型赋值符号为= ,非阻塞型赋值符号为<= 。