dsp 第13章-事件管理器

- 格式:ppt

- 大小:2.24 MB

- 文档页数:57

DSP控制技术课程教学大纲DSPContro1Techno1ogy学时数:48其中:实验学时:8学分数:3适用专业:普通本科电气工程与自动化专业一、课程的性质、目的和任务本课程是电气工程与自动化本科专业的的专业选修课。

数字信号处理己发展成一门理论与实践紧密结合的、应用日益广泛的、迅速替代传统模拟信号处理方法的、具有丰富器件支持的先进技术和方法。

DSP 器件是数字信号处理技术的最佳载体。

了解和掌握数字信号处理的实用技术对电气类学生而言,显得越来越重要且迫切。

数字信号处理器是微处理器技术发展的一个重要分支,处理的高速性和高集成度和在信号处理方面的卓越性能,使其在IT业界的用途越来越广。

本课程正是顺应这一发展方向而为电气工程与自动化本科专业学生开设的专业选修课。

本课程的目的是使该专业学生在数字信号处理器件及应用方面具有一定的基础知识,掌握DSP的结构、工作原理、特性、应用及发展方向,使该专业毕业生在工作中具有利用DSP 开发产品和解决实际问题的基本能力。

二、课程教学的基本要求本课程以TMS320F2xx为蓝本,剖析TMS320'C2000系列数字信号处理器的结构、内部资源、运行方式和指令系统、开发系统。

借鉴DSP系统实例,要求学生了解DSP的原理、用途和性能,了解软件集成开发环境的使用,掌握采用DSP进行工程项目开发的过程和软硬件调试工具的使用,熟练掌握使用汇编/C语言编写应用处理程序的方法。

本课程总学时为48学时,3学分,其中课堂教学为40学时,实验教学8学时,在第七学期完成。

三、课程的教学内容、重点和难点第零章绪论(4学时)基本内容:数字信号处理器的特点,DSP器件的发展,DSP器件的特点,DSP与其它微处理器的比较,DSP器件的应用领域,DSP应用系统设计,Mat1ab在DSP应用系统中的作用。

第一节数字信号处理器第二节专用DSP和DSP-IP核第三节通用DSP器件第四节小结基本要求:1. 了解数字信号处理器的特点2. 了解DSP器件的发展,DSP器件的特点;3. 了解DSP器件的应用领域,掌握DSP应用系统设计流程;4. 了解Uat1ab在DSP应用系统中的作用。

DSPBIOS设计指南详细DSP/BIOS是一款实时操作系统(RTOS),被广泛应用于嵌入式系统中。

本文将详细介绍DSP/BIOS的设计指南,帮助读者更好地使用和开发DSP/BIOS。

1.DSP/BIOS概述DSP/BIOS是德州仪器(Texas Instruments)开发的实时操作系统,特别适用于DSP(Digital Signal Processor)芯片应用。

DSP/BIOS提供了任务调度、任务管理、中断处理、资源管理等功能,提供了一种可靠和高效的方式来管理复杂的实时应用程序。

2.DSP/BIOS的优势DSP/BIOS具有以下优势:- 易于使用:DSP/BIOS提供了一套友好的API(Application Programming Interface),使用户可以方便地管理任务和资源。

-高度可配置:DSP/BIOS允许用户根据实际需求进行灵活的配置,以满足不同应用的要求。

-实时性能:DSP/BIOS通过优化的任务调度算法和中断处理机制,提供了快速响应和高效的实时性能。

3.DSP/BIOS的设计指南下面是一些DSP/BIOS的设计指南,供读者参考:3.1任务设计:-按照系统需求,将应用程序划分为多个任务。

每个任务负责独立的功能模块,可以利用DSP/BIOS的任务调度来管理任务的执行顺序。

-考虑任务的优先级和任务间的依赖关系,合理分配任务的优先级,确保高优先级任务能够及时得到处理。

-避免任务之间的竞争条件和资源冲突,可以使用DSP/BIOS的信号量和互斥体机制来保护共享资源。

3.2中断处理:-确保中断处理函数的执行时间尽量短,以避免影响其他任务的响应性能。

-合理设置中断的优先级和中断触发条件,确保关键中断的优先处理。

-对于高频率的中断,可以使用DSP/BIOS的中断优先级层次结构,将高优先级中断划分为多个子中断,以提高系统的可扩展性。

3.3资源管理:-确保所有任务和中断对资源的使用遵循一定的规则,防止死锁和资源冲突的发生。

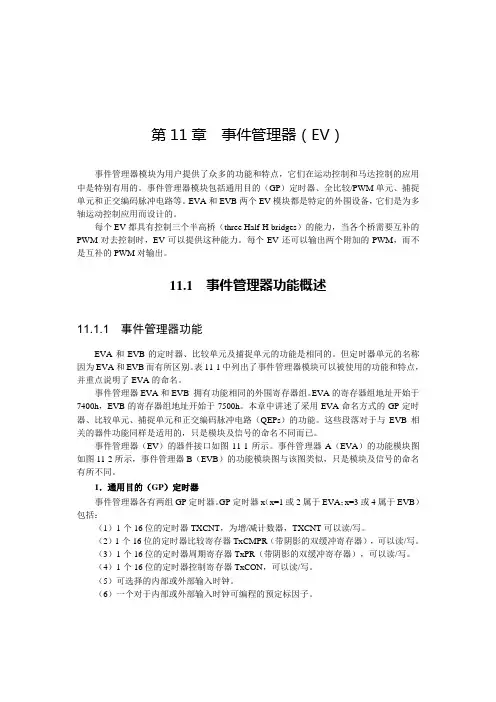

第11章事件管理器(EV)事件管理器模块为用户提供了众多的功能和特点,它们在运动控制和马达控制的应用中是特别有用的。

事件管理器模块包括通用目的(GP)定时器、全比较/PWM单元、捕捉单元和正交编码脉冲电路等。

EVA和EVB两个EV模块都是特定的外围设备,它们是为多轴运动控制应用而设计的。

每个EV都具有控制三个半高桥(three Half-H bridges)的能力,当各个桥需要互补的PWM对去控制时,EV可以提供这种能力。

每个EV还可以输出两个附加的PWM,而不是互补的PWM对输出。

11.1 事件管理器功能概述11.1.1 事件管理器功能EVA和EVB的定时器、比较单元及捕捉单元的功能是相同的。

但定时器单元的名称因为EVA和EVB而有所区别。

表11-1中列出了事件管理器模块可以被使用的功能和特点,并重点说明了EVA的命名。

事件管理器EVA和EVB 拥有功能相同的外围寄存器组。

EVA的寄存器组地址开始于7400h,EVB的寄存器组地址开始于7500h。

本章中讲述了采用EVA命名方式的GP定时器、比较单元、捕捉单元和正交编码脉冲电路(QEPs)的功能。

这些段落对于与EVB相关的器件功能同样是适用的,只是模块及信号的命名不同而已。

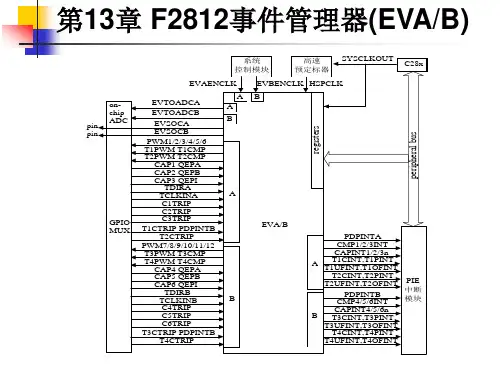

事件管理器(EV)的器件接口如图11-1所示。

事件管理器A(EVA)的功能模块图如图11-2所示,事件管理器B(EVB)的功能模块图与该图类似,只是模块及信号的命名有所不同。

1.通用目的(GP)定时器事件管理器各有两组GP定时器。

GP定时器x(x=1或2属于EVA;x=3或4属于EVB)包括:(1)1个16位的定时器TXCNT,为增/减计数器,TXCNT可以读/写。

(2)1个16位的定时器比较寄存器TxCMPR(带阴影的双缓冲寄存器),可以读/写。

(3)1个16位的定时器周期寄存器TxPR(带阴影的双缓冲寄存器),可以读/写。

(4)1个16位的定时器控制寄存器TxCON,可以读/写。

第二章6、代码安全模块CSM的作用是什么?提供代码保护,防止非法的程序拷贝。

当器件被保护的时候,只有从被保护的存储空间运行的代码可以访问(读或写)其他被保护存储空间中的数据。

从非保护的存储空间运行的代码不可以访问被保护存储空间中的数据。

7、如何由外部晶振或外部时钟频率确定CPU频率?周期包含12个时钟周期,一个机器周期就是0.5425μs。

一个机器周期一般是一条指令花费的时间,也有些是2个机器周期的指令,DJNZ,是双周期指令。

8、什么是DSP低功耗模式?DSP芯片可以工作在省点模式,使系统功能降低。

9、什么是看门狗定时钟?看门狗定时器实际上是一个计数器,一般给看门狗一个大数,程序开始运行后看门狗开始倒计数。

如果程序运行正常,过一段时间CPU应发出指令让看门狗复位,重新开始倒计数。

如果看门狗减到0就认为程序没有正常工作,强制整个系统复位。

13、281x DSP的中断是如何组织的?有哪些中断源?RINT:触发CPU的发送中断信号;XINT:触发CPU的接受中断信号。

第三章6、C28x DSP有哪些寻址方式?直接寻址、间接寻址、栈寻址、寄存器寻址。

7、直接寻址方式中,数据存储单元的地址如何形成?在直接寻址方式中,指令包括数据地址的低7位,这低7位地址作为偏移地址与DP或SP中德基地址组合形成完整的16位数据地址。

第四章3、说明. text段、. data段、. bss段分别包含什么内容?text段在内存中被映射为只读,但.data和.bss是可写的。

bss是英文Block Started by Symbol的简称,通常是指用来存放程序中未初始化的全局变量的一块内存区域,在程序载入时由内核清0。

BSS段属于静态内存分配。

它的初始值也是由用户自己定义的连接定位文件所确定,用户应该将它定义在可读写的RAM区内,源程序中使用malloc分配的内存就是这一块,它不是根据data大小确定,主要由程序中同时分配内存最大值所确定,不过如果超出了范围,也就是分配失败,可以等空间释放之后再分配。

学习DSP--EV事件管理器的学习已有 2 次阅读2011-8-31 15:09|关键词:学习一、事件管理器的功能每个EV模块(EVA和EVB)都具有2个通用定时器、3个比较单元、3个捕获单元以及1个正交编码。

通用定时器:就像秒表一样,是可以用来计时的,而且每个定时器还能产生1路独立的PWM 波形。

比较单元:主要功能就是用来生成PWM 波形的,EVA 具有3 个比较单元,每个单元可以生成一对(两路)互补的PWM 波形,生成的6 路PWM 波形正好可以驱动一个三相桥电路。

捕获单元:捕捉外部输入脉冲波形的上升沿或者下降沿,可以统计脉冲的间隔,也可以统计脉冲的个数。

正交编码电路:应该用的比较少,它可以对输入的正交脉冲进行编码和计数,它和光电编码器相连可以获得旋转机械部件的位置和速率等信息。

二、通用定时器和T1 相关的常用寄存器1. T1 周期寄存器T1PR 16 位2. T1 比较寄存器T1CMPR 16 位3. T1 计数寄存器T1CNT 16 位4. T1 控制寄存器T1CON 16 位5. 全局定时器控制寄存器A GPTCONA 16位T1 的常见输入信号1. 来自于CPU 的内部时钟2. 外部时钟输入TCLKINA,最大频率为器件自身时钟的1/4,也就是1/4*150M3. TDIRA/B,用于定时器的增/减计数模式4. 复位信号RESETT1 的输出信号1. 定时器的比较输出T1PWM_T1CMP2. 送给ADC 模块的AD 转换启动信号3. 下溢、上溢、比较匹配和周期匹配信号4. 计数方向指示定时器比较寄存器重载条件TCLD1 TCLD00 0 当计数器T1CNT值为00 1 当计数器T1CNT 值为0 或者等于周期寄存器1 0 立即载入1 1 保留当某个中断的标志位被置位,如果该中断已经使能,则会向PIE模块发送中断申请。

退出中段的时候,一定要手动清除外设中断标志位。

事件除了能够产生中断以外,还能够在事件发生的时候,产生一个ADSOC 信号,就是启动AD 转换的信号,这样可以周期性的去启动AD 转换。

实验报告一、实验目的和要求(必填)二、实验内容和原理(必填)三、主要仪器设备(必填)四、操作方法和实验步骤五、实验数据记录和处理六、实验结果与分析(必填)七、讨论、心得一、实验目的和要求(一)实验目的1.通过实验了解TMS320F2812事件管理器模块的原理和应用方法;2.学习利用事件管理器的通用定时器与全比较单元点亮8盏红灯。

(二)实验要求1.读懂老师提供的例程,运行例程观察实验结果进行验证;2.修改例程,点亮8盏红灯并实现亮度正弦分布的渐变交替闪烁;3.分析实验结果,并根据实验过程写出心得、体会。

二、实验内容和原理事件管理器(Event Manager,简称EV)是F2812的重要功能模块。

F2812 DSP具有两个功能完全相同的事件管理器EVA和EVB,它们都具有通用定时器、比较单元、捕获单元、正交编码电路,两者尽在命名上有所区别。

以其一为例,EVA模块具有2个16位的通用定时器(T1、T2)、3个比较单元、3个捕获单元和1个正交编码脉冲电路。

本次试验主要运用了通用定时器1的周期中断T1PINT、比较中断T1CMP和3个比较单元的比较中断CMP1INT、CMP2INT、CMP3INT。

通用定时器的中断事件是典型的外设中断,以T1为例,相关的中断有上溢中断、下溢中断、比较中断和周期中断。

当T1CNT的值与T1比较寄存器T1CMPR的值相等时,发生定时器T1的比较中断。

当发生比较匹配后,再过1个定时器时钟周期,则比较中断的标志位被置位。

当T1CNT的值与T1周期寄存器T1PR的值相等时,发生定时器T1的周期中断。

再过1个定时器时钟周期,则周期中断的标志位被置位。

置位后,如果该中断已经使能,则外设会立刻向PIE控制器发送中断请求。

在退出中断时要通过程序手动清除外设中断的标志位。

每个比较单元都有一个比较中断,当T1CNT的值和比较单元的比较寄存器CMPRx的值相等是,发生比较单元x的比较中断CMPxINT。

目录一引言与概述_________________________________________________________ 2 1.1 DSP介绍 _______________________________________________________________ 2 1.2DSP的应用:____________________________________________________________ 2 1.3问题描述_______________________________________________________________ 3 1.4 DSP2407简介 ___________________________________________________________ 3 1.5事件管理器的引脚说明___________________________________________________ 4 1.6比较单元_______________________________________________________________ 4 1.7 PWM基本原理__________________________________________________________ 4二系统总体设计与工作原理_____________________________________________ 6 2.1总体设计与分析_________________________________________________________ 6 2.2基本理论_______________________________________________________________ 7三各单元硬件设计及工作原理__________________________________________ 12四软件设计与说明____________________________________________________ 12 4.1程序文件说明__________________________________________________________ 12 4.2主程序(pwm.c) _________________________________________________________ 13 4.3向量表程序(vectors.asm) _________________________________________________ 14 4.4存储器配置(2407CMD.cmd) ______________________________________________ 14五调试结果及其操作说明______________________________________________ 15 5.1 CCS 集成开发环境_____________________________________________________ 15 5.2 CCS 的调试操作_______________________________________________________ 15六参考文献__________________________________________________________ 16一引言与概述1.1 DSP介绍数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

DSP名词解释DSP 专有名词解释AAbsolute Lister 绝对列表器ACC 累加器AD 模拟器件公司 Analog DevicesADC 数模转换器All-pipeline-Branching 全流水分支ALU 算数逻辑运算单元 Arithmetic Logical UnitAMBA 先进微控制器总线结构(ARM处理器的片上总线)Advanced microcontroller bus architectureANSI 美国国家标准局AP 应用处理器 Application ProcessorAPI 应用程序编程接口Application Programmable interface ARAU 辅助寄存器单元 Auxiliary Register Arithmetic Unit ARP 辅助寄存器指针/地址解析协议Address Resolution Protocol Archiver Utility 归档器公用程序ASIC 专用集成电路 Application Specific Integrated CircuitASP 音频接口 /动态服务器页面(Active Server Page)ASK 振幅调制BB0,B1 DARAM B0、B1 块双口随机存储器BDM 背景调试模式 Background Debug ModeBluetooth 蓝牙BEGIER 调试中断使能寄存器BOPS 每秒十亿次操作BOOT Loader 引导装载程序CC Compiler C编译器CALU 中央算术逻辑单元 Central Arithmetic Logical UnitCAN 控制器局域网 Controller Area NetworkCCS 代码调试器/代码设计套件 Code Composer StudioCDMA 码分多址 Code Division Multiple AccessCode Size 代码长度CLKX 发送时钟引脚CLKR 接收时钟引脚COFF 通用目标文件格式Common Object File Format Convolution 卷积Cost Efficient 成本效益Cost Revenue Analysis 成本收入分析Cross Reference List 交叉引用列表器CSM 代码安全模块 Code Security ModuleDDAG 地址发生器 Data Address GeneratorDAR 数据存储页面指针DARAM 双口随机存储器Double Access Random Access Memory DMSoC 达芬奇数字媒体片上系统DP (DPH:DPL) 数据页面指针寄存器 Data -page PointerDR 数据接收引脚DRR 数据接收寄存器 Data receive registerDRAB 数据读地址总线 Data Read Address BusDRDB 数据读数据总线 Data Read Data BusDRR 数据接收寄存器 Data receive registerDSC 数字信号控制器 Digital Signal ControllerDSK DSP初学者套件 DSP Starter KitDSP 数字信号处理/ 数字信号处理器Digital Signal Processing/Processor DSP/BIOS 小型嵌入式实时的操作系统DX 数据发送引脚DWAB 数据读地址总线 Data Write Address BusDWDB 数据写数据总线 Data Write Data BusEeCAN 增强型控制器局域网(增强型CAN总线)Enhanced Controller Area Network EV 事件管理器 Event Manager Event driven 事件驱动EVM 评估模块Evaluation Module EDMA 增强的直接存储器访问EMCV 嵌入式计算机视觉库Embedded Computer Vision Library EMIF 外部存储器接口 External Memory Interface Emulator 硬件仿真器———— Simulator 软件仿真器EOS 嵌入式操作系统 Embedded Operation SystemES 嵌入式系统 Embedded SystemETM 嵌入式跟踪宏单元 Embedded Trace MacrocellF—HFFT 快速傅里叶变换 fast fourier transformFFS 闪存系统文件 Flash file systemFinite Impulse Response Filter 有限长脉冲响应滤波器FPWR flash的功耗模式寄存器Flash Power Word Register FSM 有限状态机Finite State Machine FSR 接收帧同步引脚FSX 发送帧同步引脚GAL 普通阵列逻辑 Generic array logicGPIO 通用输入输出接口General Purpose Input Output Port GPT 通用定时器 General purpose timerGPRS 通用分组无线业务 General Packet Radio ServiceGUI 图形用户界面 Graphical User InterfaceHCD USB主机控制器驱动程序 HostController DriverHWI 硬件中断 Hardware InterruptHPI 主机接口 Host Port InterfaceIIBQ 指令缓冲队列 Instruction Buffer QueueIC 集成电路 Integrated CircuitICE 实时在线仿真 In-Circuit EmulatorIDE 集成开发环境Integrated Development Environment IDMA 内部直接存储器访问I^2C 内部集成电路 Inter Integrated CircuitIntegrated Preprocessor 集成预处理器Interrupt Redirect 中断重定向IPC 进程间通信 Inter Process CommunicationIRDA 红外线数据协会 Infrared Data AssociationISP 在线编程 In-System programmableISR 中断服务程序 Interrupt service routineISS 指令集模拟器 Instruction set simulatorJ—LJTAG 边界扫描接口 /联合测试行动小组 Joint Test Action Group LCD 液晶显示器 Liquid Crystal DisplayLibrary Build Utility 创建库工具Lowest power/MIPS 最低功耗LPM 低功耗模式 Low Power Module M—NMAC 媒体访问控制 Media Access ControlMBPS 每秒百万比特 Million Bits Per SecondMCU 单片机 Micro Control UnitMcASP 多通道音频串口 Multichannel audio serial portMcBSP 多通道缓冲接口 Multichannel Buffered Serial PortMFLOPS 每秒百万次浮点操作MIPS 每秒百万条指令 Million Instructions Per SecondMMC 多媒体卡 Multimedia CardMMR 内存映射式寄存器 Memory Map RegisterMMU 存储管理单元 Memory Management UnitMOPS 每秒百万条操作 Million Operation Per SecondMPU 嵌入式处理器/微处理器 Micro Processor UnitMSI 中规模集成电路 medium-scale integrationMSP 混合信号处理器 Mixed Signal ProcessorNFC 近场通信 Near Field CommunicationNTSC 国家电视标准委员会National Television Standard Committee Null-overhead 零开销OOCD 片上调试技术 On-chip debugging techniquesOEM 原始设备生产商(代工生产)Original equipment manufacturer OFDM 正交频分多路复用技术Orthogonal Frequency Division Multiplexing OLE 对象连接与嵌入Object linking and embeddingOMAP 开放式多媒体应用平台Opening Multimedia Application Platform OpenCv 开放计算机视觉库 Open computer vision libraryOSD 屏幕显示 On Screen DisplayOSC 晶体整荡器OTP 一次性可编程 One Time ProgrammablePP(PH:PL)乘积结果寄存器PAB 程序地址总线 Program Address BusPAL 可编程阵列逻辑 programmable array logicPAL 逐行倒相 Phase Alteration LinePAN 个人局域网 personal area networkPC 程序计数器 Program CounterPIE 外设中断扩展 Peripheral Interrupt ExpansionPIN 个人身份识别号 Personal Identification NumberPLD 可编程逻辑器件 Programable Logic DevicePLL 锁相环 Phase Locking LoopPMC 程序存储控制器 Program Memory ControllerPointer Arithmetic 定点运算PPM 脉冲相位调制 Pulse Position ModulationPRDB 程序读数据总线 Program Read Data BusPreemptive kernel 抢占式内核PREG 乘积存储器Process Manager 进程管理器Product Shifter 乘积移位器PWM 脉宽调制 Pulse Width ModulationRRBR 接收缓冲寄存器 Receive buffer registerRF 无线电射频 Radio FrequencyResource Manager and Process Manager 资源和进程管理器RISC 精简指令集 Reduced Instruction Set ComputingROM 只读存储器 Read Only MemoryRSR 接收移位寄存器 Receive Shift RegisterRTC 实时时钟 Real Time ClockRun Time Support Library 运行支持库Run Time Support Library DSP Algorithm Standard 运行支持库DSP运算法则标准SSARAM 单口随机存储器Single Access Random Access Memory SBSRAM 同步突发静态RAM Scan_Based Emulator 基于扫描的硬件仿真器SCI 串行通信接口Serial Communication InterfaceSCR 交换中心资源 Switched Central ResourceSD 安全数字卡 Secure Memory CardSDRAM 同步动态RAMShell Program 外壳程序Simulator 软件仿真器SIR 异步半双工的红外通信方式 Serial InfraredSOC 片上系统 System On ChipSource Inter_List Feature 源代码交叠工具SPI 串行外设接口 Serial Peripheral InterfaceSuper Harvard 超级哈佛结构SWI 软件中断 Software InterruptSWWSR 软件等待状态寄存器Wait for a status register software(供参考)System Crash 系统崩溃TTAP 测试访问口 Test Access PortTEC 错误传输计数器 Transmission error counterTFT 薄膜场效应晶体管 Thin Film TransistorTI 德州仪器 Texas InstrumentsTREG 临时寄存器TSIP 电信串行接口端口Telecommunication Serial Interface PortU-XUART 通用异步收发器Universal Asynchronous receiver Transmitter UWB 超宽带通信 Ultra wideband communications VLIW 超长指令字 Very Long Instruction WordVPBE 视频处理后端 Video Processing Back EndVPFE 视频处理前端 Video Processing Front EndVPSS 视频处理子系统 Video Processing Sub SystemWDT 看门狗定时器 Watchdog TimerWi-fi 一种无线方式互连技术 Wireless fidelityXDS 扩展开发系统 External Development SystemXARn(ARnH:ARn)(n取0—7)辅助寄存器XINTF 存储器外部扩展接口 External interfaceXSR 发送移位寄存器XT(T:TL)乘法单元被乘数寄存器 /暂存器数字12 - stage Pipeline 十二级流水线3C Computer Communication Consumer3G 第3代移动通信技术The 3rd Generation Telecommunication40-bit barrel shifter 40位桶形移位器。