五邑大学数电第8次课前作业

- 格式:doc

- 大小:33.00 KB

- 文档页数:1

青岛农业大学理学与信息科学学院数字电路课程设计报告设计题目多路智力竞赛抢答器的设计学生专业班级电子信息科学与技术学生姓名(学号)设计小组其他同学姓名(学号)指导教师完成时间 2012.6.3 实习(设计)地点信息楼2452012年6月3日多路智力竞赛抢答器的设计1设计目的随着各种智力竞赛越来越多,在答题的过程中一般要分为必答和抢答两种。

必答有时间的限制,到时间要警告。

而抢答则要求参赛者做好充分的准备,等主持人说完题目,参赛者开始抢答,谁先按钮,就由这个参赛者答题,但是很难确认谁先按的,因此使用抢答器来完成这一功能是很有必要的。

本设计是一个可供八个人抢答的多路抢答器。

可以显示优先抢者的序号,幷同时有音响提示。

幷具有倒计时功能。

当锁定时间到了的时候会有音响提示。

当一次抢答完毕,可由主持人按复位键重新开始下一次抢答。

2设计要求掌握抢答器的工作原理及其设计方法。

1.基本功能(1)设计一个智力竞赛抢答器,可同时供8名选手或8个代表队参加比赛,他们的编号分别是0、1、2、3、4、5、6、7,各用一个抢答按钮,按钮的编号和选手的编号相对应,分别是S 0-S 7。

(2)给节目主持人设计一个开关,用来控制系统的清零(编号显示数码管灭灯)和抢答的开始。

(3)抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,编号立即锁存,并在LED 数码管行显示出选手的编号,同时扬声器给出音响提示。

此外,要封存输入电路,禁止其他选手抢答。

优先抢答选手的编号一致保持到主持人将系统清零为止。

2.扩展功能(1)抢答器具有定时抢答的功能,且一次抢答的时间可以由主持人设定(如30S )。

当节目主持人启动“开始”键后,要求定时器立即减计时,并用显示器显示,同时扬声器发出短暂的声响,声响持续时间0.5S 左右。

(2)参赛选手在设定的时间内抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答时刻的时间,并保持到主持人将系统清零为止。

第9次 课前作业9-1分析图所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

(7分)解:从给定的电路图写出驱动方程为:(1分)⎪⎩⎪⎨⎧==++⊕=nn nn n n Q D Q D Q Q Q Q D 231223231)(将驱动方程代入D 触发器的特征方程D Qn =+1,得到状态方程为:(1分)⎪⎩⎪⎨⎧==++⊕=+++nn n n nn n n n Q Q Q Q Q Q Q Q Q 213112232311)(由电路图可知,输出方程为(1分)根据状态方程和输出方程,画出的状态转换图(2分)如图所示,时序图略。

状态转换图状态转换图如图,这是一个五进制计数器(1分),能够自启动(1分)。

9-2已知时序电路如图所示,假设触发器的初始状态均为“0”。

(9分) (1)写出电路的状态方程和输出方程。

(2)分别列出X=0和X=1 2种情况下的状态转换表,说明其逻辑功能。

答案(1)驱动方程:(1分)⎪⎩⎪⎨⎧===+==n n n n n n Q K Q J K X Q Q X Q Q J 12121121211 (2)电路的状态方程(1分)和输出方程(1分)为⎪⎩⎪⎨⎧+=+=++nn n n n n n n n Q Q Q Q Q Q Q Q X Q 12211212111 CP Q Q Z n n ⋅=21(2)X=0和X=1两种情况下的状态转换表如表所列,其逻辑功能:当X=0时,为2位二进制减法计数器(1分),可自启动(1分);当X=1时,为三进制减法计数器(1分),可自启动(1分)。

作出X=0的状态表:(1分)作出X=1的状态表:(1分)1 11 0 0 1 0 0Q 2 n+1 Q 1 n+1次 态 0 01 1 1 0 0 1Q 2 n Q 1 n 现 态 输 出 0 0 0 CPZ 1 00 1次 态 0 01 0 Q2 n Q 1 n现 态 输 出 0 0 Z Q 2 n+1 Q 1 n+19-3试分析如图所示的时序逻辑电路(9分)(1)写出各逻辑方程式 时钟方程(1分):CP0=CP ↑(时钟脉冲源的上升沿触发。

五邑大学试卷命题人:李阳审核人:试卷分类(A 卷或B 卷) B五邑大学试卷学期: 2012 至 2013 学年度第 1 学期课程:光电子技术课程代号: 010A1860 使用班级: AP10221、AP10222 姓名:学号:一、单选题:(50分,每小题2分)请将正确的答案填入下表中:1、一切能产生光辐射的辐射源都称为光源,下列光源中属于热辐射光源的是:(D )(A )LED ;(B )固体激光器;(C )金属卤化物灯;(D )卤钨灯。

2、国际照明委员会(CIE )根据对许多人的大量观察结果,确定了人眼对各种光波长的相对灵敏度,称为光谱光视效率或视见函数,在明视觉下,人眼最敏感的波长是(C )(A )450nm ;(B )550nm ;(C )555nm ;(D )650nm 。

3、一个光源发出频率为540?1012Hz 的单色辐射,若在一给定方向上的辐射强度为1/683 (W ?sr -1),则该光源在该方向上的发光强度为1个( D )。

(A )尼特;(B )勒克斯;(C )熙提;(D )坎德拉。

4、白炽灯与卤钨灯可以看作是灰体,是用钨丝做灯丝,其色温是在(B )K 左右。

(A )2300;(B )2800;(C )5500;(D )7000。

5、钠灯的泡壳内充的是( C )与金属钠滴。

(A )氧气;(B )氢氧混合气体;(C )氖氩混合气体;(D )氮气。

6、激光器一般由( D )组成。

(A )半导体材料、金属半导体材料和PN 结材料(B )固体激光器、液体激光器和气体激光器(C )电子、载流子和光子(D )激励能源、谐振腔和工作物质题号一二三四五六总分得分题号 1 2 3 4 5 6 7 8 9 10 答案题号 11 12 13 14 15 16 17 18 19 20 答案试卷编号得分7、热释电器件是由TGS、LiTaO3等热电晶体材料组成的,但不论哪种材料,都有一个特定温度,称居里温度。

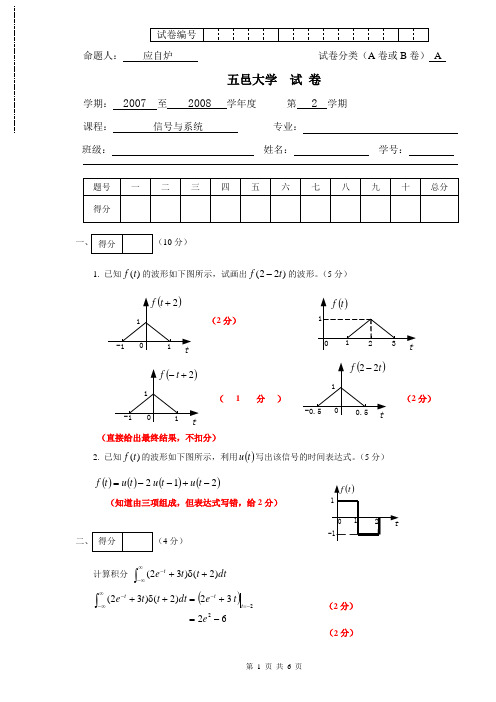

命题人: 应自炉 试卷分类(A 卷或B 卷) A五邑大学 试 卷学期: 2007 至 2008 学年度 第 2 学期 课程: 信号与系统 专业:班级:姓名: 学号:(10分)1. 已知)(t f 的波形如下图所示,试画出)22(t f -的波形。

(5分) (2分)(1分)(2分)(直接给出最终结果,不扣分)2. 已知)(t f 的波形如下图所示,利用()t u 写出该信号的时间表达式。

(5分)()()()()212-+--=t u t u t u t f(知道由三项组成,但表达式写错,给2分)(4分)计算积分dt t t e t )2()32(+δ+⎰∞∞--()6232)2()32(22-=+=+δ+-=-∞∞--⎰e t e dt t t e t t t(2分)(2分)已知描述连续时间LTI 系统的微分方程为()()()()t x dtt dx t y dt t dy +=+2 求该系统的单位冲激响应()t h 。

()21++=s s s H (3分) ()211+-=s s H (2分) ()()()t u et t h t2--δ= (3分)(用时域等其它方法求解,给出相应步骤分)(10分)一个连续时间LTI 系统的激励)(t x 和单位冲激响应)(t h 分别为()()t u t x =,()()t u e t h t3-=计算该系统的零状态响应()t y ZS 。

()s s X 1=(2分) ()31+=s s H (2分) ()()()()31+==s s s H s X s Y ZS (2分) ()⎪⎭⎫ ⎝⎛+-=31131s s s Y ZS (2分)()()()t u e t y t ZS 3131--=(2分)(用卷积等其它方法求解,给出相应步骤分)(1)设()tf 为带限信号,频带宽度为m ω,求信号()⎪⎭⎫⎝⎛t f t f 21,2的带宽(6分) 规律:时间压缩,频域扩展,时间扩展,频域压缩 (2分)()t f 2 时间压缩2倍,所以频域扩展2倍,即()t f 2的带宽为m ω2 (2分)⎪⎭⎫ ⎝⎛t f 21时间扩展2倍,所以频域压缩2倍,即⎪⎭⎫⎝⎛t f 21的带宽为m ω21 (2分)(2)已知信号如图所示,设其频谱函数为()ωF ,不要求()ωF ,求()0F (6分)根据 ()()dt et f F tj ωω-∞∞-⎰= (2分)得到()()828210=⨯⨯==⎰∞∞-dtt f F (2分 + 2分) )(3)求信号 ⎪⎩⎪⎨⎧><+=1, 0 1),cos 1(2)(t t t t f π 的傅里叶变换(6分)()()()t t G t f πcos 12+= (1分) ()()ωSa t G 422↔ (1分)()()()()[]πωδπωδπωπδπ++-+↔+2cos 1t (1分)()()()()()()()()[][]()()()()[][]()()()πωπωωπωδπωδωδωπωδπωδπωπδωπωπ++-+=++-+*=++-+*⨯=↔+=Sa Sa Sa Sa Sa F t t G t f 224222421cos 12 (3分) (用其它方法求解,给出相应步骤分)(每小题6分,18分)(1) 求函数()())(3223t u e e t f t t---=的拉普拉斯变换()s F ;()()()()2352332+++-=+-+=s s s s s s F ( 6分 )(2) 求函数()()86162++=s s s s F 的单边拉普拉斯反变换()t f ;()()()()()()42242421686162+++-+=++=++=s s s s s s s s s s F ( 4分 )(算错分子的系数扣2分)()())(24242t u e e t f t t --+-= ( 2分 )(3) 求函数()())1(252++=s s s F 的拉普拉斯反变换()t f 。

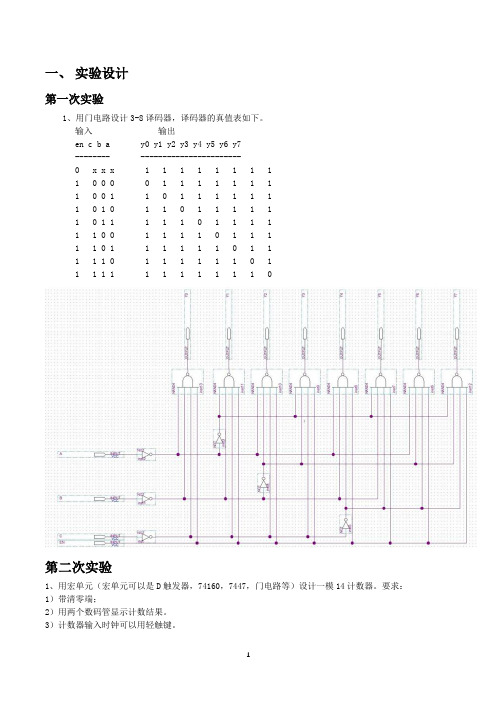

一、实验设计第一次实验1、用门电路设计3-8译码器,译码器的真值表如下。

输入输出en c b a y0 y1 y2 y3 y4 y5 y6 y7-------- -----------------------0 x x x 1 1 1 1 1 1 1 11 0 0 0 0 1 1 1 1 1 1 11 0 0 1 1 0 1 1 1 1 1 11 0 1 0 1 1 0 1 1 1 1 11 0 1 1 1 1 1 0 1 1 1 11 1 0 0 1 1 1 1 0 1 1 11 1 0 1 1 1 1 1 1 0 1 11 1 1 0 1 1 1 1 1 1 0 11 1 1 1 1 1 1 1 1 1 1 0第二次实验1、用宏单元(宏单元可以是D触发器,74160,7447,门电路等)设计一模14计数器。

要求:1)带清零端;2)用两个数码管显示计数结果。

3)计数器输入时钟可以用轻触键。

附录:模14计数器的真值表输入输出clk clr q4_q3q2q1q0------- -----------x 0 0_0000u 1 0_0001u 1 0_0010u 1 0_0011u 1 0_0100u 1 0_0101u 1 0_0110u 1 0_0111u 1 0_1000u 1 0_1001u 1 1_0000u 1 1_0001u 1 1_0010u 1 1_0011u 1 0_0000图2-1 模14计数器2、用LUT实现3输入异或门,要求画出完整的电路图(参照教材图2.29)。

输入异或门的真值表如下:输入输出c,b,a f----- -----000 0001 1010 1011 0100 1101 0110 0111 1图2-2 3输入异或门第三次实验——基于VerilogHDL的流水灯设计1、用VerilogHDL设计一模11二进制加法计数器,并仿真;表1 模11二进制计数器真值表输入信号输出信号clk clr_n q[3:0]------------ ------------x 0 0000;u 1 0001;u 1 0010;u 1 0011;u 1 0100;u 1 0101;u 1 0110;u 1 0111;u 1 1000;u 1 1001;u 1 1010;u 1 0000;------------------------------注:u表示时钟上沿module m11_counter(clk,clr_n,q); //定义模块名为m11_counterinput clk,clr_n; //定义1位的输入clk和clr_noutput reg[3:0] q; //定义4位的输出qalways@(posedge clk,negedge clr_n) //当clk上升沿或clr_n下降沿到来时触发beginif(!clr_n) q=0; //clr_n为0时q为0000elsebeginif(q==10) q=0; //判断q是否为1010,是则归0,否则自加1else q=q+1;endendendmodule2、用VerilogHDL设计4-11译码器,并仿真;表2 4-11译码器输入信号输出信号en code[3:0] y[10:0]------------- ------------------0 x 111_1111_11111 0000 000_0000_00011 0001 000_0000_00101 0010 000_0000_01001 0011 000_0000_10001 0100 000_0001_00001 0101 000_0010_00001 0110 000_0100_00001 0111 000_1000_00001 1000 001_0000_00001 1001 010_0000_00001 1010 100_0000_0000---------------------------------------module 4_11_decoder(en,code,y); //定义模块名为4_11_decoderinput en; //定义1位的输入eninput[3:0] code; //定义4位的输入codeoutput reg[10:0] y; //定义reg类型的11位输出yalways@(en,code) //当en或code有变化时触发beginif(!en) y=11'b111_1111_1111; //若en为0时,输出y的十一位全为1else//当en为1时,根据真值表调整与输入begin//code对应的输出ycase(code)4'b0000:y=11'b000_0000_0001;4'b0001:y=11'b000_0000_0010;4'b0010:y=11'b000_0000_0100;4'b0011:y=11'b000_0000_1000;4'b0100:y=11'b000_0001_0000;4'b0101:y=11'b000_0010_0000;4'b0110:y=11'b000_0100_0000;4'b0111:y=11'b000_1000_0000;4'b1000:y=11'b001_0000_0000;4'b1001:y=11'b010_0000_0000;4'b1010:y=11'b100_0000_0000;default:y=11'b111_1111_1111;endcaseendendendmodule3 [选做,可在实验时完成]用前面设计的计数器和译码器设计流水控制电路,控制11个LED灯的流动:计数器的clk输入接轻触开关,用于控制LED灯的移动;1 计数器增加加减法计数输入控制端;2 用lpm_counter设计从50MHz到10Hz的分频电路,为计数器提供时钟;3 其它;表3 模11加减法二进制计数器真值表输入信号输出信号clk clr_n up_dn q[3:0]------------------- ------------x 0 x 0000;u 1 1 q=q+1;u 1 0 q=q-1;------------------------------注:u表示时钟上沿//模11加减法二进制计数器module add_and_subtract_counter(clk,clr_n,up_dn,q);input clk,clr_n,up_dn; //定义一位的输入clk,clr_n,up_dnoutput reg[3:0] q; //定义reg类型的三位的输出qalways@(posedge clk,negedge clr_n) //当clk上升沿或clr_n下降沿到来时触发beginif(!clr_n) q=0; //当clr_n为0时,q的值为0else //否则up_dn控制加或减beginif(!up_dn) q=q-1; //up_dn为0时,q自减1else q=q+1; //up_dn为1时,q自加1endendendmodule3、(2)从50MHz到10Hz的分频电路//从50MHz到10Hz的分频电路//定义分频器模块counter_downmodule counter_down(clk_out,clk_in,reset);input clk_in,reset; //定义两个一位的输入clk_in(输入时钟),resetoutput reg clk_out; //定义一个reg型的一位的输出clk_out(输出时钟)integer cnt; //定义一个int型的cnt变量always@(posedge clk_in,posedge reset) //当clk_in或reset上升沿时触发beginif(reset) //当reset为1时清零begincnt<=0;clk_out<=0;elsebegin //reset为0时开始分频if(cnt==2_499_999)//分频从50MHz到10Hzbeginclk_out<=!clk_out;cnt<=0;endelse cnt<=cnt+1;endendendmodule第四次实验——基本电路设计+学号显示准备基于VerilogHDL的基本电路设计1、[基本]用VerilogHDL设计一个19人表决电路,输入为1时表示同意,输入为0时表示不同意。

命题人:徐秀平 审批人: 试卷分类(A 卷或B 卷) A五邑大学 试 卷学期: 2008 至 2009 学年度 第 一 学期 课程: 数字电路与逻辑设计 专业: 电子、计算机、交通 班级:姓名: 学号:一、 (包含8个小题,共38分)1.1 4分)CD D A BD B A Y +++=1.2 利用卡诺图化简下面逻辑函数,要求画出卡诺图,求得最简与或式。

(6分) ∑∑+=),),,,,,,,,,138(1514109763210(d m Y.3电路如图所示,①试写出输出端逻辑式;2,已知输入信号的波形,请对应画出输出端的波形。

(4分)A B Y BA Y1.4电路如图所示,其中所有的门均为TTL 门。

若已知各门的参数为I OH =0.25mA ,I OL =14mA ,I IH =0.05mA ,I IL =1.6mA ,试求能带多少个同类门?(4分)1.5电路如图所示,请写出输出Q 的特性方程,并画出对应时钟脉冲CLK 的输出Q 的波形(4分)1. 6电路如图所示,①说明它的容量是多少?②写出各片的地址范围(十六进制表示)。

(6分)QQSETCLRDA B CLKQDR 'TTL }N Y 00000tttttCLKDR 'A B1.7 CB555定时器接成的电路如图所示,若V CC =12V ,①试问CB555接成的是什么电路?②若输入电压v I 波形如图所示,试画出输出电压v 0的波形。

(6分)1.8 如图所示电路为4位倒T 型电阻网络D/A 转换器。

已知R=10K Ω,V REF =12V 。

当某位数字量d i =1时,开关接S i 接运算放大器的反相输入端,;当d i =0时,开关接S i 接地。

试求:①输出模拟电压v o 的范围;②求d 3d 2d 1d 0=1011时,对应的输出的模拟电压v o 值。

(4分)Ivov 0tt10V 5V二、 分析题(包含三道题,共32分)2.1由3线-8线译码器74HC138构成的逻辑电路如图所示,分析电路的逻辑功能,要求写出输出端逻辑式和真值表,说明电路有什么作用。

第2章 逻辑门电路习题

2-4-2 已知图中的门电路为74HC 系列CMOS 门电路,试指出各门电路的输出是什么状态(高电平、低电平、高阻态)?

2-4-3-1求图1所示电路Y 的表达式。

2-4-3-2在图题所示的CMOS 门电路中,要求实现下列规定的逻辑功能时,其连接有无错误?如有错误请改正。

K

C

B

C AB Y =1A Y C B A Y C ==+==2201时,时,A Y C B A Y C ==⊕==3310时,时,

图1

2-5-3在图由74系列或非门组成的电路中,试求门能驱动多少同样的或非门。

要求输出的高、低电平满足,。

或非门每个输入端的输入电流为

时输出电流的最大值为,时输出电流的最大值为。

的输出电阻可忽略不计。

命题人:徐秀平 审批人: 试卷分类(A 卷或B 卷) A五邑大学 试 卷学期: 2008 至 2009 学年度 第 一 学期 课程: 数字电路与逻辑设计 专业: 电子、计算机、交通 班级:姓名: 学号:一、(包含8个小题,共38分)4分)CD D A BD B A Y +++=利用卡诺图化简下面逻辑函数,要求画出卡诺图,求得最简与或式。

(6分) ∑∑+=),),,,,,,,,,138(1514109763210(d m Y.3电路如图所示,①试写出输出端逻辑式;2,已知输入信号的波形,请对应画出输出端的波形。

(4分)A B Y BA Y电路如图所示,其中所有的门均为TTL 门。

若已知各门的参数为I OH =,I OL =14mA ,I IH =,I IL =,试求能带多少个同类门?(4分)电路如图所示,请写出输出Q 的特性方程,并画出对应时钟脉冲CLK 的输出Q 的波形(4分)1. 6电路如图所示,①说明它的容量是多少?②写出各片的地址范围(十六进制表示)。

(6分)A DR'TTL NtR 'ACB555定时器接成的电路如图所示,若V CC =12V ,①试问CB555接成的是什么电路?②若输入电压v I 波形如图所示,试画出输出电压v 0的波形。

(6分)如图所示电路为4位倒T 型电阻网络D/A 转换器。

已知R=10K Ω,V REF =12V 。

当某位数字量d i =1时,开关接S i 接运算放大器的反相输入端,;当d i =0时,开关接S i 接地。

试求:①输出模拟电压v o 的范围;②求d 3d 2d 1d 0=1011时,对应的输出的模拟电压v o 值。

(4分)二、分析题(包含三道题,共32分)由3线-8线译码器74HC138构成的逻辑电路如图所示,分析电路的逻辑功能,要求写出输出端逻辑式和真值表,说明电路有什么作用。

(10分)S 11X 10X 1174HC 的功能表32S S '+'i Y 'i m '组合的最小项为012A A A i mv分析如图所示时序逻辑电路的功能,要求写出电路的驱动方程、状态方程、输出方程,画出状态转换图,说明是什么电路,并检查电路能否自启动。