数字电路-计数器-74LVC161

- 格式:pdf

- 大小:118.45 KB

- 文档页数:14

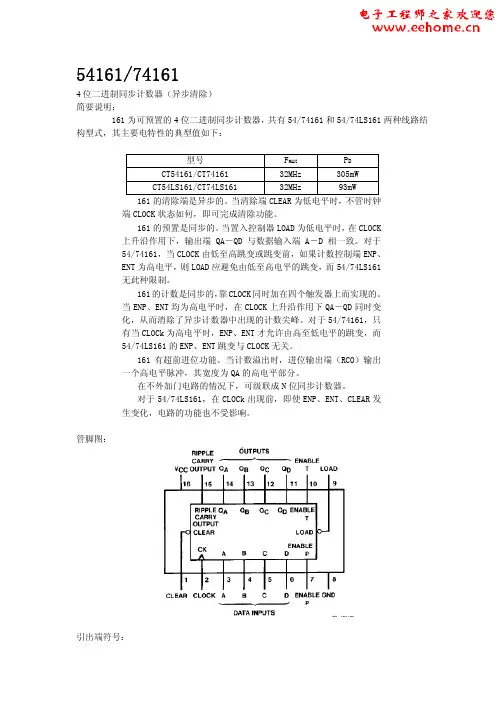

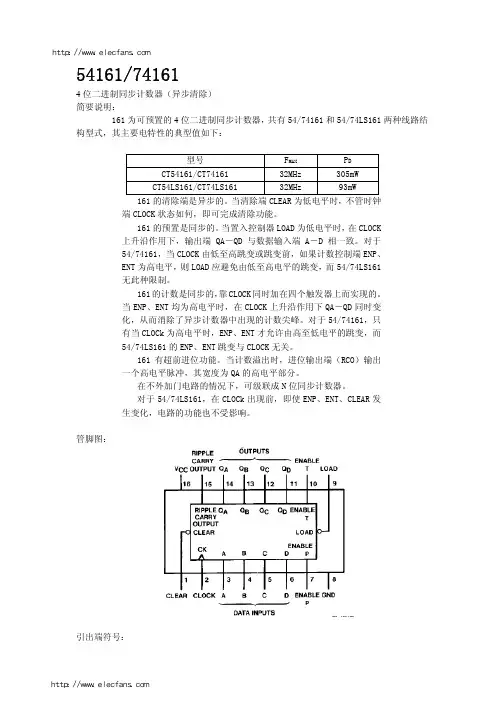

54161/741614位二进制同步计数器(异步清除)简要说明:161为可预置的4位二进制同步计数器,共有54/74161和54/74LS161两种线路结构型式,其主要电特性的典型值如下:型号 F MAX P DCT54161/CT74161 32MHz 305mWCT54LS161/CT74LS161 32MHz 93mW161的清除端是异步的。

当清除端CLEAR为低电平时,不管时钟端CLOCK状态如何,即可完成清除功能。

161的预置是同步的。

当置入控制器LOAD为低电平时,在CLOCK上升沿作用下,输出端QA-QD与数据输入端A-D相一致。

对于54/74161,当CLOCK由低至高跳变或跳变前,如果计数控制端ENP、ENT为高电平,则LOAD应避免由低至高电平的跳变,而54/74LS161无此种限制。

161的计数是同步的,靠CLOCK同时加在四个触发器上而实现的。

当ENP、ENT均为高电平时,在CLOCK上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。

对于54/74161,只有当CLOCk为高电平时,ENP、ENT才允许由高至低电平的跳变,而54/74LS161的ENP、ENT跳变与CLOCK无关。

161有超前进位功能。

当计数溢出时,进位输出端(RCO)输出一个高电平脉冲,其宽度为QA的高电平部分。

在不外加门电路的情况下,可级联成N位同步计数器。

对于54/74LS161,在CLOCk出现前,即使ENP、ENT、CLEAR发生变化,电路的功能也不受影响。

管脚图:引出端符号:PCO 进位输出端CLOCK 时钟输入端(上升沿有效)CLEAR 异步清除输入端(低电平有效)ENP 计数控制端ENT 计数控制端ABCD 并行数据输入端LOAD 同步并行置入控制端(低电平有效)QA-QD 输出端功能表:说明:H-高电平L-低电平X-任意↑-低到高电平跳变极限值电源电压------------------------------------------------7V输入电压54/74161-----------------------------------------5.5V54/74LS161---------------------------------------7VENP与ENT间电压54/74161-----------------------------------------5.5V 工作环境温度54×××------------------------------ -55~125℃74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃推荐工作条件:CT54161/CT74161 CT54LS161/CT74LS161单位最小额定最大最小额定最大54 4.5 5 5.5 5.5V 电源电压Vcc74 4.75 5 5.25 4.75 5 5.25输入高电平电压V IH 2 2 V54 0.80.7V 输入低电平电压V IL74 0.80.8输出高电平电流I OH-800-400 μA54 16 4mA 输出低电平电流I OL74 16 8时钟频率f CP0 25 0 25 MHzCLOCK 25 25ns 脉冲宽度tWCLEAR 20 20A-D、ENP 20 20ns 建立时间t setLOAD 25 20保持时间t H0 0 ns 时序图:逻辑图静态特性(T A 为工作环境温度范围)`161 `LS161参数测试条件【1】最小最大最小最大单位I IK =-12mA -1.5V IK 输入钳位电压 Vcc 最小I IK =-18mA-1.5 V54 2.4 2.5V OH 输出高电平电压Vcc=最小,V IH =2V ,V IL =最大, I OH =最大74 2.42.7V54 0.4 0.4V OL 输出低电平电压 V CC =最小,V IH =2V ,V IL =最大,I OL =最大740.40.5VA -D,ENP,CLEAR1 0.1I I 最大输入电压时输入电流 LOAD,CLOCk,ENT Vcc=最大 V I =5.5V (‘LS161为7V )1 0.2 mAA -D,ENP,CLEAR40 20LOAD 40 40 I IH 输入高电平电流 CLOCK,ENT Vcc=最大 V IH =2.4V (‘LS161为2.7V )80 40 μA A -D,ENP,CLEAR-1.6-0.4 LOAD -1.6 -0.8 V IL 输入低电平电流CLOCK,ENTVcc=最大 V IL =0.4V-3.2-0.8 mA 54-20-57-20 -100I OS 输出短路电流 Vcc=最大74-18-57-20 -100mA54 85 31IccH 输出高电平时电源电流Vcc=最大,LOAD 先接高电平,再接低电平,其余输入接高电平 74 94 31 mA54 91 32IccL 输出低电平时电源电流Vcc=最大,CLOCK 先接高电平,再接低电平,其余输入接低电平74101 32mA【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

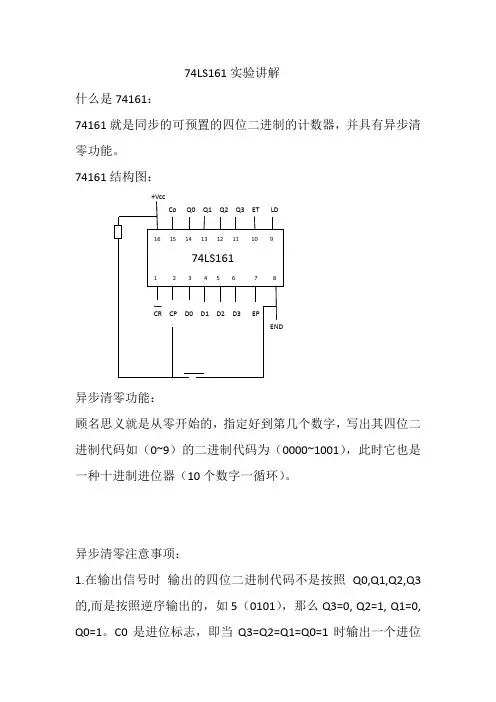

74LS161实验讲解什么是74161:74161就是同步的可预置的四位二进制的计数器,并具有异步清零功能。

74161结构图:异步清零功能:顾名思义就是从零开始的,指定好到第几个数字,写出其四位二进制代码如(0~9)的二进制代码为(0000~1001),此时它也是一种十进制进位器(10个数字一循环)。

异步清零注意事项:1.在输出信号时输出的四位二进制代码不是按照Q0,Q1,Q2,Q3的,而是按照逆序输出的,如5(0101),那么Q3=0, Q2=1, Q1=0, Q0=1。

C0是进位标志,即当Q3=Q2=Q1=Q0=1时输出一个进位信号1,否则输出0。

9(1010),Q3=1, Q2=0, Q1=0, Q0=1。

2.当循环到数字9时,由于Q3=1,Q0=1,那么瞬时就会把“0”信号传入CR,数字“9”会被瞬时清零,很难被看清(除非相应慢)。

想要克服这种情况,必须把9改成10(1010)。

这样才能看清9,然后再变成0。

异步清零(十进制(0~9))结构实验图:因为到数字10时(1010)Q3=1, Q2=0, Q1=1, Q0=0,发现只有当Q3=Q1=1时才开始循环,那么依照《电工与电子技术》第198页的表8-9。

只有让CR为”L”,即”0”才开始清零操作。

可以吧Q3和Q1与非的结果送入+Vcc C0Q0 Q1 Q2 Q3 ET LD同步并行:1.同异步清零相似,但是同步并行的功能比异步清零更完善,即可以恢复到初始状态。

2.与异步清零不同,因为异步清零只能从零开始,到某个位置回复到零在开始循环。

二同步并行并没有这种局限,它能从任意位置开始,然后到指定的位置,在恢复到一开始设置的位置循环。

注意事项:1.与异步清零相似的注意事项,在输入输出的,都是按照逆序输入输出的d3,d2,d1,d0. Q3,Q2,Q1,Q0.2.因为下图的LD没有带上非号,而课本第198表8-9上的LD上有非号,所以连接电路时还是注意一下。

H a r b i n I n s t i t u t e o f T e c h n o l o g y设计说明书(论文)课程名称:数字电子技术基础设计题目:同步加法计数器设计院系:航天学院自动化班级:0804101设计者:龚翔宇学号:24设计时间:【问题重述】试用同步加法计数器74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。

采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。

【设计思路】同步加法计数器74LS161为16进制计数器,要设计一个60进制的计数器,用555定时器设计多谐振荡电路,为同步加法计数器74LS161提供时钟输入信号并且用LED数码管显示结果。

要用16进制的161计时器设计60进制的,必须将其改装为10进制的。

将2个161联级,低位向高位进位6次,然后置零——即基本设计思路。

【基本元件】74LS161(两片)二4输入与非门74LS20(一片)555定时器【设计方案】555定时器提供时钟信号用555构成的多谐振荡器用555定时器构成的多谐振荡器如图所示。

555定时器可以方便的接成施密特触发器,在其基础上再改接成多谐振荡器。

o u可输出触发脉冲信号。

74LS161接为十进制计数器本方案使用置数法将161改装为十进制的计数器。

用如图所示。

D C B A Q Q Q Q 在经过1000时置数控制端LD =0,74LS161处在置数状态,D C B AQ Q Q Q 重新回到1111, 跳过了中间6个状态,由16进制转换为十进制计数器。

RCO 仍为进位输出。

对于低位芯片,全以0态作为起始状态,经过10-1=9状态后,产生置数控制信号1001。

这样,当第10个时钟的上升沿到达时,计数器置数为0000,每个芯片跳过剩余状态,成为10进制的计数器。

对于高位芯片,以取全0态作为起始状态,经过6个状态后,计数器清零,每个芯片跳过剩余状态,成为6进制的计数器。

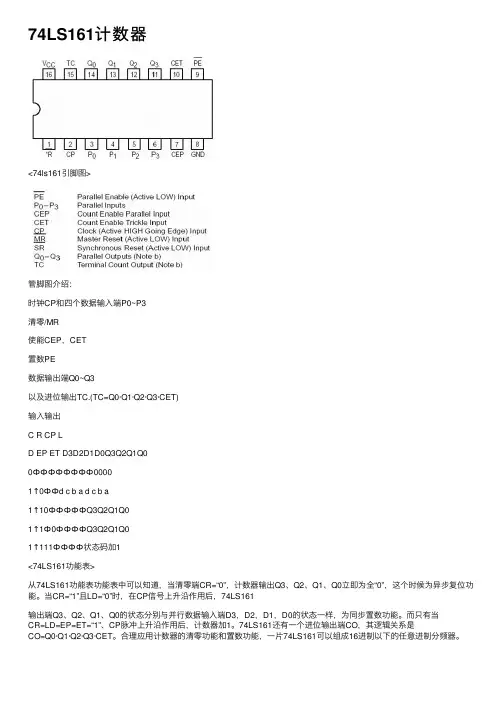

74LS161计数器

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输⼊端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC.(TC=Q0·Q1·Q2·Q3·CET)

输⼊输出

C R CP L

D EP ET D3D2D1D0Q3Q2Q1Q0

0ФФФФФФФФ0000

1↑0ФФd c b a d c b a

1↑10ФФФФФQ3Q2Q1Q0

1↑1Ф0ФФФФQ3Q2Q1Q0

1↑111ФФФФ状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0⽴即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作⽤后,74LS161

输出端Q3、Q2、Q1、Q0的状态分别与并⾏数据输⼊端D3,D2,D1,D0的状态⼀样,为同步置数功能。

⽽只有当

CR=LD=EP=ET=“1”、CP脉冲上升沿作⽤后,计数器加1。

74LS161还有⼀个进位输出端CO,其逻辑关系是

CO=Q0·Q1·Q2·Q3·CET。

合理应⽤计数器的清零功能和置数功能,⼀⽚74LS161可以组成16进制以下的任意进制分频器。

74ls161输出方程74LS161是一种四位二进制同步计数器,它有四个输入端(A,B,C和D)用于控制计数器的操作,以及一个时钟输入端(CLK)。

它的功能是根据锁存器反馈电路的当前状态对计数器的输出进行计数。

根据74LS161的功能,我们可以推导出以下输出方程。

首先,我们需要确定计数器输出的位数。

74LS161有4个输出端(Q0,Q1,Q2和Q3),因此我们需要一个4位的输出方程。

接下来,我们需要确定计数器的工作模式。

74LS161有两种工作模式:同步和异步。

在同步模式下,当时钟输入端接收到上升或下降沿信号时,计数器才进行计数。

而在异步模式下,计数器会忽略时钟信号,直接根据输入端的状态进行计数。

在同步模式下,我们可以使用JK触发器作为锁存器,每个触发器的输出将作为输出方程的一部分。

现在让我们推导计数器的输出方程:Q0=DQ1=D'•C+D•C'•BQ2=D'•C'•B•A+D•C'•B'•A'Q3=D'•C'•B'•A'其中D表示输入端D的状态(0或1)D'表示输入端D的反状态(1或0)C表示输入端C的状态(0或1)C'表示输入端C的反状态(1或0)B表示输入端B的状态(0或1)B'表示输入端B的反状态(1或0)A表示输入端A的状态(0或1)A'表示输入端A的反状态(1或0)通过以上方程,我们可以根据输入端的状态来确定74LS161计数器的输出。

这些方程描述了计数器在每个时钟周期中的状态转换。

请注意,这只是74LS161计数器输出方程的一个示例。

根据具体的设计要求和工作模式,方程可能会有所不同。

因此,在实际应用中,我们需要根据具体的设计要求来确定计数器的输出方程。

数电技术课程实践班级:12电本姓名:徐保霞学号:201292150118 指导教师:崔用明设计一个用74L161组成的14进加法计数器一、摘要:本设计主要是对四位二进制同步计数器74L161(异步清除)的同步预置控制端进行分析设计,使74LS161能克服触发器的工作速度的差异情况以及竞争冒险现象,实现了使同步预置信号能够持续足够长的时间,从而使74LS161能够从0000这一状态复位变为1101状态,成功得竞争结果,实现十四进制计数器的设计。

英文摘要:This design is mainly to four binary synchronous counter 74 L161 (asynchronous clearance) analyze the synchronous reset control end of the design, make a 74 ls161 can overcome the trigger the differences of working speed and competitive adventure phenomenon, has realized the synchronous preset signal can be sustained long enough, so that 74 ls161 can this state is reset to 0000 from 1101, a competition to succeed as a result, achieve 14 into the design of the system counter.关键词:计数器、同步预置二、设计要求1)熟练掌握加法计数器、74L161的基本概念。

2)实现14进加法计数器的设计3) 掌握并分析结果三、设计步骤1、电路组成框图(图1-1)图1-12、电路原理图(图1-2)图1-23、元器件选择74L161、与非门、数码管4、参数的设计计算设0000为预置数,则十四进制加法计数器的有效态为0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100、1101(图1-3)图(1-3)将输入端的数据d3d2d1d0=0000设为预置数,在输入时钟脉冲CP上升沿的作用下,EP、ET、R D接高电平,当输出端Q l输出为低电平时接与非门,此时Q l 输出为高电平,与Q3 Q2 Q0再通过一个与非门,此时“0”接入L D,实现R D=1、L D=0,达到设计要求输出为预置数0000。

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0Q3 Q2Q1Q0

0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 0

1 ↑ 0 Ф Ф d c b a d c b a

1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·C ET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LD EP ET D3D2D1D0Q3 Q2Q1Q00 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表〉从74LS161功能表功能表中可以知道,当清零端CR=“0",计数器输出Q3、Q2、Q1、Q0立即为全“0",这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1"、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

利用74LS161设计十进制计数器

1 设计要求

利用74LS161设计十进制计数器

1)要求写出设计过程,绘制电路原理图,并进行实验验证。

2)利用数码管和逻辑电平指示灯显示结果,记录计数器输出结果。

3)根据数码管和逻辑电平指示灯的显示结果绘制74LS161时钟和输出端波形。

2 集成计数器74LS161

TTL 型可预置4

位二进制数的同步加法计数器

U

2 集成计数器74LS161

74LS161功能表

3 设计过程

D

清零法构成十进制计数器电路原理图

3 设计过程

清零法构成十进制计数器电路原理图

D 0000000100100011010001010110011110100000

异步清零

10001001

3 设计过程

D

置数法构成十进制计数器电路原理图

3 设计过程

置数法构成十进制计数器电路原理图

D 00000001001000110100010101100111

0000

同步置数10001001

4

实验验证

U141312111098

12

34567

4 实验验证

十进制计数器波形图。