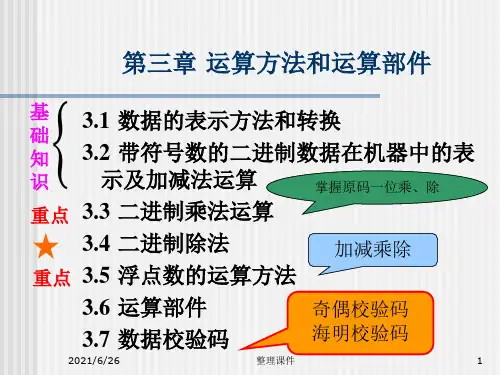

第三章 运算方法和运算部件(3-3,4,5)

- 格式:ppt

- 大小:1.53 MB

- 文档页数:54

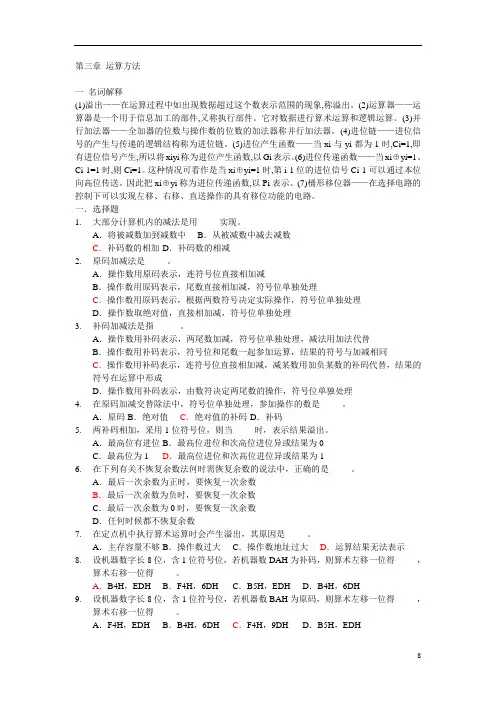

第三章运算方法一名词解释(1)溢出——在运算过程中如出现数据超过这个数表示范围的现象,称溢出。

(2)运算器——运算器是一个用于信息加工的部件,又称执行部件。

它对数据进行算术运算和逻辑运算。

(3)并行加法器——全加器的位数与操作数的位数的加法器称并行加法器。

(4)进位链——进位信号的产生与传递的逻辑结构称为进位链。

(5)进位产生函数——当xi与yi都为1时,Ci=1,即有进位信号产生,所以将xiyi称为进位产生函数,以Gi表示。

(6)进位传递函数——当xi⊕yi=1、Ci-1=1时,则Ci=1。

这种情况可看作是当xi⊕yi=1时,第i-1位的进位信号Ci-1可以通过本位向高位传送。

因此把xi⊕yi称为进位传递函数,以Pi表示。

(7)桶形移位器——在选择电路的控制下可以实现左移、右移、直送操作的具有移位功能的电路。

一.选择题1.大部分计算机内的减法是用_____实现。

A.将被减数加到减数中B.从被减数中减去减数C.补码数的相加 D.补码数的相减2.原码加减法是_____。

A.操作数用原码表示,连符号位直接相加减B.操作数用原码表示,尾数直接相加减,符号位单独处理C.操作数用原码表示,根据两数符号决定实际操作,符号位单独处理D.操作数取绝对值,直接相加减,符号位单独处理3.补码加减法是指______。

A.操作数用补码表示,两尾数加减,符号位单独处理,减法用加法代替B.操作数用补码表示,符号位和尾数一起参加运算,结果的符号与加减相同C.操作数用补码表示,连符号位直接相加减,减某数用加负某数的补码代替,结果的符号在运算中形成D.操作数用补码表示,由数符决定两尾数的操作,符号位单独处理4.在原码加减交替除法中,符号位单独处理,参加操作的数是_____。

A.原码 B.绝对值C.绝对值的补码 D.补码5.两补码相加,采用1位符号位,则当_____时,表示结果溢出。

A.最高位有进位 B.最高位进位和次高位进位异或结果为0C.最高位为1 D.最高位进位和次高位进位异或结果为16.在下列有关不恢复余数法何时需恢复余数的说法中,正确的是_____。

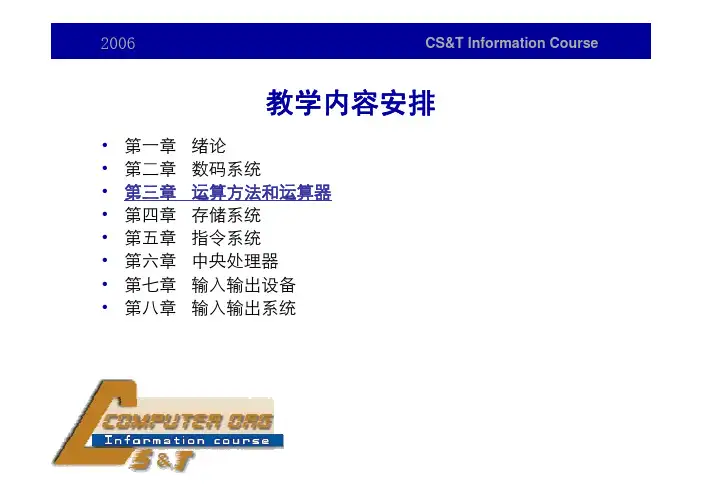

教学内容安排•第一章绪论•第二章数码系统•第三章运算方法和运算器•第四章存储系统•第五章指令系统•第六章中央处理器•第七章输入输出设备•第八章输入输出系统第三章运算方法和运算器• 3.1组成计算机硬件电路的基本逻辑部件• 3.2机器数的加减运算及其实现• 3.3定点乘法及其实现• 3.4定点除法及其实现(了解)• 3.5浮点数的算术运算(了解)• 3.6运算器的组教学重点和难点•基本逻辑运算和逻辑电路•机器数的加减运算•定点原码一位乘第三章运算方法和运算器 3.1组成计算机硬件电路的基本逻辑部件逻辑电路的基本概念•表示电路中输入信号与输出信号之间的关系的运算,为逻辑运算•赋以逻辑属性值“0”或“1”的变量,为逻辑变量。

•描述逻辑变量关系的函数(F=f(A,B)),为逻辑函数•实现逻辑函数功能的电路,为逻辑电路•逻辑电路可以做成计算机系统中常用的部件,为逻辑部件。

•逻辑部件分为:组合逻辑部件和时序逻辑电路•描述逻辑函数的值与它的逻辑变量之间关系的表格,称作真值表。

第三章运算方法和运算器 3.1组成计算机硬件电路的基本逻辑部件逻辑代数中基本逻辑运算•逻辑与(逻辑乘)•逻辑或(逻辑加)•逻辑非(逻辑求反)•逻辑异或•逻辑同或第三章运算方法和运算器 3.1组成计算机硬件电路的基本逻辑部件1.“与”逻辑------实现的电路叫与门只有决定事物结果的全部条件同时具备时,结果才会发生(有一个条件不具备,结果也不会发生)。

闭合1闭合1逻辑表达式第三章运算方法和运算器 3.1组成计算机硬件电路的基本逻辑部件2.“或”逻辑------实现的电路叫或门决定事物结果的诸条件中只要有任何一个满足时,结果就发生,这种因果关系叫做逻辑“或”,换句话说,只有所给条件均不具备,结果才不会发生。

第三章运算方法和运算器 3.1组成计算机硬件电路的基本逻辑部件3.“非”(反)逻辑-----实现的电路叫非门(或反相器)如果条件具备了,结果便不会发生;而条件不具备时结果一定发生。

第1章计算机系统概述一、选择题1、在下列四句话中,最能准确反映计算机主要功能的是 C。

A、计算机可以存储大量信息B、计算机能代替人的脑力劳动C、计算机是一种信息处理机D、计算机可实现高速运算2、1946年2月,在美国诞生了世界上第一台电子数字计算机,它的名字叫(1)C,1949年研制成功的世界上第一台存储程序式的计算机称为(2)。

(1)A、EDVAC B、EDSAC C、ENIAC D、UNIVAC-Ⅰ(2)A、EDVAC B、EDSAC C、ENIAC D、UNIVAC-Ⅰ3、计算机硬件能直接执行的只能是B。

A、符号语言B、机器语言C、汇编语言D、机器语言和汇编语言4、对计算机软、硬件资源进行管理,是 A 的功能。

A、操作系统B、数据库管理系统C、语言处理程序D、用户程序二、填空题1、计算机的各大部件通过____总线____________连接在一起,它是各部件之间传输信息的通道。

2、计算机按内部信息形式可以分为___模拟____________和___数字信号_两类。

3、计算机硬件一般由_运算器,控制器_______、__存储器______、_输入_______和、____输出____和五大部分组成。

4、运算器是一个数据加工部件,主要完成二进制___算术_______运算及__逻辑________运算。

5、运算器的___位数________越多,计算的精度就越高,但是所费的电子器件也越多,成本越高。

三、简答题1、简述计算机的发展过程。

1、第一代电子管计算机1946年2月,诞生了世界上第一台电子数字计算机——ENIAC ,1949年研制成功的世界上第一台存储程序式的计算机EDSAC 。

2、第二代晶体管计算机1947年在贝尔实验室制成第一个晶体管,进入20世纪50年代全球出现一场以晶体管代替电子管的革命。

3、第三代集成电路计算机4、大规模集成电路计算机5、超大规模集成电路计算机3、冯.诺依曼计算机的特点是什么?它包括哪些主要组成部分?各部分的功能是什么?1、计算机由运算器、存储器、控制器、输入设备和输出设备五大部件组成2、指令和数据以同等的地位存放在存储器内,并可以按地址寻访3、指令和数据均用二进制数表示4、指令由操作码和地址组成。

第三章运算方法与运算器文章目录定点补码加减法运算补码加减法运算方法溢出及检测溢出检测操作数与运算结果的符号位是否一致最高位的进位和符号位的进位是否一致变形补码补码加减法的逻辑实现移码加减运算及实现逻辑移码的加法运算移码加减法的溢出判断直接采用移码运算的溢出判断方法采用双符号判断定点乘法运算机器数的移位操作原码一位乘法原码一位乘法符号位的确定乘积的数值补码一位乘法运算规则(booth算法)阵列乘法器定点除法运算原码一位除法原码恢复余数法原码不恢复余数法不恢复余数的补码一位除法浮点运算浮点数加减运算阶码和尾数采用补码表示的浮点数加减运算IEEE 754浮点数的加减运算浮点数乘法运算浮点数除法运算逻辑运算运算器定点运算器运算前的基本组成单元算术逻辑运算单元通用寄存器组输入输出数据选择控制内部总线运算器的基本结构单总线双总线三总线浮点运算器基本算术逻辑单元的设计基本算术、逻辑部件基本算术逻辑运算单元设计串行进位加法器并行加法器定点补码加减法运算补码加减法运算方法补码加法:[x]补 + [y]补 = [x + y]补 mod M补码减法:[x]补 - [y]补 = [x - y]补 mod M溢出及检测运算结果超出数据类型所能表示数据范围的现象称为溢出溢出检测操作数与运算结果的符号位是否一致只有符号相同的数相加,才有可能产生溢出,因此检测运算结果的符号位,是否与操作数一致设操作数为S1XXXX和S2XXXX,其中S1和S2为他们的符号位,结果为SXXXX,S是结果的标志位,V是溢出标志位,那么V = S1 S2 !S + !S1 !S2 S如果符号位不同,则S1和S2必定是0和1的组合,其结果V一定为0 如果符号位相同,则可能同时为0或者同时为1,这时就要看结果的符号位S了最高位的进位和符号位的进位是否一致最高位C和符号位S的进位,如果不同步,则发生了溢出变形补码变形补码就是用两个位来表示符号位,正数符号位00,负数符号位11 如果运算后的结果为01,则上溢,10则下溢补码加减法的逻辑实现利用一位全加器(FA)作为基本的加法单元,低位FA的进位,直接送到相邻高位FA的进位输入,构成一个串行进位链进行加法运算时,直接送入全加器,进行减法运算时,减数先求补采用基于变形补码的双符号位溢出检测方法不支持逻辑运算移码加减运算及实现逻辑移码的加法运算公式1:[x]移 + [y]移 = [x + y]移 + 2^n公式2:[x]移 + [y]移 = [x + y]补公式3:[x]移 + [y]补 = [x + y]移 mod 2^(n+1)求移码的加法有三种方式直接对两数的移码求和,然后将高位取反直接求出两数和的补码,然后将高位取反用一个数的移码,加另一个数的补码移码加减法的溢出判断直接采用移码运算的溢出判断方法只有符号相同的加法,才会溢出正数的移码,符号位为1,如果两个正数的移码相加,符号位1+1=0,结果的符号位变成0因此,移码相加后,符号位与操作数相同,则发生了溢出采用双符号判断S1S2 = 00,结果为负,未溢出S1S2 = 01,结果为正,未溢出S1S2 = 10,上溢S1S2 = 11,下溢定点乘法运算机器数的移位操作移位操作是乘法实现过程的基本操作,又分为逻辑移位和算术移位逻辑移位:左移和右移,空出来的位置都补0算术移位:左移时低位补0,右移时高位补符号位原码一位乘法原码一位乘法符号位的确定两个乘数符号位的异或乘积的数值由于符号位已经单独处理了,所以乘积就是绝对值相乘用循环累加和移位操作实现乘法运算两个n位数参加乘法运算,要做n次加法和移位操作补码一位乘法运算规则(booth算法)被乘数一般取双符号位参与运算乘数末位增设附加位Y(n+1),初值为0利用Y(n+1) 与 Yn 的差,决定下一步的具体运算按照上述算法进行n+1步累加操作,n步右移操作Y(n+1) - Yn部分积右移一位部分积加[x]补后,右移一位部分积加[-x]补后,右移一位阵列乘法器一位乘法通过逐位判断、右移、循环累加来实现,速度较慢,为了提高乘法速度,可以采用硬件方式实现阵列乘法器,其基本思想是采用类似手工乘法运算的方法,用大量与门产生手工乘法中的各乘积项,同时将大量一位全加器按照手工乘法算式中需要进行加运算的各相关项的排列方式组成加法器阵列定点除法运算除法运算与乘法运算的处理思想相似,通常是将n位数的除操作转换成若干次的加减和移位来实现原码一位除法原码恢复余数法被除数(余数)减去除数,如果为正则够减商1,如果为负则不够减商0,而且被除数(余数)要恢复到减之前的值,这就叫恢复余数法为了防止溢出,除法运算(x - y)一定要满足(|x| |y|),保证商的绝对值不超过1,因此第一次上商的值,要放在商的符号位,后面上的商,从小数点后依次排列,商的位数一般与除数相等,因此最后一次上商后,就不用做减法和移位了原码不恢复余数法与恢复余数法相比,进行比较后,如果商1则算法不变,如果商0则不恢复余数,先移位再加上除数当余数为正时,商1,余数左移一位,减去除数当余数为负时,商0,余数左移一位,加上除数不恢复余数的补码一位除法算法规则如下被除数与除数同号,被除数减去除数;被除数与除数异号,被除数加上除数余数与除数同号,商1,余数左移一位减去除数;余数与除数异号,商0,余数左移一位加上除数一般情况下,对于商的精度没有特殊要求,商的末位“恒置1”如果要求提高精度,则多求一位商,再用校正的办法对商进行处理当刚好能除尽时,如果除数为正,则商不必修正;如果除数位负,则商需要校正当不能除尽时,如果商为正,则不必修正;如果商为负,则商需要校正求得n位商后,得到的余数往往是不正确的,正确的余数常需要根据具体情况做适当的处理若商为正,当余数与被除数符号相同,则不需处理;当余数与被除数异号时,则应将余数加上除数进行修正才能获得正确的余数若商为负,当余数与被除数同号时,则余数不需要处理;当余数与被除数异号时,则余数需要减去除数进行校正余数之所以需要校正,是因为补码不恢复余数法除法运算过程中先比较上商的缘故浮点运算浮点数常用规格化数进行运算浮点数加减运算阶码和尾数采用补码表示的浮点数加减运算对阶:对阶的原则是小的阶码向大的看齐,因为小阶码增大时,尾数部分右移而减小,损失的是最低位,对精度影响不大尾数运算:对阶完成后,按照定点数的加减法运算执行尾数加减操作结果规格化:为了处理方便,一般取两位符号位,当尾数符号位01或10时,需要向右规格化,将尾数右移一位,同时阶码加一;当尾数为11.1xxx 或00.0xxx时,需要左移规格化,左移次数不固定,直到尾数部分出现11.0xx或00.1xx为止舍入:在对阶右移和结果规格化右移时,会丢掉末尾的值,常用的舍入方法末位恒置1法:只要右移时丢失过1,则末位置10舍1入法:当丢失位数最高位为1时,尾数末尾加1溢出判断:只有阶码溢出时,才产生溢出,阶码符号位为01和10时溢出IEEE 754浮点数的加减运算IEEE 754浮点数的阶码采用移码表示,尾数采用原码表示,且尾数的最高位隐藏,因此算法与之前都采用补码的形式不同对阶和规格化过程中,阶码的运算采用移码的加减运算尾数的运算采用原码运算法则,且隐藏位要参与尾数运算隐藏位参与尾数规格化判断及尾数规格化过程溢出判断,上溢时阶码全1,下溢时阶码全0浮点数乘法运算阶码相加尾数相乘结果规格化浮点数除法运算尾数调整:检查被除数的尾数是否小于除数的尾数(考察绝对值),如果被除数的尾数大于除数尾数,则将被除数的尾数右移一位并调整阶码。

第3章运算方法和运算部件在计算机中,完成数值运算的部件就是CPU中的算术逻辑运算单元ALU(Arithmetic Logical Unit)。

ALU的逻辑结构取决于机器的指令系统、数据的表示方法、运算方法和选用的逻辑器件等。

数据的表示方法在第二章中已经讲解,指令系统的内容将在第五章介绍,本章重点介绍运算方法、运算器的结构和工作原理。

对运算方法的讨论主要是指:算术运算在计算机中是按什么规则进行的。

对不同的机器数表示形式所对应的算法也不同。

此外,由于计算机中的数有定点和浮点表示,因此相应的有定点数运算和浮点数的运算方法。

计算机中的加、减、乘、除基本算术运算通常都是转化为加法运算完成的,因此加法器是构成运算器的关键部件。

为了提高乘除法运算速度,有的计算机还专门设置了乘法部件和除法部件,但加法器绝对不是可有可无的。

在运算器内部,除了加法器以外,还设有一定数量的寄存器,用来存放参加运算的数据及运算过程中的中间结果。

不同计算机的寄存器数目和功能都有所不同。

满足加、减法运算要求的寄存器数目一般最少要有两个,而要完成乘、除法运算,则一般至少要有三个寄存器。

可被程序员指定访问的寄存器通常叫做通用寄存器(General Register);此外还有一些工作寄存器,例如状态标志寄存器(Flag Register),主要用以保存一条指令执行后运算结果的特征。

逻辑运算也是计算机中常用的操作,其硬件设置比较简单,通常是在加法器的输入端增加相应的逻辑门来实现。

随着大规模集成电路的发展,运算器的结构也在不断地变化。

本章将以4位片的ALU SN 74181 为例子,介绍ALU的结构和原理。

3-1算术逻辑运算基础3-1-1 定点数的加减法运算加法运算是所有计算机的基本运算,减法运算可以通过补码加法来实现。

而乘法和除法运算也可以通过一系列的加减法运算和移位来实现。

我们通过第二章的学习已知:在计算机内部,带符号数通常都是用补码来表示的,这当然是由补码的特点决定的。