半导体器件物理-MOSFET4

- 格式:ppt

- 大小:2.68 MB

- 文档页数:21

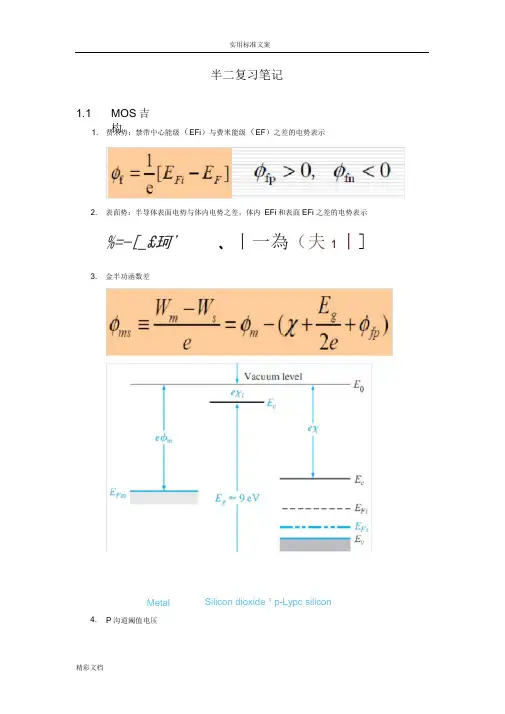

%=—[_£珂'、丨一為(夫1丨]半二复习笔记1.11.MOS 吉构 费米势:禁带中心能级(EFi )与费米能级(EF )之差的电势表示表面势:半导体表面电势与体内电势之差,体内 EFi 和表面EFi 之差的电势表示2. 3. 金半功函数差4. MetalP 沟道阈值电压Silicon dioxide 1 p-Lypc silicon意faifn 是个负值1.3 MOS 原理1. MOSFET 非饱和区IV 公式g =岑5% —耳)瞎-氐](当 V GS > go <V DS < "2(如 J2. 跨导定义:VDS —定时,漏电流ID 随VGS 变化率,反映了 VGS 对ID 的控制能力戶F 饱和区(含线性区卫“缶"冋切)SmL -------- : ------ * as饱和区(厂氏注厂肌(的))3.提咼饱和区跨导途径T ¥D =^7^[2(%-冷)%-氐]2L。

二仝牛竺T GS -厲广 2昨畑“”叫无关GS —「T密勒电容G =c 叭(1+爲几)阈值反型点时的变化,最大耗尽层和最大耗尽层电荷面密度变化:2017/10/235.背栅定义:衬底能起到栅极的作用。

VSB 变化,使耗尽层宽度变化,耗尽层电荷变化;若VGS 不变,则反型沟道电荷变化,漏电流变化1.4频率特性1. MOSFET 频率限制因素: ①沟道载流子的沟道运输时间(通常不是主要的限制因素)② 栅电容充放电需要时间2.截止频率:器件电流增益为1时的频率'炳> a2卩血十"防 JV2 I「迟(现+4)广 1现」4.衬底偏置电压VSB>0其影响高频等效模型如下:1.5 CMOS1. 开关特性开关时间:输出相对于输入的时间延迟,包括导通时间如和关断时间(针对驱动管、NOS 而言) 载流子沟道输运时间b (本征延迟〉 取决于沟道的长度和载流子的漂移速度 输出端对地电容的充放电时间(负载延迟)取决于输出端对地总电容G T 大小和充放电电流(』广人)的大小输入电励可恥爲+01/ 、=>电流增益 打输出电流仃=為仪]A2#(C^+C V )截1E 频率可」Irr 1跨盹E 等效输入栅极电容cG = c gs T +C M:跨导加栅极总电容CG 看题目所给条件。

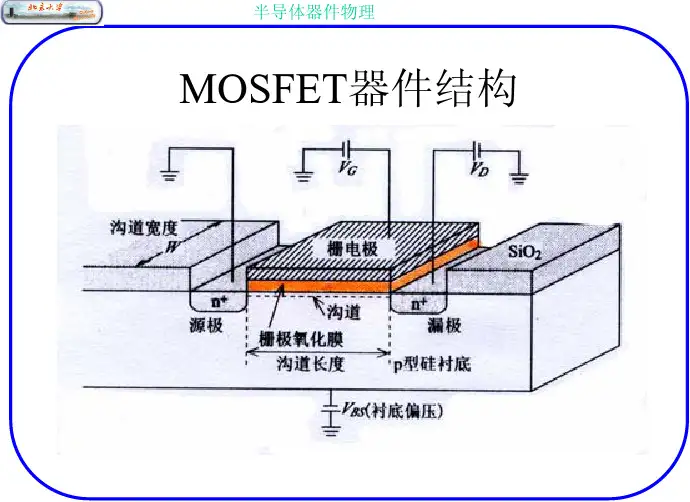

半导体器件物理进展第四章CMOS的等比例缩小、优化设计及性能因子CMOS Scaling, Design Optimization, and Performance FactorsPart 1 MOSFET模型及小尺寸效应内容提要:MOSFET结构及其偏置条件MOSFET的漏极电流模型MOSFET的亚阈区特性与温度特性 MOSFET的小尺寸效应MOSFET的缩比特征长度MOSFET的速度饱和效应1. MOSFET结构及其偏置条件MOSFET在实际集成电路中的剖面结构如下图所示。

横向:源-沟道-漏;纵向:M-O-S;几何参数L:沟道长度;W:沟道宽度;t ox:栅氧化层厚度;x j:源漏结深;MOSFET的发展简史:早期:主要采用铝栅电极,栅介质采用热氧化二氧化硅,扩散形成源、漏区,其与栅电极之间采用非自对准结构,场区采用厚氧化层隔离;中期:栅极采用N型掺杂的多晶硅栅,源、漏区与栅极之间采用自对准离子注入结构,场区采用硅的局部氧化工艺(LOCOS)实现器件隔离;后期:栅极采用互补双掺杂(N型和P型)的多晶硅栅,源漏区与栅极之间采用LDD(轻掺杂漏)结构和金属硅化物结构,场区采用浅沟槽隔离(STI)技术。

近期:栅极采用难熔金属栅极(例如W、Mo等),栅介质采用高K介质材料(例如氧化铪等),源、漏区与栅极之间采用自对准金属硅化物结构,场区采用浅沟槽隔离或其它介质隔离技术。

一个自对准MOSFET的工艺制造过程以NMOS器件为例,包含四个结构化的光刻掩模:(1)场区光刻掩模:利用氮化硅掩蔽的LOCOS局部氧化工艺,在P型掺杂的硅单晶衬底上定义出器件有源区和场氧化层隔离区;(2)栅极光刻掩模:通过多晶硅的淀积、光刻和刻蚀工艺,定义出器件的多晶硅栅电极;(3)接触孔光刻掩模:通过对源漏有源区及多晶硅栅电极上二氧化硅绝缘层的光刻和刻蚀工艺,定义出相应的欧姆接触窗口;(4)铝引线光刻掩模:通过铝布线金属的溅射、光刻和刻蚀工艺,定义出器件各引出端的铝引线电极;对于包含PMOS器件的CMOS工艺,则还需要增加一步N阱区的掩模及其光刻定义。

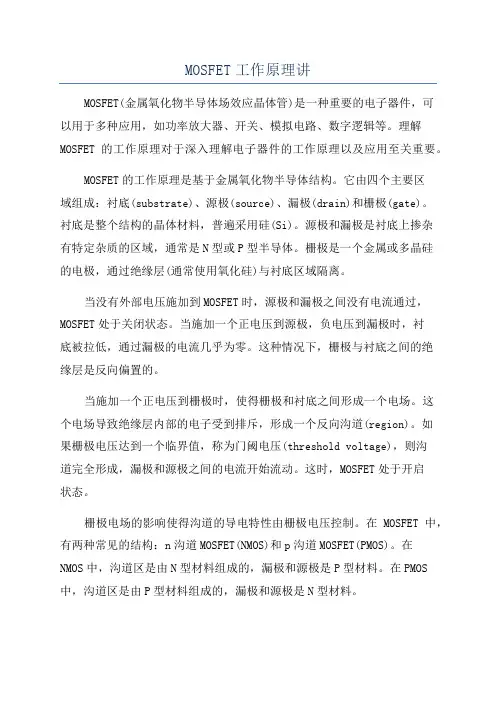

MOSFET工作原理讲MOSFET(金属氧化物半导体场效应晶体管)是一种重要的电子器件,可以用于多种应用,如功率放大器、开关、模拟电路、数字逻辑等。

理解MOSFET的工作原理对于深入理解电子器件的工作原理以及应用至关重要。

MOSFET的工作原理是基于金属氧化物半导体结构。

它由四个主要区域组成:衬底(substrate)、源极(source)、漏极(drain)和栅极(gate)。

衬底是整个结构的晶体材料,普遍采用硅(Si)。

源极和漏极是衬底上掺杂有特定杂质的区域,通常是N型或P型半导体。

栅极是一个金属或多晶硅的电极,通过绝缘层(通常使用氧化硅)与衬底区域隔离。

当没有外部电压施加到MOSFET时,源极和漏极之间没有电流通过,MOSFET处于关闭状态。

当施加一个正电压到源极,负电压到漏极时,衬底被拉低,通过漏极的电流几乎为零。

这种情况下,栅极与衬底之间的绝缘层是反向偏置的。

当施加一个正电压到栅极时,使得栅极和衬底之间形成一个电场。

这个电场导致绝缘层内部的电子受到排斥,形成一个反向沟道(region)。

如果栅极电压达到一个临界值,称为门阈电压(threshold voltage),则沟道完全形成,漏极和源极之间的电流开始流动。

这时,MOSFET处于开启状态。

栅极电场的影响使得沟道的导电特性由栅极电压控制。

在MOSFET中,有两种常见的结构:n沟道MOSFET(NMOS)和p沟道MOSFET(PMOS)。

在NMOS中,沟道区是由N型材料组成的,漏极和源极是P型材料。

在PMOS 中,沟道区是由P型材料组成的,漏极和源极是N型材料。

当NMOS或PMOS处于开启状态时,漏极和源极之间的电流正比于栅极电压与门阈电压之间的差值。

如果栅极电压高于门阈电压,则沟道导电性增强,电流增大。

如果栅极电压低于门阈电压,则沟道导电性减弱,电流减小。

MOSFET的特点之一是具有高输入阻抗。

输入阻抗是指输入端读取电流和电压之间的比例关系。

mos管q4的体二极管

MOS管(MOSFET)的Q4是指N沟道MOS管的第四象限工作区。

在Q4工作区,MOS管的栅极电压(Vgs)为负值,且漏极电压(Vds)也为负值。

在这个工作区,MOS管的栅极电压低于阈值电压,使栅极与源极之间的沟道关闭。

同时,漏极电压为负,使漏极区域形成了PN结,从而将MOS管的底部二极管(也称为体二极管)逆偏。

因此,Q4工作区下的MOS管是一种开启的三极管结构。

体二极管具有反向偏置的特性,不会产生导电效果。

在Q4工作区下,MOS管被用作开关,用于控制电流的导通和截断。

当控制信号(Vgs)为负值时,MOS管处于关断状态,没有漏极电流流过。

当控制信号(Vgs)变为正值时,MOS管进入其他象限的工作区,可能发生导通,漏极电流流动。

需要注意的是,Q4工作区仅适用于N沟道MOS管的情况。

对于P沟道MOS管而言,在不同象限的工作区可能会有不同的编号。

在实际应用中,根据具体的电路要求和设备特性,可以选择合适的MOS管工作区来实现所需的电流控制和开关功能。