第5章锁存器和触发器

- 格式:doc

- 大小:60.04 KB

- 文档页数:4

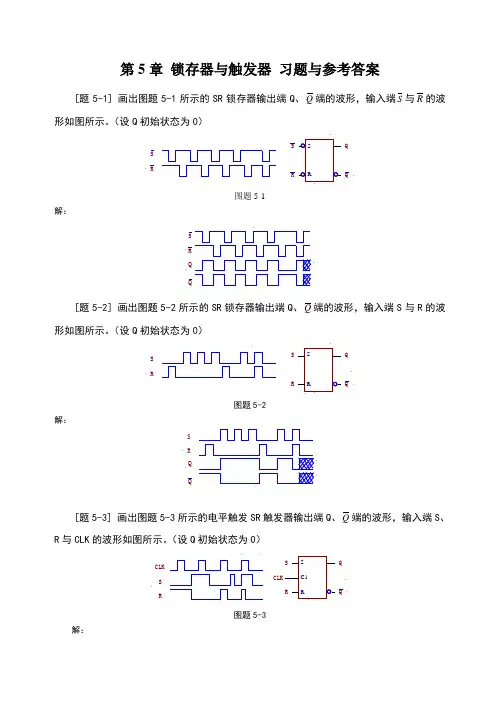

第5章 锁存器与触发器 习题与参考答案[题5-1] 画出图题5-1所示的SR 锁存器输出端Q 、Q 端的波形,输入端S 与R 的波形如图所示。

(设Q 初始状态为0)S RSRSRQQ....图题5-1解:SR.QQ....[题5-2] 画出图题5-2所示的SR 锁存器输出端Q 、Q 端的波形,输入端S 与R 的波形如图所示。

(设Q 初始状态为0)S RS RQQ...SR....图题5-2解:SR.Q Q......[题5-3] 画出图题5-3所示的电平触发SR 触发器输出端Q 、Q 端的波形,输入端S 、R 与CLK 的波形如图所示。

(设Q 初始状态为0)C1S RSRQQ....CLKS RCLK...图题5-3解:S RCLK..Q Q..[题5-4] 画出图题5-4所示的电平触发D 触发器输出Q 端的波形,输入端D 与CLK 的波形如图所示。

(设Q 初始状态为0)C1D DQQ....CLKDCLK..图题5-4解:DCLK..QQ....[题5-5] 画出图题5-5所示的边沿触发D 触发器输出端Q 端的波形,输入端D 与CLK 的波形如图所示。

(设Q 初始状态为0)C11DD QQ....CLKDCLK ...DQQ....CLKDCLK...C11D (1)(2)图题5-5解:DCLK ...DCLK...(1)(2)QQ....[题5-6] 画出图题5-6所示的边沿D 触发器输出Q 端的波形,CLK 的波形如图所示。

(设Q 初始状态为0)C11D Q 1CLK....CLK.1C11D Q 2CLK .CLK .图题5-6解:CLK....Q1Q2Q3...[题5-7] 试画出图题5-7所示电路输出端Q 1、Q 0端的波形,CLK 的波形如图所示。

(设Q 初始状态为0)CLK.....图题5-7解:..CLK...Q0Q1[题5-8] 画出图题5-8所示的JK 触发器输出Q 端的波形,输入端J 、K 与CLK 的波形如图所示。

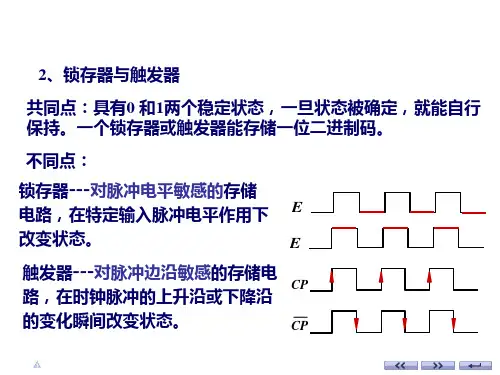

锁存器和触发器锁存器(Latch)和触发器(Flip-flop)是数字电路中常用的存储元件。

它们能够存储一个或多个位的信息,并将其在需要的时候保持下去。

在数字电路中,锁存器和触发器常用于存储、传输和操作数据。

本文将介绍锁存器和触发器的基本原理、特性和应用。

1. 锁存器锁存器是一种能够存储和保持输入信号状态的元件。

它可以通过一个控制信号来控制存储和保持动作。

常见的锁存器有SR锁存器、D锁存器和JK锁存器。

1.1 SR锁存器SR锁存器是由两个交叉连接的与非门构成的。

它有两个输入信号:S(Set)和R(Reset)。

当S=1、R=0时,输入Q=1,输出Q’=0;当S=0、R=1时,输入Q=0,输出Q’=1;当S=0、R=0时,保持前一状态不变;当S=1、R=1时,无效。

SR锁存器的真值表如下:S R Q Q’0 0 Q Q’0 1 0 11 0 1 01 1 禁止禁止1.2 D锁存器D锁存器是由一个与非门和一个与门构成的。

它只有一个输入信号D(Data)。

当D=0时,输入Q=0,输出Q’=1;当D=1时,输入Q=1,输出Q’=0。

D锁存器的真值表如下:D Q Q’0 0 11 1 01.3 JK锁存器JK锁存器是由两个与非门和一个与门构成的。

它有两个输入信号J(Jump)和K(Kill)。

当J=1、K=0时,输入Q=1,输出Q’=0;当J=0、K=1时,输入Q=0,输出Q’=1;当J=0、K=0时,保持前一状态不变;当J=1、K=1时,输入Q’=Q’的反相。

JK锁存器的真值表如下:J K Q Q’0 0 Q Q’0 1 0 11 0 1 01 1 翻转翻转2. 触发器触发器是一种特殊的锁存器,它能够根据时钟信号进行同步操作。

触发器有很多种类,其中最常见的是D触发器、JK触发器和T触发器。

2.1 D触发器D触发器是一个带有使能端的触发器,它只有一个输入信号D(Data),一个时钟信号CLK(Clock)和一个使能信号EN(Enable)。

锁存器和触发器

1.分析图1所示电路的功能,列出功能表。

图1

2.若图2 a所示电路的初始状态为Q = 1,E、S、R端的输入信号如图2 b 所示,试画出相应Q和Q端的波形。

S

G3 Q

Q

E

R

S

(a) (b)

图2

3.试用1片八D锁存器74HC373设计一个能锁存两位BCD码信号的锁存电路。

假定三态输出使能端OE=0,锁存器原输出Q7Q6Q5Q4Q3Q2Q1Q0=10010100(94D),而输入为D7D6D5D4D3D2D1D0=10010101(95D),画出锁存器锁存新数据前、后使能端LE应输入的波形和相应Q

的波形。

4.触发器的逻辑电路如图4所示,确定其应属于何种电路结构的触发器。

9 Q Q

图4

5.上升沿触发和下降沿触发的D触发器逻辑符号及时钟信号CP

(CP)和D 的波形如图5所示。

分别画出它们的Q端波形。

设触发器的初始状态为0。

D D

D

CP(CP)

图5

6.设下降沿触发的JK触发器初始状态为0,CP、J、K信号如图6所示,试画出触发器Q端的输出波形。

J

K

图6

7.逻辑电路如图7所示,试画出在CP作用下,φ0、φ1、φ2和φ3的波形。

图7

8.电路如图

8所示,设各触发器的初态为

0,画出在CP脉冲作用下Q端波

形。

Q1

Q1

3

Q3

4

Q4

CP

(a) (b) (c) (d)

图8

9.逻辑电路如图9所示,已知CP和X

的波形,试画出Q1和Q2的波形。

触发

器的初始状态均为0。

X

1

X

图9

10.两相脉冲产生电路如图10所示,试画出在CP作用下φ1、φ2的波形,并

说明φ1和φ2的时间关系。

各触发器的初始状态为0。

φ2

图10。