脉冲边沿检测(Verilog)

在很多时候都要对输入脉冲进行边沿检测,如PS/2时序,ps2_data数据在ps2_clk时钟下降沿接收。

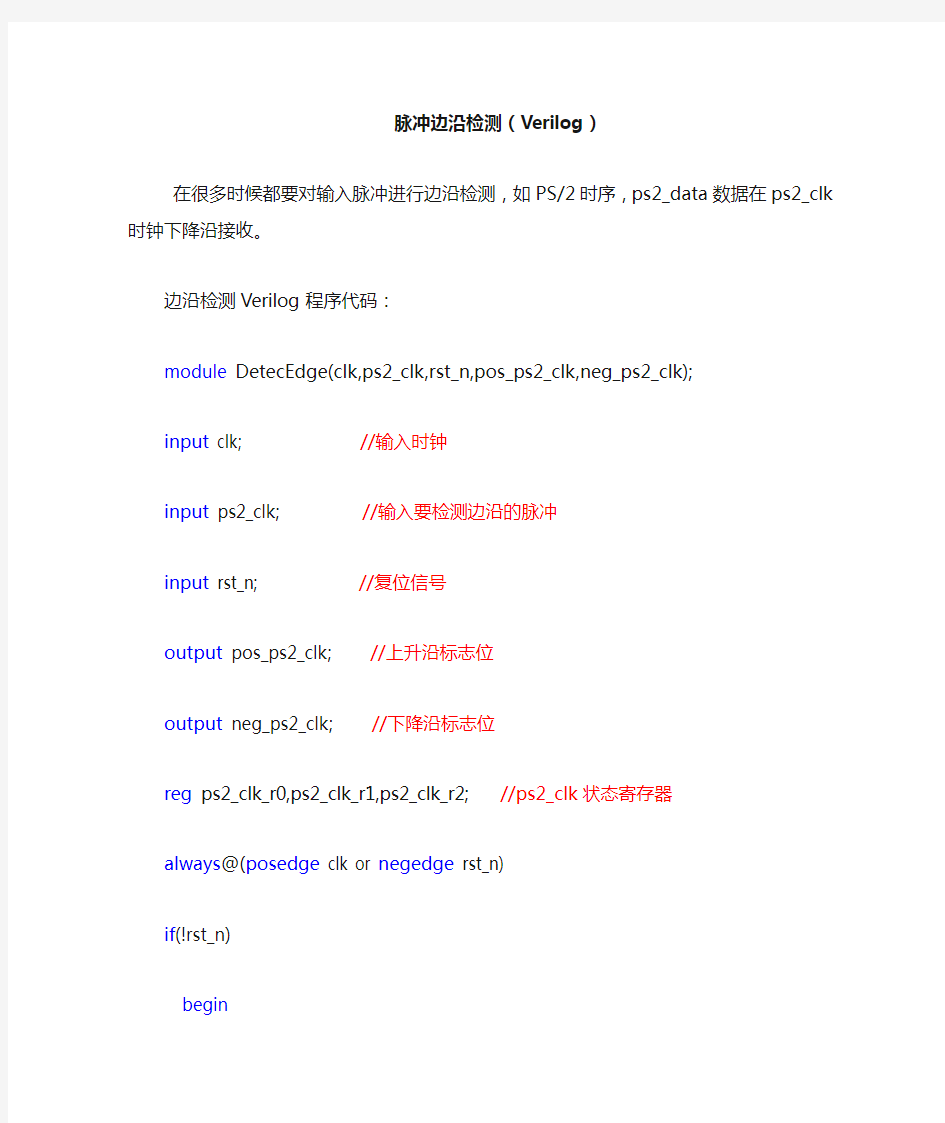

边沿检测Verilog程序代码:

module DetecEdge(clk,ps2_clk,rst_n,pos_ps2_clk,neg_ps2_clk);

input clk; //输入时钟

input ps2_clk; //输入要检测边沿的脉冲

input rst_n; //复位信号

output pos_ps2_clk; //上升沿标志位

output neg_ps2_clk; //下降沿标志位

reg ps2_clk_r0,ps2_clk_r1,ps2_clk_r2; //ps2_clk状态寄存器

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

ps2_clk_r0<=1'b0;

ps2_clk_r1<=1'b0;

ps2_clk_r2<=1'b0;

end

else//锁存状态

begin

ps2_clk_r0<=ps2_clk;

ps2_clk_r1<=ps2_clk_r0;

ps2_clk_r2<=ps2_clk_r1;

end

assign pos_ps2_clk=(~ps2_clk_r2)&ps2_clk_r1; //上升沿检测

assign neg_ps2_clk=ps2_clk_r2&(~ps2_clk_r1); //下降沿检测

endmodule

布线布局后仿真波形如下图:

可以注意到其中的移位寄存器用了非阻塞赋值(<=)

ps2_clk_r0<=ps2_clk;

ps2_clk_r1<=ps2_clk_r0;

ps2_clk_r2<=ps2_clk_r1;

如果用阻塞赋值的话,综合的时候会把其中两个寄存器去点,用阻塞赋值(=)

ps2_clk_r0=ps2_clk;

ps2_clk_r1=ps2_clk_r0;

ps2_clk_r2=ps2_clk_r1;

会出来这样的警告:

WARNING:Xst:646 - Signal

Register

Found 1-bit register for signal

WARNING:Xst:2677 - Node

从RTL可以看到,只剩ps2_clk_r1一个D触发器。

上图是非阻塞赋值综合后的RTL,可以看出,有三个D触发器做移位寄存器。通过移位,对边沿进行检测。

代码还有一种写法:

module DetecEdge(clk,ps2_clk,pos_ps2_clk,neg_ps2_clk);

input clk; //输入时钟

input ps2_clk; //输入要检测边沿的脉冲

output pos_ps2_clk; //上升沿标志位

output neg_ps2_clk; //下降沿标志位

reg [2:0] ps2_clkr; //用一个fifo来采样ps2_clk信号;

always @(posedge clk)

ps2_clkr <= {ps2_clkr[1:0], ps2_clk};

wire pos_ps2_clk = (ps2_clkr[2:1]==2'b01); // now we can detect ps2_clk rising edges

wire neg_ps2_clk = (ps2_clkr[2:1]==2'b10); // and falling edges

endmodule

布线布局后仿真波形和之前程序的仿真波形一样

基于FPGA的Verilog HDL数字钟设计 专业班级姓名学号 一、实验目的 1.掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程; 2.熟悉一种EDA软件使用; 3.掌握Verilog设计方法; 4.掌握分模块分层次的设计方法; 5.用Verilog完成一个多功能数字钟设计; 6.学会FPGA的仿真。 二、实验要求 ?功能要求: 利用实验板设计实现一个能显示时分秒的多功能电子钟,基本功能: 1)准确计时,以数字形式显示时、分、秒,可通过按键选择当前显示时间范围模式; 2)计时时间范围00:00:00-23:59:59 3)可实现校正时间功能; 4)可通过实现时钟复位功能:00:00:00 扩展功能: 5)定时报:时间自定(不要求改变),闹1分钟(1kHz)---利用板上LED或外接电路实现。 6)仿广播电台正点报时:XX:59:[51,53,55,57(500Hz);59(1kHz)] ---用板上LED或外接 7)报整点时数:XX:00:[00.5-XX.5](1kHz),自动、手动---用板上LED或外接 8)手动输入校时; 9)手动输入定时闹钟; 10)万年历; 11)其他扩展功能; ?设计步骤与要求: 1)计算并说明采用Basys2实验板时钟50MHz实现系统功能的基本原理。 2)在Xilinx ISE13.1 软件中,利用层次化方法,设计实现模一百计数及显示的电路系 统,设计模块间的连接调用关系,编写并输入所设计的源程序文件。 3)对源程序进行编译及仿真分析(注意合理设置,以便能够在验证逻辑的基础上尽快 得出仿真结果)。 4)输入管脚约束文件,对设计项目进行编译与逻辑综合,生成下载所需.bit文件。 5)在Basys2实验板上下载所生成的.bit文件,观察验证所设计的电路功能。

基于FPGA的计数器的程序设计方案 1.1 FPGA简介 FPGA(Field-Progrmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了 原有可编程器件门电路数有限的缺点。 自1985 年Xilinx 公司推出第一片中大规模现场可编程逻辑器件(FP2GA) 至 今,FPGA 已经历了十几年的历。在这十几年的过程中,可编程器件有了惊人的发展: 从最初的1200 个可利用门,到今天的25 万可利用门,规模增大了200 多倍; FPGA 供应商也从Xilinx 的一枝独秀,到今天近20 个厂商的分庭抗争;FPGA 从单一的基于SRAM结构到今天各种结构类型的出现,都充分体现了可编程器件这一巨大市场的吸引力。FPGA 不仅可以解决电子系统小型化、低功耗、高可靠性等问题,而且其开 发周期短、开发软件投入少、芯片价格 不断降低。由于目前电子产品生命周期相对缩短,相近功能产品的派生设计增多 等特点,促使FPGA 越来越多地取代了ASIC 的市场,特别是对国内众多的科研单位来说,小批量、多品种的产品需求,使得FPGA 成为首选。 1.2 硬件描述语言VHDL特点 功能强大、设计灵活。VHDL具有功能强大的语言结构,可以用简洁明确的源代码来描述复杂的逻辑控制。它具有多层次的设计描述功能,层层细化,最后可直接生成电路级描述。VHDL支持同步电路、异步电路和随机电路的设计,这是其他硬件描述语言所不能比拟的。VHDL还支持各种设计方法,既支持自底向上的设计,又支持自顶向下的设计;既支持模块化设计,又支持层次化设计。支持广泛、易于修改。由于VHDL已经成为IEEE标准所规范的硬件描述语言,目前大多数EDA工具几乎都支持VHDL,这为VHDL的进一步推广和广泛应用奠定了基础。在硬件电路设计过程中,主要的设计文件是用VHDL编写的源代码,因为VHDL易读和结构化,所以易于修改设计。强大的系统硬件描述能力。VHDL具有多层次的设计描述功能,既可以描

实验九脉冲计数(定时/计数器实验) 1、实验目的:熟悉单片机内部定时/计数器功能,掌握初始化编程方法。 2、实验内容:把定时器0外部输入的脉冲进行计数,并送显示器显示 3、实验程序框图: 4、实验接线图:

5、实验步骤:P3.4 依次接T0~T7或单脉冲输出孔,执行程序,观察数码管上 计数脉冲的速度及个数。 6、思考:修改程序使显示器上可显示到999999个脉冲个数。 7、程序清单文件名:SW09.ASM;脉冲计数实验 ORG 0000H LJMP SE15 ORG 06E0H SE15: MOV SP,#53H MOV P2,#0FFH MOV A,#81H MOV DPTR,#0FF23H MOVX @DPTR,A ; 1 MOV TMOD,#05H MOV TH0,#00H MOV TL0,#00H SETB TR0 LO29: MOV R2,TH0 MOV R3,TL0 LCALL ZOY0 MOV R0,#79H MOV A,R6 LCALL PTDS MOV A,R5 LCALL PTDS MOV A,R4 LCALL PTDS LCALL SSEE SJMP LO29 ZOY0: CLR A MOV R4,A MOV R5,A MOV R6,A MOV R7,#10H LO30: CLR C MOV A,R3 RLC A MOV R3,A MOV A,R2 RLC A MOV R2,A MOV A,R6 ADDC A,R6 DA A MOV R6,A MOV A,R5 ADDC A,R5 DA A MOV R5,A MOV A,R4 ADDC A,R4 DA A MOV R4,A DJNZ R7,LO30 RET PTDS: MOV R1,A

几种常用边缘检测算法的比较摘要:边缘是图像最基本的特征,边缘检测是图像分析与识别的重要环节。基于微分算子的边缘检测是目前较为常用的边缘检测方法。通过对Roberts,Sobel,Prewitt,Canny 和Log 及一种改进Sobel等几个微分算子的算法分析以及MATLAB 仿真实验对比,结果表明,Roberts,Sobel 和Prewitt 算子的算法简单,但检测精度不高,Canny 和Log 算子的算法复杂,但检测精度较高,基于Sobel的改进方法具有较好的可调性,可针对不同的图像得到较好的效果,但是边缘较粗糙。在应用中应根据实际情况选择不同的算子。 0 引言 边缘检测是图像分析与识别的第一步,边缘检测在计算机视觉、图像分析等应用中起着重要作用,图像的其他特征都是由边缘和区域这些基本特征推导出来的,边缘检测的效果会直接影响图像的分割和识别性能。边缘检测法的种类很多,如微分算子法、样板匹配法、小波检测法、神经网络法等等,每一类检测法又有不同的具体方法。目前,微分算子法中有Roberts,Sobel,Prewitt,Canny,Laplacian,Log 以及二阶方向导数等算子检测法,本文仅将讨论微分算子法中的几个常用算子法及一个改进Sobel算法。 1 边缘检测

在图像中,边缘是图像局部强度变化最明显的地方,它主要存在于目标与目标、目标与背景、区域与区域( 包括不同色彩) 之间。边缘表明一个特征区域的终结和另一特征区域的开始。边缘所分开区域的内部特征或属性是一致的,而不同的区域内部特征或属性是不同的。边缘检测正是利用物体和背景在某种图像特征上的差异来实现检测,这些差异包括灰度、颜色或纹理特征,边缘检测实际上就是检测图像特征发生变化的位置。边缘的类型很多,常见的有以下三种: 第一种是阶梯形边缘,其灰度从低跳跃到高; 第二种是屋顶形边缘,其灰度从低逐渐到高然后慢慢减小; 第三种是线性边缘,其灰度呈脉冲跳跃变化。如图1 所示。 (a) 阶梯形边缘(b) 屋顶形边缘 (b) 线性边缘 图像中的边缘是由许多边缘元组成,边缘元可以看作是一个短的直线段,每一个边缘元都由一个位置和一个角度确定。边缘元对应着图像上灰度曲面N 阶导数的不连续性。如果灰度曲面在一个点的N 阶导数是一个Delta 函数,那么就

4 脉冲信号产生电路 4.1 实验目的 1.了解集成单稳态触发器的基本功能及主要应用。 2.掌握555定时器的基本工作原理及其性能。 3.掌握用555定时器构成多谐振荡器、单稳态触发器的工作原理、设计及调试方法。 4.2 实验原理 1.集成单稳态触发器及其应用 在数字电路的时序组合工作中,有时需要定时、延时电路产生定时、展宽延时等脉冲,专门用于完成这种功能的IC,就是“单稳延时多谐振荡器”,也称“单稳触发器”。其基本原理是利用电阻、电容的充放电延时特性以及电平比较器对充放电电压检测的功能,实现定时或延时,只需按需要灵活改变电阻、电容值大小,就可以取得在一定时间范围的延时或振荡脉冲输出。常用的器件有LS121/122、LS/HC123、LS/HC221、LS/HC423、HC/C4538及CC4528B等。 集成单稳态触发器在没有触发信号输入时,电路输出Q=0,电路处于稳态;当输入端输入触发信号时,电路由稳态转入暂稳态,使输出Q=1;待电路暂稳态结束,电路又自动返回到稳态Q=0。在这一过程中,电路输 出一个具有一定宽度的脉冲,其宽度与电路的外接定时元件C ext 和R ext 的数 值有关。 图4-1

集成单稳态触发器有非重触发和可重触发两种,74LS123是一种双可重触发的单稳态触发器。它的逻辑符号及功能表如图4-1、表4-1所示。 在表4-1中“正”为正脉冲,“负”为负脉冲。 LS/HC123的特点是,复位端CLR也具有上跳触发单稳态过程发生的功能。 在C ext >1000pF时,输出脉冲宽度t w ≈0.45R ext C ext 。 器件的可重触发功能是指在电路一旦被触发(即Q=1)后,只要Q还未恢复到0,电路可以被输入脉冲重复触发,Q=1将继续延长,直至重复触发的最后一个触发脉冲的到来后,再经过一个t w (该电路定时的脉冲宽度)时间,Q才变为0,如图4-2所示: 图4-2 74LS123的使用方法: (1)有A和B两个输入端,A为下降沿触发,B为上升沿触发,只有AB=1时电路才被触发。 (2)连接Q和A或Q与B,可使器件变为非重触发单稳态触发器。 (3)CLR=0时,使输出Q立即变为0,可用来控制脉冲宽度。 (4)按图4-3、3-5-4连接电路,可组成一个矩形波信号发生器,利用开关S瞬时接地,使电路起振。 图4-3 图4-4 2.555时基电路及其应用 555时基电路是一种将模拟功能和数字逻辑功能巧妙地结合在同一硅片上的新型集成电路,又称集成定时器,它的内部电路框图如图4-5所示。 图4-5 电路主要由两个高精度比较器C 1、C 2 以及一个RS触发器组成。比较器 的参考电压分别是2/3V CC 和1/3V CC ,利用触发器输入端TR输入一个小于 1/3V CC 信号,或者阈值输入端TH输入一个大于2/3V CC 的信号,可以使触发 器状态发生变换。CT是控制输入端,可以外接输入电压,以改变比较器的参考电压值。在不接外加电压时,通常接0.01μF电容到地,DISC是放电输入端,当输出端的F=0时,DISC对地短路,当F=1时,DISC对地开路。 R D 是复位输入端,当R D =0时,输出端有F=0。 器件的电源电压V CC 可以是+5V~+15V,输出的最大电流可达200mA,当 电源电压为+5V时,电路输出与TTL电路兼容。555电路能够输出从微秒级到小时级时间范围很广的信号。 (1)组成单稳态触发器 555电路按图4-6连接,即构成一个单稳态触发器,其中R、C是外接定时元件。单稳态触发器的输出脉冲宽度t w ≈1.1RC。 图4-6 (2)组成自激多谐振荡器 图4-7 自激多谐振荡器电路 按图4-7连接,即连成一个自激多谐振荡器电路,此电路的工作过程

目录 摘要:单片机是一种集成在电路芯片,是采用超大规模集成电路技术把具有数据处理能力的中央处理器CPU、随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能集成到一块硅片上构成的一个小而完善的计算机系统。本课程设计的指导思想是控制单片机实现从0到99的计数功能,其结果显示在两位一体的共阳极数码管上。 关键词:脉冲计数器数码管单片机 本设计基于单片机技术原理,以单片机芯片STC89C52作为核心控制器,通过硬件电路的制作以及软件程序的编制,设计制作出一个计数器,包括以下功能:输出脉冲,按下键就开始计数,并将数值显示在两位一体的共阳极数码管上。 1课题原理 PCB板上设置开始计数按键和清零按键,以上按键与89C52单片机的P1口连接,通过查询按键是否被按下来判断进行计数或者清零。若按下计数健,则单片机控制两位一体的共阳极数码管显示从00开始的数字,按下一次,则数字加一,一次类推;若按下清零键,则程序返回程序开始处,并且数码管显示00。

2 硬件及软件设计 2.1 硬件系统 2.1.1 硬件系统设计 此设计是在单片机最小系统的基础上进行开发和拓展,增加了按键电路和和数码管显示电路,由于单片机输出电流不足以驱动数码管发光,所以数码管需要驱动电路。我们采用了三极管对数码管电流进行放大,使电流大小达到要求值。 2.1.2 单元电路设计 基本框架如下图2.1 2.1基本框架

1.STC89C52芯片 STC89C52RC芯片包括: 8k字节 Flash,512字节RAM, 32位I/O口 线,看门狗定时器,两个数据指针, 三个16位定时器/计数器,一个6向 量2级中断结构,全双工串行口,片 内晶振及时钟电路。STC89C52RC芯片 可降至0Hz静态逻辑操作,时钟频率 0-80MHz,支持2种软件可选择节电 模式。空闲模式下,CPU停止工作, 允许RAM、定时器/计数器、串口、中 断继续工作。掉电保护方式下,RAM 内容被保存,振荡器被冻结,单片 机一切工作停止,直到下一个中断或 硬件复位为止。8位微控制器8K字节 在系统可编程。芯片如图2.4所示。 图2.4 STC89C52芯片 2.按键电路 K1键为启动键,K2键为清零键,K3键为计数键,通过按钮的连接,实现开始、计数清零功能,连接电路如图2.5所示。 图2.5 按键电路

五层楼电梯运行控制逻辑设计 摘要:电梯是高层建筑不可缺少的运输工具,用于垂直运送乘客和货物,传统的电梯控制系统主要采用继电器,接触器进行控制,其缺点是触点多,故障率高、可靠性差、维修工作量大等,本设计根据电梯自动控制的要求利用Verilog语言编写并完成系统设计,在利用软件仿真之后,下载到了FPGA上进行硬件仿真。FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了之前的可编程器件门电路数有限及速度上的缺点。 关键词:电梯控制FPGA Verilog软件设计硬件设计 在当今社会,随着城市建设的不断发展,高层建筑的不断增多,电梯作为高层建筑中垂直运行的交通工具已与人们的日常生活密不可分。目前电梯控制系统主要有三种控制方式:继电路控制系统(早期安装的电梯多位继电器控制系统),FPGACPLD [1] 的控制系统、微机控制系统。继电器控制系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,目前已逐渐被淘汰,而微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷。而FPGACPLD控制系统由于运行可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点 [2] ,倍受人们重视等优点,已经成为目前在电梯控制系统中使用最多的控制方式,目前也广泛用于传

统继电器控制系统的技术改造。 随着现代化城市的高度发展,每天都有大量人流及物流需要输送,因此在实际工程应用中电梯的性能指标相当重要,主要体现在:可靠性,安全性,便捷快速性。电梯的可靠性非常重要,直接或间接的影响着人们的生产,生活,而电梯的故障主要表现在电力拖动控制系统中,因此要提高可靠性也要从电力拖动控制系统入手。 本次设计尝试用Verilog实现电梯控制器部分,进行了多层次的电梯控制,也进行了软件及硬件上的仿真验证,时序分析以保证设计的正确。在设计中先用软件进行模拟仿真,然后又下载到FPGA开发板上进行硬件仿真,以确保设计的正确性。 1电梯的设计分析 1.1 系统的需求分析及系统描述 设计一个电梯运行控器,该电梯有5层楼,设计的电梯调度算法满足提高服务质量、降低运行成本的原则;电梯的内部有一个控制面板,它负责按下请求到的楼层,并且显示当前尚未完成的目的地请求,当到达该楼层以后自动撤销本楼层的请求,即将面板灯熄灭;除1层和5层分别只有上和下按钮外,其余每个楼层(电梯门口旁)的召唤面板都有两个按钮,分别指示上楼和下楼请求。当按下后,对应按钮灯亮。如果电梯已经到达该楼层,按钮灯熄灭;电梯的外部面板会显示电梯当前所在的楼层,及上行还是下行(暂停显示刚才运行时的状态);电梯向一个方向运行时,只对本方向前方的请求进行应答,直到本方向前方无请求时,才对反方向的请求进行应答。当前内部控制面板上有的请求,只要经过所在楼层均会立即响应.

郑州轻工业学院 电子技术课程设计 题目 _基于FPGA的计数器设计___ _________________________ 学生姓名 _ XXX_________________ 专业班级 _电子信息工程10-01班____ 学号 _5401001030XXX__________ 院(系)电气信息工程学院___ ____ 指导教师 _杜海明耿鑫____________ 完成时间20XX年06月22日_______

郑州轻工业学院 课程设计任务书 题目基于FPGA的计数器的程序设设计_______________ 专业、班级电子信息工程学号姓名 _____ 主要内容、基本要求、主要参考资料等: 主要内容: 要求学生使用硬件描述语言(Verilog 或者VHDL)设计基于FPGA的计数器的 源程序。实现如下功能:显示1个0-9999的四位计数器;四位七段数码管的译码与 显示。理解数码管的译码原理,同时需要做一个分频器,理解时钟分频的原理及意 义。 基本要求: 1、学会quartusII的使用,掌握FPGA 的程序设计方法。 2、掌握硬件描述语言语法。 3、程序设计完成后要求在quartusII中实现功能仿真。 主要参考资料: 1、. [M]..20XX,4 2、陈怀琛.MATLAB及在电子信息课程中的应用[M].北京:电子工业出版 社.20XX,1 完成期限:20XX.6.21—20XX.6.25 指导教师签名: ________________ 课程负责人签名: ___________________ 20XX年6月18日

目录

基于FPGA的计数器的程序设设计 摘要 本文介绍了一种基于FPGA的,由顶层到底层设计的数字频率计。本文主要包括该频率计的设计基础和实现方法以及译码与显示等内容,描述了它的设计平台、工作原理和软硬件实现。本设计主要有分频器、四位计数器、16位锁存器以及数码管显示电路。计数器设计采用VHDL硬件描述语言编程,极大地减少了硬件资源的占用,仿真与分析结果表明,该数字频率计性能优异,软件设计语言灵活,硬件简单,速度快。 关键词FPGA 计数器 VHDL

郑州工业应用技术学院 课程设计说明书 题单片机脉冲信号测量 姓名: 院(系):信息工程学院专业班级:计算 机科学与技术学号: 指导教师: 成绩: 时间:年月日至年月日

摘要 脉冲信号测量仪是一种常用的设备,它可以测量脉冲信号的脉冲宽度,频率等参数,并用十进制数字显示出来。利用定时器的门控信号GATE进行控制可以 实现脉冲宽度的测量。在单片机应用系统中,为了便于对LED显示器进行管理,需要建立一个显示缓冲区。本文介绍了基于单片机AT89C51的脉冲信号参数测量仪的设计。该设计可以对脉冲信号的宽度,频率等参数进行测量。 关键词:脉冲信号;频率;宽度;单片机AT89C51

目录 摘要............................................................... I 目录............................................................... II 第一章技术背景及意义 (1) 第二章设计方案及原理 (2) 第三章硬件设计任务 (3) 第四章软件结论 (12) 第五章参考文献 (13) 第六章附录 (14)

第一章技术背景及意义 单片机微型计算机是微型计算机的一个重要分支,也是颇具生命力的机种。单片机微型计算机简称单片机,特别适用于控制领域,故又称为微控制器。通常,单片机由单块集成电路芯片构成,内部包含有计算机的基本功能部件:中央处理器、存储器和I/O 接口电路等。因此,单片机只需要和适当的软件及外部设备相结合,便可成为一个单片机控制系统。由于单片机稳定可靠、物美价廉、功耗低,所以单片机的应用日益广泛深入,涉及到各行各业,如工业自动化、智能仪表与集成智能传感器、家用电器等领域。单片机应用的意义绝不仅限于它的广阔范围以及带来的经济效益,更重要的意义在于,单片机的应用正从根本上改变着传统的控制系统的设计思想和设计方法。从前必须由模拟电路或数字电路实现的大部分控制功能,现在使用单片机通过软件就能实现了。随着单片机应用的推广普及,单片机控制技术将不断发展,日益完善。因此,本课程设计旨在巩固所学的关于单片机的软件及硬件方面的知识,激发广大学生对单片机的兴趣,提高学生的创造能力,动手能力和将所学知识运用于实践的能力。 中断功能是一种应用比较广泛的功能,它指的是当CPU正在处理某件事情的时候,外部发生了某一件事(如一个电平的变化,一个脉冲沿的发生或定时器计数溢出等)请求CPU迅速去处理,于是,CPU暂时终止当前的工作,转去处理所发生的事件。中断服务处理完该事件以后,再回到原来被中止的地方继续原来的工作,这样的过程称为中断。本文中用到了定时器T0溢出中断,以实现软件延时。脉冲信号测量仪是一种常用的设备,它可以测量脉冲信号的脉冲宽度,脉冲频率等参数。

湖南工业大学 课程设计 资料袋 理学学院(系、部)2012 ~ 2013 学年第 1 学期 课程名称单片机应用系统指导教师周玉职称副教授学生姓名张思远专业班级电子科学102 学号10411400223 题目对外部脉冲计数系统的设计 成绩起止日期2013 年01 月06 日~2013 年01 月10 日 目录清单

湖南工业大学 课程设计任务书 2012 —2013 学年第1 学期 理学院学院(系、部)电子科学专业102 班级 课程名称:单片机应用系统 设计题目:对外部脉冲计数系统的设计 完成期限:自2013 年01 月06 日至2013 年01 月10 日共 1 周

指导教师(签字):年月日系(教研室)主任(签字):年月日

附件三 (单片机应用系统) 设计说明书 (题目) 对外部脉冲计数系统的设计 起止日期:2013 年01 月06 日至2013 年01 月10 日 学生姓名张思远 班级电子科学102 学号10411400223 成绩 指导教师(签字) 电气与信息工程学院 2012年12 月10 日

一、设计任务: 1.1 外部脉冲自动计数,自动显示。 1.1.1设计一个255计数器:0-255计数,计满后自动清0,重 新计数(在数码管中显示)。 1.1.2设计一个50000计数器:0-50000计数,计满后自动清0, 重新计数(在数码管中显示)。 注:要求首先采用PROTEUS完成单片机最小系统的硬件电路 设计及仿真;程序仿真测试通过后,再下载到单片机实训 板上执行。 二、硬件设计介绍: ※STC89C52单片机; ※6位共阴或者共阴极数码管; ※外部晶振电路; ※ISP下载接口(In system program,在系统编程); ※DC+5V电源试配器(选配); ※ISP下载线(选配) ※6个PNP(NPN)三极管 ※12个碳膜电阻 三、硬件设计思路 方案一:五个1位7段数码管,无译码器 方案二:五个1位7段数码管,译码器 方案三:1个6位7段数码管,译码器 方案四:1个6位7段数码管,无译码器 考虑实际中外围设备、资金、单片机资源利用率、节省端口数量,可实行性以及连接方便等问题,采用6为数码管(共阳或者共阴极)由于实际中没买到6位的,采用2个三位数码管并接组合一个6位数码管形式;由于实际P口驱动能力有限,故采用6位三极管增大驱动能力,已便足以使得6位数码管亮度明显正常工作,增加6个电阻限流保护数码管不被烧坏。让数码管a-g7段分别接P1.6—P1.0,6位位选分别接P2.5—P2.0。 方法一:共阴极数码管 硬件图1.0所示:通过npn管放大后,段选高电平有效,位选低电平有效

一、概述 1.1 电子密码锁的现状 随着我国对外开放的不断深入,高档建筑发展很快,高档密码锁具市场的前景乐观。我国密码锁具行业对密码锁具高新技术的投入正逐年增大,高档密码锁的市场需求也逐年增加。在安防工程中,锁具产品是关系到整个系统安全性的重要设备,所以锁具产品的优劣也关系了整个安防工程的质量和验收。 目前,市场上比较先进的智能电子密码锁分别有:IC卡电子密码锁、射频卡式电子密码锁、红外遥控电子密码锁、指纹识别电子密码锁和瞳孔识别电子密码锁等。IC卡电子密码锁成本低,体积小,卡片本身无须电源等优点占领了一定的市场份额,但是由于有机械接触,会产生接触磨损,而且使用不太方便,在一定程度上限制了它的应用;射频卡式电子密码锁是非接触式电子密码锁,成本也不太高,体积跟IC卡密码锁相当,卡片使用感应电源,重量很轻,技术成熟,受到了广泛的欢迎,但是与IC卡电子密码锁相比,成本偏高;指纹识别电子密码锁和瞳孔识别电子密码锁可靠性很高,安全性是目前应用系统中最高的,但是成本高昂,还没进入大众化使用阶段。 在国外,美国、日本、德国的电子密码锁保密性较好,并结合感应卡技术,生物识别技术,使电子密码锁系统得到了飞跃式的发展。这几个国家的密码锁识别的密码更复杂,并且综合性比较好,已经进入了成熟期,出现了感应卡式密码锁,指纹式密码锁,虹膜密码锁,面部识别密码锁,序列混乱的键盘密码锁等各种技术的系统,它们在安全性,方便性,易管理性等方面都各有特长,新型的电子密码锁系统的应用也越来越广。 基于FPGA的电子密码锁是新型现代化安全管理系统,它集微机自动识别技术和现代安全管理措施为一体,它涉及电子,机械,计算机技术,通讯技术,生物技术等诸多新技术。它是解决重要部门出入口实现安全防范管理的有效措施,适用各种场合,如银行、宾馆、机房、军械库、机要室、办公间、智能化小区、工厂、家庭等。 在数字技术网络技术飞速发展的今天,电子密码锁技术得到了迅猛的发展。它早已超越了单纯的门道及钥匙管理,逐渐发展成为一套完整的出入管理系统。它在工作环境安全、人事考勤管理等行政管理工作中发挥着巨大的作用。在该系统的基础上增加相应的辅助设备可以进行电梯控制、车辆进出控制,物业消防监控、餐饮收费、私家车库管理等,真正实现区域内一卡智能管理。

脉冲边缘检测法: Reg[2:0] key_rst; //用来保存按键的值 Reg[2:0] key_rst_r; //用来保存key_rst的值 always @(posedge clk or negedge rst) begin if(!rst)key_rst<=3’b111; else key_rst<={key1,key2,key3};//将三个按键的值都赋给key_rst end always @ (posedge clk or negedge rst) begin if(!rst) key_rst_r<=3’b111; else key_rst_r<=key_rst; end wire[2:0] key_an; assign key_an=key_rst_r&(~key_rst);//实现了记录由低电平按下的目的到此就可以判断有按键按下或有抖动。这两个是那一个到此还不确定。 Reg[2:0] low_sw; Reg[2:0] low_sw_r; Reg[19:0] cnt; always @(posedge clk or negedge rst) begin if(!rst) cnt<=20’d0; else if(key_an) cnt<=20’d0; else cnt<=cnt+1’b1; end always @(posedge clk or negedge clk) begin if(!rst) low_sw<=3’b111; else if(cnt==20’hfffff) low_sw<={key1,key2,key3}; end always @(posedge clk or negedge rst) begin if(!rst) low_sw_r<=3’b111; else low_sw_r<=low_sw; end wire[2:0] led_ctrl assign led_ctrl=low_sw_r&(~low_sw); 到此就可以判断是按键按下还是抖动了,如果led_ctrl=1那就是按键按下了,如果led_ctrl=0,则是抖动。 注:开始时按键接的脚为高电平。当按键按下时按键对应的脚为低电平。

基于FPGA的计数器的程序设计 摘要 本文介绍了一种基于FPGA的,由顶层到底层设计的数字计数器。本文主要包括该计数器的设计基础和实现方法以及译码与显示等内容,描述了它的设计平台、工作原理和软硬件实现。本设计主要有分频器、四位计数器、16位锁存器以及数码管显示电路四个模块组成。计数器各模块设计采用VHDL硬件描述语言编程,极大地减少了硬件资源的占用,仿真与分析结果表明,该数字计数器性能优异,软件设计语言灵活,硬件简单,速度快。 关键词FPGA计数器VHDL分频器

目录 基于FPGA的计数器的程序设计 (1) 摘要 (1) 1 绪论 (3) 1.1 FPGA简介 (3) 1.2硬件描述语言VHDL简介 (3) 1.3开发工具Quartus II简介 (4) 2整体设计方案 (4) 3各功能模块设计及仿真 (5) 3.1分频器的设计 (5) 3.1.1分频器设计原理 (5) 3.1.2源程序及波形仿真 (6) 3.1.3分频器RTL 电路图 (7) 3.2计数器的设计 (7) 3.2.1分频器设计原理 (7) 3.2.2源程序及波形仿真 (8) 3.2.3 RTL 电路图 (11) 3.3锁存器的设计 (11) 3.3.1锁存器设计原理 (11) 3.3.2锁存器源程序及波形仿真 (12) 3.3.3锁存器RTL电路图 (13) 3.4显示部分的设计 (13) 3.4.1七段数码管显示原理 (13) 3.4.2七段数码管显示源程序及波形仿真 (15) 3.4.3七段数码管显示RTL 电路图 (16) 4系统顶层设计 (17) 4.1.1自顶向下的设计方法 (17) 4.1.2 顶层设计源程序及其仿真波形 (17) 4.1.3系统顶层RTL 电路图 (20) 5总结 (21) 参考文献 (22)

变频器的电压检测电路(新) ——正弦变频器电压检测实际电路分析 一、电路构成和原理简析 电压检测电路,是变频器故障检测电路中的一个重要组成部分,旨在保障使IGBT 逆变电路的工作电源电压在一特定安全范围以内,若工作电源危及IGBT (包含电源本身的储通电容)器件的安全时,实施故障报警、使制动电路投入工作、停机保护等措施。此外,少数机型还有对输出电压的检测,在一定程度上,起到对IGBT 导通管压降检测的同样作用,取代驱动电路中IGBT 的管压降检测电路。 1、电压检测电路的构成、电压采样方式及故障表现 图1 电路检测电路的构成(信号流程)框图 1、电压检测电路的电压采样形式(前级电路) 1)直接对DC530V 电压采样 78L05C 8 P N 图2 DC530V 电压检测电路之一 直接对P 、N 端DC530V 整流后电源电压进行进行采样,形成电压检测信号。如阿尔法ALPHA2000型变

频器的电压检测电路,如图2所示。 电路中U14线性光耦合器的输入侧供电,由开关变压器的独立绕组提供的交流电压,经整流滤波、由78L05稳压处理得到5V 电源所提供,电源地端与主电路N 端同电位。输出侧供电,则由主板+5V 所提供。 直流回路P 、N 端的DC530V 电压,直接经电阻分压,取得约120mV 的分压信号,输入U14(线性光耦合器,其工作原理前文已述)进行光、电隔离与线性放大后,在输出端得到放大了的检测电压信号,再由LF353减法放大器进一步放大,形成VPN 直流电压检测信号,经CNN1端子,送入MCU 主板上的电压检测后级电路。 2)由开关变压器次级绕组取得采样电路信号 +5V -42V 图3 DC530V 电压检测电路之二 N +5V N1输入电压波形示意图V T 截止 VT 饱合导通 0V 530V 5V 0V -42V N3输出电压波形示意图 压采样等效电路T1 图4 直流回路电压采样等效电路及波型示意图 主电路的DC550V 直流电压检测信号,并不是从主电路的P 、N 端直接取得,而是“间接”从开关电源的二次绕组取出,这是曾经令一些检修人员感到困惑、找不到电压检测信号是从何处取出的一件事情,也成为该部分电路检修的一个障碍。电压采样电路如上图4所示。 在开关管VT 截止期间,开关变压器TRAN 中储存的磁能量,由次级电路进行整流滤波得到+5V 工作电源,释放给负载电路;在VT 饱和导通期间,TC2从电源吸取能量进行储存。 N3二级绕组上产生的电磁感应电压,正向脉冲出现的时刻对应开关管的截止时间,宽度较大,幅值较低,经二极管D12正向整流后提供负载电路的供电,有电流释放回路;反向脉冲出现的时刻对应开关管的饱和导通时间,宽度极窄,但并不提供电流输出,回路的时间常数较大(不是作为供电电源应用,只是由R 、C 电路取得电压检测信号),故能在电容C17上维持较高的幅值。开关管VT 饱合导通时,相当于将N1绕组直接接入530V 电源,因而在同一时刻N3绕组此时所感应的负向脉冲电压,是直接反映N1绕组供电电压高低的,并与其成线性比例关系——N3绕组感应电压的高低,仅仅取决于N1、N3绕组的匝数比。整

南昌航空大学实验报告 二0一一年九月二十九日 课程名称:单片微型机实验名称:脉冲计数和电脑时钟程序 班级: 080611 学生姓名:学号: 08061108 指导教师评定:签名: 一、实验目的 1、熟悉8031定时/计数功能,掌握定时/计数初始化编程方法; 2、熟悉MCS—51定时器、串行口和中断初始化编程方法,了解定时器应用在实时控制中程序的设计技巧; 3、编写程序,从DVCC系列单片机实验仪键盘上输入时间初值,用定时器产生0.1S定时中断,对时钟计数器计数,并将数值实时地送数码管显示。 二、实验内容及要求 1、脉冲计数 对定时器0外部输入的脉冲进行计数,并送显示器显示。程序框图如下: 图1 二进制转换子程序 2、电脑时钟程序程序 程序框图如下:

图2 定时中断服务程序 三、实验步骤及操作结果 1、脉冲计数程序 (1) 当DVCC 单片机仿真实验系统独立工作时 1) 把8032CPU 的P3.4插孔接T0—T7任一根信号线或单脉冲输出空“SP ”。 2)用连续方式从起始地址02A0H 开始运行程序(按02A0后按EXEC 键)。 3)观察数码管显示的内容应为脉冲个数。 (2) 脉冲计数程序(源文件名:Cont .Asm )。汇编程序代码如下: ORG 02A0H CONT: MOV SP,#53H MOV TMOD,#05H ;初始化定时/计数器 MOV TH0,#00H MOV TL0,#00H SETB TR0 ;允许定时/计数中断 CONT1: MOV R2,TH0 ;取计数值 MOV R3,TL0 LCALL CONT2 ;调二转十进制子程序 MOV R0,#79H MOV A,R6 LCALL PWOR MOV A,R5 LCALL PWOR MOV A,R4 LCALL PWOR LCALL DISP ;调显示子程序 SJMP CONT1 ;循环 CONT2: CLR A ;清R4、R5、R6 MOV R4,A MOV R5,A MOV R6,A MOV R7,#10H CONT3: CLR C ;R2、R3左移,移出的位送CY MOV A,R3 RLC A

基于FPGA的Verilog-HDL数字钟设计--

————————————————————————————————作者:————————————————————————————————日期:

基于FPGA的Verilog HDL数字钟设计 专业班级姓名学号 一、实验目的 1.掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程; 2.熟悉一种EDA软件使用; 3.掌握Verilog设计方法; 4.掌握分模块分层次的设计方法; 5.用Verilog完成一个多功能数字钟设计; 6.学会FPGA的仿真。 二、实验要求 功能要求: 利用实验板设计实现一个能显示时分秒的多功能电子钟,基本功能: 1)准确计时,以数字形式显示时、分、秒,可通过按键选择当前显示时间范围模式; 2)计时时间范围00:00:00-23:59:59 3)可实现校正时间功能; 4)可通过实现时钟复位功能:00:00:00 扩展功能: 5)定时报:时间自定(不要求改变),闹1分钟(1kHz)---利用板上LED或外接电路实现。 6)仿广播电台正点报时:XX:59:[51,53,55,57(500Hz);59(1kHz)] ---用板上LED或外接 7)报整点时数:XX:00:[00.5-XX.5](1kHz),自动、手动---用板上LED或外接

8)手动输入校时; 9)手动输入定时闹钟; 10)万年历; 11)其他扩展功能; 设计步骤与要求: 1)计算并说明采用Basys2实验板时钟50MHz实现系统功能的基本原理。 2)在Xilinx ISE13.1 软件中,利用层次化方法,设计实现模一百计数及显示的电路系 统,设计模块间的连接调用关系,编写并输入所设计的源程序文件。 3)对源程序进行编译及仿真分析(注意合理设置,以便能够在验证逻辑的基础上尽快 得出仿真结果)。 4)输入管脚约束文件,对设计项目进行编译与逻辑综合,生成下载所需.bit文件。 5)在Basys2实验板上下载所生成的.bit文件,观察验证所设计的电路功能。 三、实验设计 功能说明:实现时钟,时间校时,闹铃定时,秒表计时等功能 1.时钟功能:完成分钟/小时的正确计数并显示;秒的显示用LED灯的闪烁做指示; 时钟利用4位数码管显示时分; 2.闹钟定时:实现定时提醒及定时报时,利用LED灯代替扬声器发出报时声音; 3.时钟校时:当认为时钟不准确时,可以分别对分钟和小时位的值进行调整; 4.秒表功能:利用4个数码管完成秒表显示:可以实现清零、暂停并记录时间等功能。 秒表利用4位数码管计数; 方案说明:本次设计由时钟模块和译码模块组成。时钟模块中50MHz的系统时钟clk分频产

1. 讲废话 最近闲得蛋疼,翻阅了一下以前的项目笔记,想起去年折腾的一个小玩意儿。记得当时是由于项目需要,boss找到我,说主板上有一个单片机,会发出heartbeat信号(就是MCU等一些芯片的心跳信号,只要芯片活着,就会一直发送固定频率的脉冲出去,如果芯片挂了,heartbeat就一直为0或1),能不能用CPLD判断这个信号是否处于正常状态?(说白了,也就是判断单片机是否还活着)。于是着手研究了一下这个heartbeat信号,用示波器测了一下,是一个标准的脉冲,频率为1HZ,占空比为50%,捯饬了两个小时,给出的解决方案是:每3s钟,计算一次上升沿的个数,如果此数值等于0,则heartbeat信号异常(用0表示),否则heartbeat信号正常(用1表示)。 把这个问题和方案贴出来,一是觉得实用性比较强,以前也没有看到有人做过,二是此解决方案对于其他同类问题有启发作用,只要弄懂此个案,其他问题也会触类旁通,易于解决。 现在给出方案的verilog源码,供大家研究,代码已通过项目验证,可靠好用。 2. 晒干货 ps. 带★号处可根据需要进行修改. /*********************************************************************** ******************* Author: Bob Liu E-mail:shuangfeiyanworld@https://www.doczj.com/doc/6713200219.html, Device: LCMX0256C-3T100C Tool: Diamond 1.1 Function:判断脉冲输入信号是否正常 Version: 2012-1-11 v1.0 ************************************************************************ ******************/ module pulse_in_status ( input CLK, // 基准时钟,50M input pulse_in, // 被测脉冲 output reg pulse_in_status // 指示被测脉冲正常与否,1表示正常,0异常 ); reg [1 :0] temp; // 电平值寄存器 reg [31:0] CNT,CNT2; reg [3 :0] pos_edge; // 上升沿个数 parameter delay = 50_000;

基于FPGA的定时器/计数器的设计与实现 摘要 本课题旨在用EDA工具与硬件描述语言设计一个基于Altera公司的FPGA 16位计数器\定时器,可对连续和非连续脉冲进行计数,并且计数器在具有计数定时功能基础上,实现简单脉宽调制功能和捕获比较功能。本设计采用QuartusII编译开发工具使用VerilogHDL 设计语言进行设计,并采用了由上而下的设计方法对计数器进行设计,体现了VerilogHDL 在系统级设计上自上而下设计风格的优点。本设计中采用了三总线的设计方案,使设计更加简洁与规范。本设计所有模块与功能均在Quartus II 7.0_1.4G_Liwz版本下通过编译与仿真,实现了定时器/计数器的设计功能。 关键词:VerilogHDL硬件描述语言;QuartusII;FPGA;定时器/计数器

FPGA-based timer / counter design and implementation This topic aims to use EDA tools to design a 16 bit counter \ timer based on Altera's FPGA by hardware descripe language, which can count continuous and discontinuous pulset, and the counter with the function of capture and PWM. This design uses VerilogHDL language and top-down design method to design the counter on QuartusII compile tool, the design reflect the advantages of VerilogHDL top-down design in system-level design. The design uses a three-bus design, which make design much more specifications and concise. The design and function of all modules are compiled and simulationed on the Quartus II 7.0_1.4G_Liwz versions, and achieve the timer / counter’s features. Key words: VerilogHDL hardware description language; QuartusII; FPGA; timer / counter