在FPGA设计中怎样检测脉冲边沿

- 格式:docx

- 大小:120.50 KB

- 文档页数:1

一种“边沿检测电路”和“脉宽检测电路”的设计方法

关于“边沿检测电路”和“脉宽检测电路”有很多设计方法,以下是一种比较常见的设计方法,大部分的“边沿检测电路”和“脉宽检测电路”都是分别以这两种电路为基础实现的,也是我们在芯片设计中经常采用的方法:

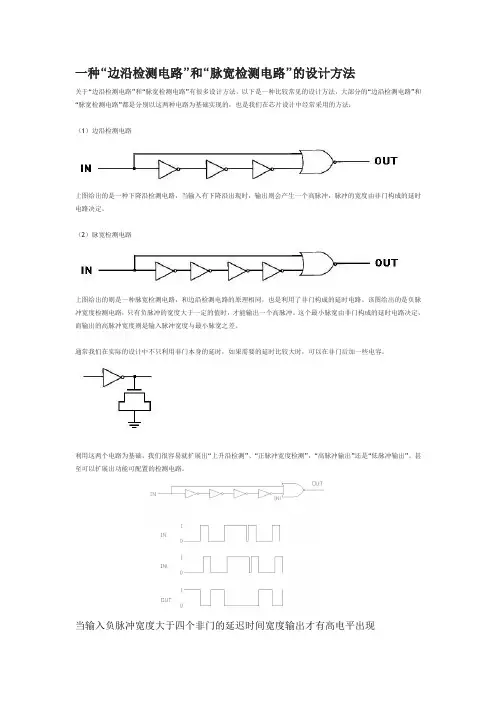

(1)边沿检测电路

上图给出的是一种下降沿检测电路,当输入有下降沿出现时,输出则会产生一个高脉冲,脉冲的宽度由非门构成的延时电路决定。

(2)脉宽检测电路

上图给出的则是一种脉宽检测电路,和边沿检测电路的原理相同,也是利用了非门构成的延时电路。

该图给出的是负脉冲宽度检测电路,只有负脉冲的宽度大于一定的值时,才能输出一个高脉冲。

这个最小脉宽由非门构成的延时电路决定,而输出的高脉冲宽度则是输入脉冲宽度与最小脉宽之差。

通常我们在实际的设计中不只利用非门本身的延时,如果需要的延时比较大时,可以在非门后加一些电容。

利用这两个电路为基础,我们很容易就扩展出“上升沿检测”、“正脉冲宽度检测”,“高脉冲输出”还是“低脉冲输出”。

甚至可以扩展出功能可配置的检测电路。

当输入负脉冲宽度大于四个非门的延迟时间宽度输出才有高电平出现

当输入正脉冲大于四个非门的延迟时间宽度输出才有高电平出现。

基于FPGA的时间间隔测量仪的设计设计思路:1. 采集信号:FPGA通过引脚或者其他接口采集待测信号,并将其统一转化为数字信号进行处理。

2. 时钟同步:使用定时器或者PLL对采集到的信号进行时钟同步,以确保后续处理的准确性。

3. 脉冲宽度测量:利用FPGA的高速计数器进行脉冲宽度的测量。

通过计数器记录信号的上升沿和下降沿之间的时钟周期数,再根据时钟频率将其转化为时间。

4. 时间间隔测量:根据采集到的两个信号的上升沿或者下降沿的时间戳信息计算时间间隔,同样利用高速计数器完成。

其中,时间间隔是通过记录两个信号的上升沿或者下降沿之间累积的时间周期数来计算的。

5. 数据处理:将测量到的脉冲宽度和时间间隔信息进行数字信号处理,例如平均值、最大值、最小值、标准差等统计分析。

6. 结果显示:将处理后的结果通过数码管、LCD屏幕、计算机等方式进行显示,以方便用户观察和分析。

该设计中,FPGA作为核心处理器,具有高速计数器、PLL等硬件模块,可以提供高精度和高测量速率的能力。

相较于传统基于微处理器或者DSP的仪器,基于FPGA的时间间隔测量仪具有以下优点:1. 快速响应和高测量速率:FPGA具备并行计算的能力,可以同时处理多个信号,提供更高的测量速率。

2. 高精度测量结果:FPGA的高速计数器可以提供高精度的计数和测量能力,减小了测量误差。

3. 可编程性和可扩展性:FPGA具有可编程性,可以根据不同的应用场景进行定制和优化设计;同时也方便后期的新功能扩展。

在实际设计过程中,需要进行以下步骤:1. 硬件设计:包括FPGA的选择、电路连接、时钟同步、高速计数器等基本硬件模块的设计。

2. 软件编程:通过HDL语言进行FPGA的编程,实现采集、同步、计数和数据处理等功能。

3. 系统测试:对设计的时间间隔测量仪进行系统测试,验证其测量精度和稳定性等指标。

4. 优化和调试:根据测试结果进行优化和调试,提高测量精度和速率。

虽然基于FPGA的时间间隔测量仪具有很多优点,但也需要考虑以下问题:1. 成本:FPGA的成本相对较高,相较于传统的微处理器或者DSP方案成本较高。

脉冲信号测量上升沿和下降沿定义脉冲信号,这东西听起来有点复杂对吧?不过别急,咱们慢慢来,给你讲讲它的上升沿和下降沿。

这些术语听起来挺高大上的,但要是你把它们拆开来看,就会发现其实也没那么神秘。

什么叫脉冲信号呢?想象一下,你按下一个开关,灯泡就亮了;再按一次,灯泡又灭了。

这就是脉冲信号,信号像灯泡一样是闪亮的,忽明忽暗的。

你要是仔细看,脉冲信号并不是一开始就亮个不停的,它总是“闪”一下,又灭了,接着再“闪”一下。

哎,像极了偶尔停电的生活,每当灯泡闪一下,总会让你心跳加速,对吧?但是,咱们今天要讨论的,不是这“闪”一下,而是“闪”的时候的动作,具体来说,就是上升沿和下降沿。

咱们先说上升沿。

它是什么呢?你可以把它想象成脉冲信号从低到高的转折点,像你从懒洋洋的床上爬起来,顿时充满活力。

想象一下,一个电压从零开始,突然嗖地一下冲上去了,就像火箭发射的瞬间,那一刹那,能量爆发,动力十足!这时候,信号从“低谷”开始快速上升,跳过了很多的零星点,直接来到了一个新的高度。

上升沿就是这个突如其来的变化,它就像是一个强力的“加速器”,把信号从慢悠悠的状态一下带到一个“高能”阶段。

哎,你是不是想问了,上升沿到底好不好?说白了,上升沿好不好看要看什么信号。

如果你需要信号迅速变化,那它可就非常给力了。

但是,如果信号变化得太快呢?就会造成一些不稳定的情况。

信号变化的过快,可能会引起误差,甚至导致系统出错。

所以,信号的上升沿可不是一味追求速度,得有一定的控制和规律,才能让整个系统运行得稳稳当当的。

再说说下降沿吧。

下降沿其实就跟上升沿差不多,不过是信号从高处掉下来的过程。

你可以把它想象成你从高高的山顶突然滑下来,呼——风一样的速度,哎呀,刺激得很!同样的道理,脉冲信号从高电平跌落到低电平的过程,就是下降沿。

这时候信号就像是一颗陨石从天而降,迅速失去它的高度,掉到最低点。

上升沿把信号从低处拉到了高点,而下降沿则把它从高处摔到低处。

173脉冲参数测试仪是在信号类常用的一种仪器,用它可以测量峰峰值、有效值、频率、上升沿和下降沿时间、占空比等。

大型台式的测试仪功能比较齐全,而手提便携式的功能还没那么完善且生产数量较少,测量精度也没有台式的高。

现在最便携式的测量仪器普遍用的就是万用表,它可以测量直流电压、电阻、电流、电容等。

本设计采用FPGA作为主控芯片,以整形电路、控制电路、显示电路三大模块为基础,设计出测量峰峰值、频率、占空比、上升沿和下降沿时间的参数的脉冲参数测试仪。

本文主要介绍了三大模块电路,并对相应的硬软件设计思路方法进行阐述。

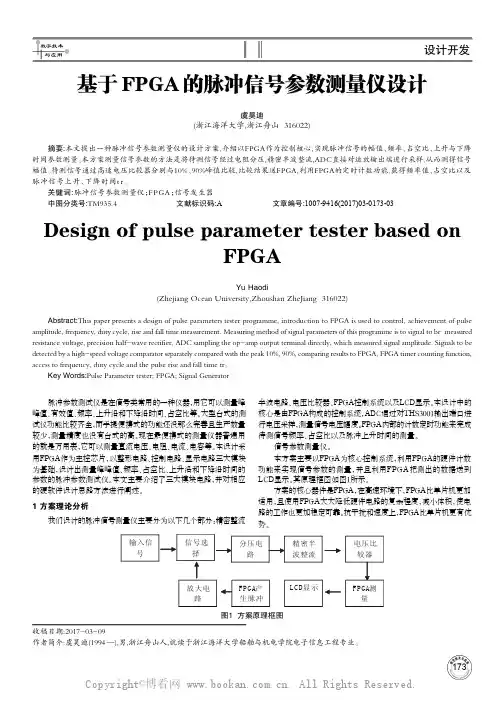

1 方案理论分析我们设计的脉冲信号测量仪主要分为以下几个部分:精密整流半波电路、电压比较器、FPGA控制系统以及LCD显示。

本设计中的核心是由FPGA构成的控制系统,ADC通过对THS3001输出端口进行电压采样,测量信号电压幅度。

FPGA内部的计数定时功能来完成待测信号频率、占空比以及脉冲上升时间的测量。

信号参数测量仪。

本方案主要以FPGA为核心控制系统,利用FPGA的硬件计数功能来实现信号参数的测量,并且利用FPGA把测出的数据送到LCD显示。

其原理框图如图1所示。

方案的核心器件是FPGA,在高速环境下,FPGA比单片机更加适用,且使用FPGA大大降低硬件电路的复杂程度,减小体积,使电路的工作也更加稳定可靠。

抗干扰和速度上,FPGA比单片机更有优势。

基于FPGA 的脉冲信号参数测量仪设计虞昊迪(浙江海洋大学,浙江舟山 316022)摘要:本文提出一种脉冲信号参数测量仪的设计方案,介绍以FPGA作为控制核心,实现脉冲信号的幅值、频率、占空比、上升与下降时间参数测量。

本方案测量信号参数的方法是将待测信号经过电阻分压,精密半波整流,ADC直接对运放输出端进行采样,从而测得信号幅值。

待测信号通过高速电压比较器分别与10%、90%峰值比较,比较结果送FPGA,利用FPGA的定时计数功能,获得频率值、占空比以及脉冲信号上升、下降时间t r 。

基于FPGA的脉冲信号参数测量仪作者:袁汇丰胡佳文郭成钧来源:《数字技术与应用》2018年第02期摘要:本设计利用FPGA作为数据处理和系统控制的核心,通过FPGA及其外围电路完成脉冲信号参数的测量。

其中外围电路由信号前置处理模块、双路比较器模块、显示模块等模块组成。

经前级电路处理后的信号送入FPGA,利用FPGA较强的信号处理能力完成对信号的测量,最后由LCD显示屏显示参数。

在实际应用中具有体积小、实时性好、工作效率高等特点。

关键词:FPGA;电压比较器;脉冲信号参数测量仪中图分类号:TM935.4 文献标识码:A 文章编号:1007-9416(2018)02-0068-02脉冲信号参数测量仪作为一种重要的电子测量仪器,其作用是测量脉冲信号的幅值、频率、占空比、上升时间等参数。

随着微电子技术与自动控制技术的发展,越来越多的FPGA器件正广泛应用于各种数字信号处理。

FPGA具有体系结构和逻辑单元灵活、集成度高、运行快、可靠性强等特点。

近年来,以虚拟仪器为代表的新型测量仪器异军突起,其突破了传统的电子测量仪器的制约,充分利用计算机技术,将软硬件相结合。

本设计中将FPGA应用于脉冲信号测量仪就是一个非常好的应用,使我们能够更好的了解FPGA在脉冲信号测量仪的应用中所体现出来的优势,减少了脉冲信号测量仪的复杂度。

1 系统设计原理及测量方案1.1 系统总方案本设计将输入信号经前端电路处理,可以将0.1-10V的信号整形成3.3V以下的方波,经过双路比较电路将比较结果送入FPGA测得与时间相关的三个参数,将处理后的信号送入FPGA,其中对于频率和占空比测量采用计数法和测周法相结合的方法。

利用A/D测量峰值用以得到脉冲信号的幅值,最后将测得的参数显示在LCD显示屏。

1.2 精密整流电路精密整流电路常运用于信号变换的场合,本设计将衰减后的信号整流成直流信号,鉴于信号的幅值较小,若直接采用二极管整流,考虑到二极管上的电压降,会使测量所得的数据存在较大误差。

基于Fpga的脉冲信号参数测试仪的设计与制作开题报告在我那乱得像被龙卷风席卷过的实验室里,我正对着一堆电路板和芯片发愁呢,就像一个迷失在沙漠里的旅人,看着满眼的黄沙(也就是那些电子元件),完全不知道从哪儿下手。

这时候,我的好伙伴小李晃悠过来了,他那副悠闲的样子,就好像这些难题在他眼里都是小儿科。

“嘿,你这愁眉苦脸的,是在跟这些小玩意儿较什么劲呢?”小李打趣道。

我无奈地叹了口气,“你看啊,我要做这个基于Fpga的脉冲信号参数测试仪的设计与制作,可我现在感觉就像无头苍蝇一样,毫无头绪。

”“哟,这听起来可挺酷的啊。

”小李来了兴致,“不过这脉冲信号参数测试仪到底是个啥玩意儿呢?听起来就像一个超级侦探,专门去探测脉冲信号的各种秘密似的。

”我被他的话逗笑了,“哈哈,你这个比喻还挺形象的。

简单来说呢,脉冲信号在很多地方都特别重要,就像人体的心跳一样,是很多电子设备正常工作的节拍器。

这个测试仪啊,就是要把脉冲信号的参数,像频率、幅度、脉宽这些,准确地测量出来。

”“哦,我明白了。

那为啥要用Fpga呢?”小李追问。

“这Fpga啊,就像是一个万能的积木盒子。

”我一边解释,一边用手比划着,“它可以根据我们的需求自由组合各种功能,灵活性特别高。

而且它处理速度快,就像一个超级大脑,能快速对脉冲信号进行分析处理。

不像一些传统的芯片,功能比较固定,就像被定好型的小机器人,只能做那几件事。

”在和小李的聊天中,我渐渐理清了思路。

我打算先从研究Fpga的基本结构和功能开始,这就好比盖房子要先了解砖头和水泥的特性一样。

我要深入学习它的可编程逻辑模块、输入输出模块等,这些都是构建测试仪的基础。

然后呢,就是设计脉冲信号的采集模块。

这可不容易,就像要在嘈杂的集市里准确捕捉到一种特定的声音一样。

我得考虑如何让这个模块能够精确地采集到脉冲信号,不能让其他干扰信号混进来,不然就像在一锅好汤里掉进了一只苍蝇,整个测量结果就全毁了。

在测量脉冲信号的频率方面,我想着可以利用Fpga内部的计数器。

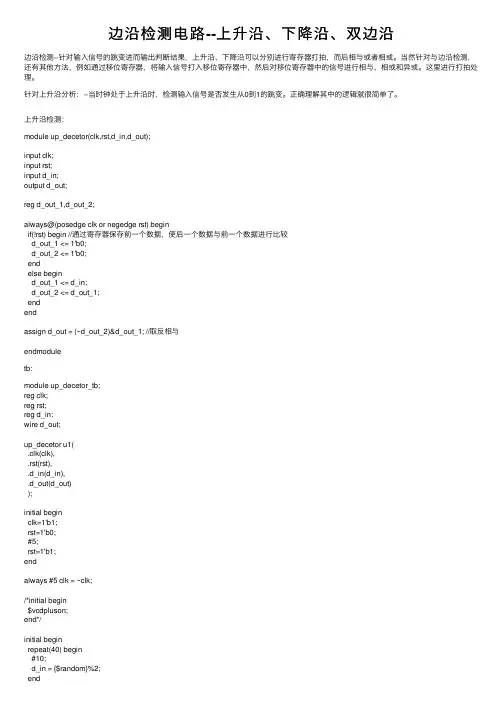

边沿检测电路--上升沿、下降沿、双边沿边沿检测--针对输⼊信号的跳变进⽽输出判断结果,上升沿、下降沿可以分别进⾏寄存器打拍,⽽后相与或者相或。

当然针对与边沿检测,还有其他⽅法,例如通过移位寄存器,将输⼊信号打⼊移位寄存器中,然后对移位寄存器中的信号进⾏相与、相或和异或。

这⾥进⾏打拍处理。

针对上升沿分析:--当时钟处于上升沿时,检测输⼊信号是否发⽣从0到1的跳变。

正确理解其中的逻辑就很简单了。

上升沿检测:module up_decetor(clk,rst,d_in,d_out);input clk;input rst;input d_in;output d_out;reg d_out_1,d_out_2;always@(posedge clk or negedge rst) beginif(!rst) begin //通过寄存器保存前⼀个数据,使后⼀个数据与前⼀个数据进⾏⽐较d_out_1 <= 1'b0;d_out_2 <= 1'b0;endelse begind_out_1 <= d_in;d_out_2 <= d_out_1;endendassign d_out = (~d_out_2)&d_out_1; //取反相与endmoduletb:module up_decetor_tb;reg clk;reg rst;reg d_in;wire d_out;up_decetor u1(.clk(clk),.rst(rst),.d_in(d_in),.d_out(d_out));initial beginclk=1'b1;rst=1'b0;#5;rst=1'b1;endalways #5 clk = ~clk;/*initial begin$vcdpluson;end*/initial beginrepeat(40) begin#10;d_in = {$random}%2;endendendmodule下降沿检测module down_decetor(clk,rst,d_in,d_out); input clk;input rst;input d_in;output d_out;reg d_out_1,d_out_2;always@(posedge clk or negedge rst) begin if(!rst) begind_out_1 <= 1'b0;d_out_2 <= 1'b0;endelse begind_out_1 <= d_in;d_out_2 <= d_out_1;endendassign d_out = (~d_out_1)&d_out_2; // endmoduletb:module down_decetor_tb; reg clk;reg rst;reg d_in;wire d_out;down_decetor u1(.clk(clk),.rst(rst),.d_in(d_in),.d_out(d_out));initial beginclk=1'b1;rst=1'b0;#5;rst=1'b1;endalways #5 clk = ~clk;initial begin$vcdpluson;endinitial begin#10;d_in=1'b1;#10;d_in=1'b0;#10;d_in=1'b0;#10;d_in=1'b1;#10;d_in=1'b0;#20;d_in=1'b1;#10;d_in=1'b1;#10;d_in=1'b0;#30;d_in=1'b1;#50;$finish();endendmodule双边沿检测:module double_decetor(clk,rst,d_in,d_out);input clk;input rst;input d_in;output d_out;reg d_out_1,d_out_2;always@(posedge clk or negedge rst) begin if(!rst) begind_out_1 <= 1'b0;d_out_2 <= 1'b0;endelse begind_out_1 <= d_in;d_out_2 <= d_out_1;endendassign d_out = d_out_1^d_out_2; //异或endmoduletb:module down_decetor_tb;reg clk;reg rst;reg d_in;wire d_out;double_decetor u1(.clk(clk),.rst(rst),.d_in(d_in),.d_out(d_out));initial beginclk=1'b1;rst=1'b0;#5;rst=1'b1;endalways #5 clk = ~clk;initial begin$vcdpluson;endinitial begin#10;d_in=1'b1;#20;d_in=1'b0; #10;d_in=1'b1; #10;d_in=1'b0; #10;d_in=1'b1; #10;d_in=1'b0; #20;d_in=1'b1; #10;d_in=1'b0; #30;d_in=1'b1; #50;$finish(); end endmodule。

测试与光电工程学院课程设计任务书电子科学与技术系班学生课题名称:脉冲序列检测器的设计课题要求:查找相关资料,确定基于FPGA的多路脉冲序列检测器的设计方案,要求能对多路脉冲序列信号进行检测。

课题容:1、系统设计要求:脉冲序列检测器广泛应用于现代数字通信系统中。

随着通信技术的发展,对多路脉冲序列信号检测要求越来越高,本实验设计一个基于FPGA的多路脉冲序列检测器。

设计完成后,经综合和仿真验证后,在FPGA中实现。

2、工作进度安排:查找相关资料,确定脉冲序列检测器设计方案 11月15日~11月21日第12周系统各模块的详细设计 11月22日~12月28日第13周系统仿真及修正 11月29日~12月5日第14周系统测试,课程设计报告的撰写 12月6日~12月10日第15周主要参考资料:【1】潘松,黄继业 EDA技术使用教程(第三版)科学2006【2】邬波,王曙光,胡建平有限状态机VHDL设计及优化信息技术 2004(01) 【3】欲晓 EDA技术与VHDL技术电子工业 2009.4【4】鄢靖丰,晓黎,王平用Verilog-HDL设计序列检测器 2005(11)【5】唐瑜,符兴吕,罗江用VHDL语寿实现序列信号的产生和检测 2008(09) 【6】蒋昊,哲英基于多种EDA工具的FPGA设计流程[J].微计算机信息,2007 【7】束礼宝,宋克柱,王砚方.伪随机数发生器的FPGA实现与研究[J].电路与系统学报,2003.8系负责人:指导教师:柴明钢时间:2010年11月10日摘要脉冲序列检测器广泛应用于现代数字通信系统中,随着通信技术的发展,对多路脉冲序列信号检测要求越来越高。

现代通信系统的发展方向是功能更强、体积更小、速度更快、功耗更低,大规模可编程逻辑器件FPGA器件的集成度高、工作速度快、编程方便、价格较低,易于实现设备的可编程设计,这些优势正好满足通信系统的这些要求。

随着器件复杂程度的提高,电路逻辑图变得过于复杂,不便于设计。

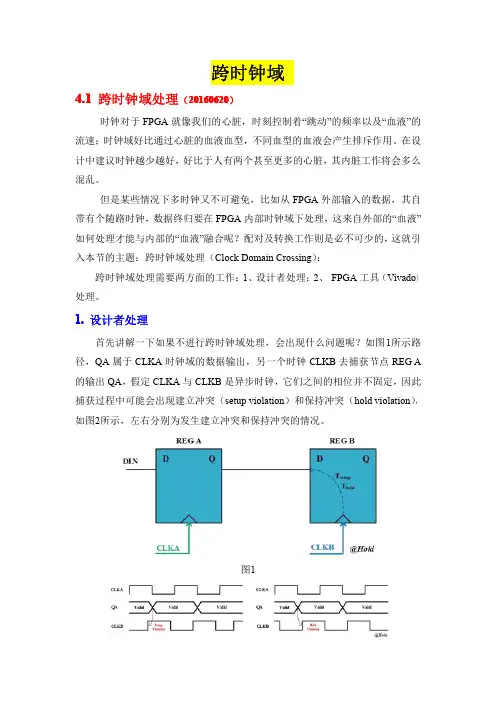

跨时钟域4.1跨时钟域处理(20160620)时钟对于FPGA就像我们的心脏,时刻控制着“跳动”的频率以及“血液”的流速;时钟域好比通过心脏的血液血型,不同血型的血液会产生排斥作用。

在设计中建议时钟越少越好,好比于人有两个甚至更多的心脏,其内脏工作将会多么混乱。

但是某些情况下多时钟又不可避免,比如从FPGA外部输入的数据,其自带有个随路时钟,数据终归要在FPGA内部时钟域下处理,这来自外部的“血液”如何处理才能与内部的“血液”融合呢?配对及转换工作则是必不可少的,这就引入本节的主题:跨时钟域处理(Clock Domain Crossing):跨时钟域处理需要两方面的工作:1、设计者处理;2、FPGA工具(Vivado)处理。

1.设计者处理首先讲解一下如果不进行跨时钟域处理,会出现什么问题呢?如图1所示路径,QA属于CLKA时钟域的数据输出,另一个时钟CLKB去捕获节点REG A 的输出QA,假定CLKA与CLKB是异步时钟,它们之间的相位并不固定,因此捕获过程中可能会出现建立冲突(setup violation)和保持冲突(hold violation),如图2所示,左右分别为发生建立冲突和保持冲突的情况。

图1图2当冲突出现时(我感觉整个人都不好了),会发生什么事情呢?在发生建立冲突或者保持冲突,捕获节点(REG B)会处于一个不定的状态,正常的状态是高电平或者低电平,而此时的状态停留在高电平和低电平的中间,无效的电平X,称这个状态为亚稳态。

如图3所示,捕获节点输出保持在亚稳态,可能在整个时钟周期内都保持在亚稳态,由于不正确的状态,其后连接的逻辑在功能实现上就会出现问题,比如一个判断信号上升沿的逻辑,通常判断D==HIGH&&D_PREV==LOW(D为信号当前电平状态,D_PREV为信号上个时钟的电平状态)是否成立,而发生亚稳态时则D_PREV==X,这个上升沿将会错过。

因此,加入跨时钟域处理设计是必须的。

FPGA位同步信号提取1. 引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过编程实现不同的电路功能。

在许多应用中,需要对FPGA进行位同步信号提取,以确保各个模块之间的数据传输和处理的准确性和一致性。

本文将详细介绍FPGA位同步信号提取的原理、方法和实现过程。

2. 原理在FPGA中,位同步信号提取是指从输入数据中提取一个用于同步各个模块的时钟信号。

这个时钟信号通常由一个稳定的时钟源产生,并被分配给FPGA内部的各个模块。

位同步信号提取有两个主要任务:检测输入数据中的时钟边沿,以及生成一个与输入数据频率相匹配的稳定时钟。

2.1 时钟边沿检测在FPGA中,通常使用触发器来检测输入数据中的时钟边沿。

触发器是一种存储元件,在时钟上升沿或下降沿触发时将输入数据存储到输出端口。

通过检测触发器输出端口的变化,可以确定输入数据中是否存在时钟边沿。

常见的触发器类型包括D触发器、JK触发器和T触发器。

这些触发器可以根据需要进行级联,以实现更复杂的时钟边沿检测功能。

在FPGA中,可以使用硬件描述语言(如Verilog或VHDL)来描述和实现这些触发器电路。

2.2 稳定时钟生成一旦检测到输入数据中的时钟边沿,需要生成一个稳定的时钟信号,并将其分配给FPGA内部的各个模块。

稳定的时钟信号通常由一个PLL(Phase-Locked Loop)电路来生成。

PLL是一种反馈控制系统,可以根据输入参考时钟的相位和频率来生成一个稳定的输出时钟。

PLL通常由相位比较器、环形振荡器和反馈回路组成。

相位比较器用于比较输入参考时钟和反馈时钟之间的相位差,并产生一个控制信号。

环形振荡器根据控制信号调整自身的振荡频率,使得反馈时钟与输入参考时钟保持同步。

通过不断调整振荡频率,PLL能够自动消除相位差,并生成稳定的输出时钟。

3. 方法在FPGA中实现位同步信号提取有多种方法,下面将介绍两种常用的方法:基于触发器的位同步信号提取和基于PLL的位同步信号提取。

verilog判断上升沿的方法在 Verilog 中判断上升沿的方法有多种。

以下是其中两种常用方法的介绍:方法一:使用边沿检测器要判断信号的上升沿,可以使用边沿检测器模块。

边沿检测器将输入信号与其之前的状态进行比较,当输入信号从低电平变为高电平时,输出产生一个上升沿脉冲。

以下是一个示例代码片段:```module EdgeDetector (input wire clk,input wire sig,output wire posedge);reg sig_prev = 0;always @(posedge clk) beginsig_prev <= sig;posedge <= (sig && !sig_prev);endendmodule```在上述示例中,输入信号 `sig` 和时钟信号 `clk` 都采用 `wire` 类型声明。

`sig_prev` 为上一个时刻的信号值,使用 `reg` 类型存储,并在时钟上升沿触发时进行更新。

`posedge` 为输出信号,当边沿检测到输入信号 `sig` 由低电平变为高电平时,输出一个脉冲。

方法二:使用组合逻辑Verilog 中也可以使用组合逻辑来判断上升沿。

以下是一个使用组合逻辑实现的示例代码片段:```module RisingEdgeDetector (input wire clk,input wire sig,output wire posedge);wire sig_prev = ~sig;assign posedge = (sig && sig_prev);endmodule```在上述示例中,`sig_prev` 通过对输入信号 `sig` 取反得到,用于表示上一个时刻的信号状态。

`posedge` 是一个输出信号,使用 `assign` 语句通过逻辑运算判断输入信号 `sig` 是否为高电平,并且上一个时刻的信号 `sig_prev` 为低电平。

基于FPGA的脉冲信号参数测量系统设计基于FPGA的脉冲信号参数测量系统设计是一种利用FPGA(Field Programmable Gate Array)芯片来实现脉冲信号参数测量的系统。

脉冲信号参数包括脉冲宽度、频率、占空比等,这些参数广泛应用于通信、雷达、无线电和其他各种应用领域中。

该系统的设计包括以下几个方面:一、信号采集和预处理系统需要首先采集脉冲信号,并进行预处理。

采集可以通过连接外部传感器或电路来实现,传感器/电路将信号转换成电压或电流,并通过模拟到数字转换器(ADC)将采样的信号转化成数字信号。

预处理阶段可以包括滤波去噪、放大/衰减等。

二、数字信号处理经过信号采集和预处理后,系统需要对数字信号进行处理,提取脉冲信号的参数。

这可以通过在FPGA上实现一些数字信号处理(DSP)算法来完成。

常见的DSP算法包括傅里叶变换、滤波、边沿检测等。

通过这些算法,系统可以实时地分析脉冲信号,提取出脉冲宽度、频率、占空比等参数。

三、参数显示和输出提取出的脉冲信号参数需要以可视化的方式显示出来,便于用户观察和分析。

可以通过连接显示器或其他输出设备来实现参数的显示。

此外,系统还可以通过串口、以太网等方式输出参数,以便于进一步的数据分析和处理。

四、参数控制和配置系统还可以提供参数控制和配置的功能。

用户可以通过操作面板或其他方式输入参数配置,例如采样率、滤波器类型、显示方式等。

系统可以根据用户配置的参数来调整相应的处理算法和显示方式。

基于FPGA的脉冲信号参数测量系统的设计,可以利用FPGA芯片的高度可编程性和并行计算能力来实现实时处理和高精度的脉冲信号参数测量。

该系统还可以具有较高的灵活性和可扩展性,可以根据不同应用的需求对参数进行定制和调整。

总之,基于FPGA的脉冲信号参数测量系统设计是一种利用FPGA芯片来实现脉冲信号参数测量的系统,通过信号采集和预处理、数字信号处理、参数显示和输出以及参数控制和配置等模块的设计和实现,能够提供高性能和高精度的脉冲信号参数测量功能。

基于DE2-115开发板的FPGA入门设计实验1、Lab1: 4位加法器、减法器的设计1.1 摘要在文件add_sub里面的工程文件operation_4.v为顶层文件,该顶层文件包含了三个子模块,分别为数码管显示模块,4位带进位的二进制加法器模块和4位带借位的二进制减法器模块,最后通过DE2-115开发板显示实验结果。

1.2 程序1)add_4bits.v 加法器module adder_4bits(input clk,input rst_n,input [3:0] x,input [3:0] y,output reg [3:0] sum,output reg carry_out //溢出位);always@(posedge clk or negedge rst_n)beginif(!rst_n){carry_out, sum} <= 0;else{carry_out, sum} = x + y;endendmodule2)substractor_4bits.v减法器module subtractor_4bits(input clk,input rst_n,input [3:0] x,input [3:0] y,output r eg [3:0] sub,output r eg borrow_out);always@(posedge clk or negedge rst_n) beginif(!rst_n){borrow_out, sub} <= 0;elsebeginif(x >= y){borrow_out, sub} = {1'b0, x - y};else{borrow_out, sub} = {1'b1, x - y};endendendmodule3)seg7_lut.v 数码管显示译码模块module Seg7_lut(input [3:0] iDIG,output r eg [6:0] oSEG);always @(iDIG)begincase(iDIG)4'h1: oSEG = 7'b1111001; // ---t----4'h2: oSEG = 7'b0100100; // | |4'h3: oSEG = 7'b0110000; // lt rt4'h4: oSEG = 7'b0011001; // | |4'h5: oSEG = 7'b0010010; // ---m----4'h6: oSEG = 7'b0000010; // | |4'h7: oSEG = 7'b1111000; // lb rb4'h8: oSEG = 7'b0000000; // | |4'h9: oSEG = 7'b0011000; // ---b----4'ha: oSEG = 7'b0001000;4'hb: oSEG = 7'b0000011;4'hc: oSEG = 7'b1000110;4'hd: oSEG = 7'b0100001;4'he: oSEG = 7'b0000110;4'hf: oSEG = 7'b0001110;4'h0: oSEG = 7'b1000000;endcaseendendmodule1.3 结果本设计通过Verilog HDL硬件描述语言。

基于FPGA和单片机的多功能等精度频率计设计摘要基于传统测频原理的频率计的测量精度将随着被测信号频率的下降而降低,在实用中有很大的局限性,而等精度频率计不但有较高的测量精度,而且在整个测频区域内保持恒定的测试精度。

运用等精度测量原理,结合单片机技术设计了一种数字频率计,由于采用了屏蔽驱动电路及数字均值滤波等技术措施,因而能在较宽定的频率范围和幅度范围内对频率,周期,脉宽,占空比等参数进行测量,并可通过调整闸门时间预置测量精度。

选取的这种综合测量法作为数字频率计的测量算法,提出了基于FPGA 的数字频率计的设计方案。

给出了该设计方案的实际测量效果,证明该设计方案切实可行,能达到较高的频率测量精度。

关键词等精度测量,单片机,频率计,闸门时间,FPGAABSTRACTAlong with is measured based on the traditional frequency measurement principle frequency meter measuring accuracy the signalling frequency the drop but to reduce, in is practical has the very big limitation, but and so on the precision frequency meter not only has teaches the high measuring accuracy, moreover maintains the constant test precision in the entire frequency measurement region. Using and so on the precision survey principle, unified the monolithic integrated circuit technical design one kind of numeral frequency meter, because has used the shield actuation electric circuit and technical measure and so on digital average value filter, thus could in compared in the frequency range and the scope scope which the width decided to the frequency, the cycle, the pulse width, occupied parameter and so on spatial ratio carries on the survey, and might through the adjustment strobe time initialization measuring accuracy. Selection this kind of synthesis measured the mensuration took the digital frequency meter the survey algorithm, proposed based on the FPGA digital frequency meter design proposal. Has produced this design proposal actual survey effect, proved this design proposal is practical and feasible, can achieve the high frequency measurement precisionKeywords Precision survey, microcontroller, frequency meter, strobe time,field programmable gate array1 绪论测量频率是电子测量技术中最常见的测量之一。

基于FPGA的脉冲信号发生器设计章欣【摘要】基于FPGA并运用DDS技术的相关理论,通过模块化设计,使标准脉冲信号发生器达到较高的性能指标,能够产生1~100 kHz 线性可调的脉冲,脉冲分辨率达100 Hz,上升沿及下降沿为2.5 ns,脉冲宽度从200 ns~5μs可调,脉宽分辨率50 ns,满足集成电路的脉冲驱动要求。

%Based on FPG and the theory of DDS technology,according to the design of each module,the standard pulse signal generator achieves the high performance index.It can produce 1 k-100 kHz linear adjustable pulse,100Hz the pulse resolution,2.5ns rising and falling edge,pulse width adjustable from 200ns-5μs and 50ns pulse width resolution,which meets the requirement of pulse drive in the integrated circuits.【期刊名称】《气象水文海洋仪器》【年(卷),期】2014(000)002【总页数】5页(P69-73)【关键词】FPGA;脉冲信号发生器;DDS【作者】章欣【作者单位】南京信息工程大学,气象灾害预报预警与评估协同创新中心,南京210044【正文语种】中文【中图分类】TP317.40 引言在集成电路应用中经常需要使用脉冲源来驱动集成芯片,在雷达、计算机硬件系统和通信系统等领域的设计和调试中,同样需要大量的精度高、速度快的脉冲信号和数字序列作为激励。

在其他领域例如:激光器供电、电火花加工、静电除尘、脉冲电镀等方面,脉冲源也得到了广泛的应用,因而脉冲信号发生器的设计和研制具有很大的价值。