第六章 时序逻辑电路

- 格式:ppt

- 大小:5.25 MB

- 文档页数:56

6 时序逻辑电路6.1.1 已知一时序电路的状态表如表题6.1.1所示,A为输入信号,试作出相应的状态图。

解:由状态图的概念及已知的状态表,可画出对应的状态图,如图题解6.1.1所示。

6.1.2已知状态表如表题6.1.2所示,输入为X1X0,试作出相应的状态图。

解:根据表题6.1.2所示的状态表,作出对应的状态图如图题解6.1.2所示。

6.1.3已知状态图如图题6.1.3所示,试列出它的状态表。

解:按图题6.1.3列出的状态表如表题解6.1.3所示。

6.1.5 图题6.1.5所示是某时序电路的状态图,设电路的初始状态为01,当序列A=100110(自左至右输入)时,求该电路输出Z的序列。

解:由图题6.1.5所示的状态图可知,当初态为01,输入信号的序列A=100110时,该时序电路将按图题解6.1.5所示的顺序改变状态,因而对应的输出序列为Z=011010。

6.1.6已知某时序电路的状态表如表题6.1.6所示,输入A,试画出它的状态图。

如果电路的初始状态在b,输入信号A一次是0、1、0、1、1、1、1,试求出其相应的输出。

解:根据表题6.1.6所示的状态表,可直接画出与其对应的状态图,如图题解6.1.6(a)当从初态b开始,依次输入0、1、0、1、1、1、1信号时,该时序电路将按图题解6.1.6(b)所示的顺序改变状态,因而其对应的输出为1、0、1、0、1、0、1。

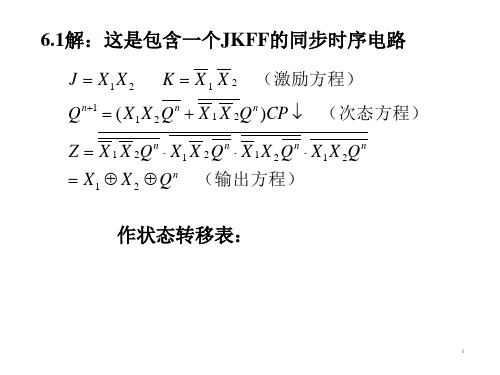

6.2 同步时序逻辑电路的分析6.2.1 试分析图题6.2.1(a)所示时序电路,画出其状态表和状态图。

设电路的初始状态为0,试画出6.2.1(b)所示波形作用下,Q和Z的波形图。

解:由所给电路图可写出该电路的状态方程和输出方程,分别为1n nQ A QZAQ+=⊕=其状态表如表题解6.2.1所示,状态图如图题解6.2.1(a)所示,Q和Z的波形图如图题解6.2.1(b)所示。

6.2.2 试分析图题6.2.2(a)所示时序电路,画出其状态表和状态图。

数字电子技术(第5版)第6章时序逻辑电路1.(334)利用()可以把集成计数器设计成初态不为零的计数器。

答案.反馈置数法2.(318)时序逻辑电路由( ) 和( ) 两部分组成。

答案.组合电路存储电路3.(337)一个4位的扭环形计数器有()个状态。

答案. 84.(335)集成计数器的级联方式有()和()两种方式。

答案.异步同步5.(333)利用()和()可以改变集成计数器的计数长度。

答案.反馈归零法反馈置数法6.(332)一个模为24的计数器,能够记录到的最大计数值是()。

答案. 237.(331)计数器的模表示计数器的()计数长度。

答案.最大8.(329)构成时序电路的各触发器的时钟输入端都接在一起,这种时序电路称为()。

答案.同步时序电路9.(328)时序电路的输出不仅与电路的()有关,还与电路的()有关。

答案.现态输入信号10.(327)摩尔型时序电路的输出仅由电路的()决定,而与电路的( ) 无关。

(注:教材中没有讲述摩尔型电路的概念,故删去此题)答案.现态输入信号11.(326) 时序逻辑电路的功能描述有 ( ) 、 ( ) 、 ( ) 、 ( ) 。

答案. 逻辑方程式 状态表 状态图 时序图12.(330) 异步时序电路中的各触发器的状态转换 ( )同一时刻进行的。

答案. 不是在13.(336) 一个4位的环形计数器有( )个状态。

答案. 414.(325) 时序逻辑电路可分为 ( ) 和 ( ) 两大类。

答案. 同步时序电路 异步时序电路15.(354) 分析如图7307所示电路,说明其功能。

图7307输 入输 出CR LD T CT P CT CP 3D 2D 1D 0D 3Q 2Q 1Q 0QCO0 × × × × × × × × 000 10××↑3d 2d 1d 0d 3d 2d 1d 0d1111↑×××× 计数 110×××××× 保持 11××××××保持答案. 经分析知,采用了74LS160的同步置数功能。

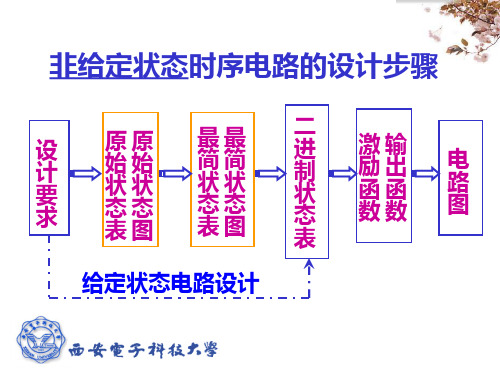

数字电路第6章(1时序逻辑电路分析方法)1、第六章时序规律电路本章主要内容6.1概述6.2时序规律电路的分析方法6.3若干常用的时序规律电路6.4时序规律电路的设计方法6.5时序规律电路中的竞争-冒险现象1.时序规律电路的特点2.时序规律电路的分类3.时序规律电路的功能描述方法§6.1概述一、时序规律电路的特点1、功能:任一时刻的输出不仅取决于该时刻的输入;还与电路原来的状态有关。

例:串行加法器:两个多位数从低位到高位逐位相加一、时序规律电路的特点2.电路结构①包含存储电路和组合电路,且存储电路必不行少;②存储电路的输出状态必需反馈到组合电路输入端,与输入变量共同确定组合规律的输出。

yi:输出信号xi:输2、入信号qi:存储电路的状态zi:存储电路的输入可以用三个方程组来描述:Z=G(X,Q)二、时序电路的分类1.依据存储电路中触发器的动作特点不同时序电路存储电路里全部触发器有一个统一的时钟源;触发器状态改变与时钟脉冲同步.同步:异步:没有统一的时钟脉冲,电路中要更新状态的触发器的翻转有先有后,是异步进行的。

二、时序电路的分类2.依据输出信号的特点不同时序电路输出信号不仅取决于存储电路的状态,而且还取决于输入变量。

Y=F(X,Q)米利(Mealy)型:穆尔(Moore)型:输出状态仅取决于存储电路的状态。

犹如步计数器Y=F(Q)三、时序规律电路的功能描述方法描述方法3、规律方程式状态转换表状态转换图时序图三、时序规律电路的功能描述方法(1)规律方程式:写出时序电路的输出方程、驱动方程和状态方程。

输出方程反映电路输出Y与输入X和状态Q之间关系表达式;驱动方程反映存储电路的输入Z与电路输入X和状态Q之间的关系状态方程反映时序电路次态Qn+1与驱动函数Z和现态Qn之间的关系三、时序规律电路的功能描述方法(2)状态〔转换〕表:反映输出Z、次态Qn+1和输入X、现态Qn间对应取值关系的表格。

(3)状态〔转换〕图:(4)时序图:反映时序规律电路状态转换规律及相应输入、输出取值关系的有向图形。

第六章时序逻辑电路(选择、判断共30题)一、选择题1.同步计数器和异步计数器比较,同步计数器的显著优点是。

A.工作速度高B.触发器利用率高C.电路简单D.不受时钟C P控制。

2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。

A.4B.5C.9D.203.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器B.加法器C.数码寄存器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为的计数器。

A.NB.2NC.N2D.2N5.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N6.五个D触发器构成环形计数器,其计数长度为。

A.5B.10C.25D.327.同步时序电路和异步时序电路比较,其差异在于后者。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关8.一位8421B C D码计数器至少需要个触发器。

A.3B.4C.5D.109.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用级触发器。

A.2B.3C.4D.810.8位移位寄存器,串行输入时经个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.811.用二进制异步计数器从0做加法,计到十进制数178,则最少需要个触发器。

A.2B.6C.7D.8E.1012.某电视机水平-垂直扫描发生器需要一个分频器将31500H Z的脉冲转换为60H Z的脉冲,欲构成此分频器至少需要个触发器。

A.10B.60C.525D.3150013.某移位寄存器的时钟脉冲频率为100K H Z ,欲将存放在该寄存器中的数左移8位,完成该操作需要时间。

A.10μSB.80μSC.100μSD.800m s 14.若用J K 触发器来实现特性方程为,则J K 端的方程为 。

AB Q A Q n 1n +=+A.J =A B ,K = B.J =A B ,K = C.J =,K =A B D.J =,K =A B B A +B A B A +B A 15.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需要 片。