组合逻辑电路中的竞争冒险备课讲稿

- 格式:doc

- 大小:172.00 KB

- 文档页数:13

数字电路与系统东南大学信息科学与工程学院第三章组合逻辑电路的分析和设计组合逻辑电路的特点组合逻辑电路的分析方法组合逻辑电路的最小化设计方法组合逻辑电路的竞争与冒险◆通常,对于组合逻辑电路的分析与设计,都是在理想的情况下进行的,也就是假设电路中没有延时;◆而实际上,信号从电路的输入端输入,到电路的输出端输出,都需要一定的时间;◆信号经过电路中的连线、逻辑门,会产生延迟,也就是信号经过导线、逻辑门的传输,需要一定的响应时间,信号的变化也就会存在一定的过渡时间;◆信号经过不同的路径到达输出端,延迟也就会不一样;◆多个信号变化时,会存在有先后快慢的区别;◆考虑到这些实际情况,在前面对逻辑电路的分析和设计,就有可能出现信号变化的瞬间,电路的输出与我们分析或者设计的结果不一致;◆这种电路的输出与我们的预期,或者说理论上的分析与设计不一致的现象,就是竞争与险象;◆竞争的概念:在组合逻辑电路中,输入信号的变化传输到电路的各级逻辑门,到达的时间有先后,也就是存在时差,称为竞争;◆险象的概念:当输入信号变化时,输出端产生错误,出现了瞬时的干扰脉冲现象;◆竞争不一定会产生冒险,因为当输入信号传输到各级逻辑门,存在竞争,但是在输出端没有出现瞬时的干扰脉冲,就不会产生冒险;◆冒险,一定存在竞争,冒险是竞争的结果;◆严格的意义上讲,冒险的产生,是因为电路存在延迟;◆如果电路仅仅存在竞争,而没有产生险象,对电路的输出或者对后续电路都没有影响,就没有必要进行处理;◆如果电路存在竞争,也产生了险象,但是,这种险象是瞬间的;如果险象对于电路的输出不产生影响,或者后续电路对这种现象不敏感,险象也可以不进行处理;◆但是,如果后续电路对这种瞬时出现的干扰脉冲敏感,就会导致电路功能产生错误;◆在这种情况下,就需要采取措施消除冒险现象;例:如图所示与门,输出F=AB;当AB取值01或者10时,输出F为0;但是,当AB由01变为10时,由于两个信号变化不可能同时完成:如果A先于B变化,就会产生干扰脉冲,也就是会出现冒险现象;如果A滞后于B变化,不会产生冒险;组合逻辑电路,如果输入信号变化前后,稳定的输出值相同,而仅仅在转换瞬间有冒险,称为静态冒险。

数电实验五组合电路中的竞争与冒险预习报告1、复习与组合逻辑电路竞争与冒险有关内容(1)竞争冒险现象及其成因对于组合逻辑电路,输出仅取决于输入信号的取值组合,但这仅是指电路的稳定解而言,没有涉及电路的暂态过程。

实际上,在组合逻辑电路中信号的传输可能通过不同的路径而汇合到某一门的输入端上。

由于门电路的传输延迟,各路信号对于汇合点会有一定的时差,这种现象称为竞争。

如果竞争现象的存在不会使电路产生错误的输出,则称为非临界竞争;如果使电路的输出产生了错误,则称为临界竞争,通常称为逻辑冒险现象。

一般说来,在组合逻辑电路中,如果有两个或两个以上的信号参差地加到同一门的输入端,在门的输出端得到稳定的输出之前,可能出现短暂的、不是原设计要求的错误输出,其形状是一个宽度仅为时差的窄脉冲,通常称为尖峰脉冲或毛刺。

(2)检查竞争冒险现象的方法在输入变量每次只有一个改变状态的简单情况下,可以通过逻辑函数式判断组合逻辑电路中是否有竞争冒险存在。

__如果输出端门电路的两个输入信号A和A 是输入变量A经过两个不同的传输途径而来的,那么当输入变量的状态发生突变时输出端便有可能产生尖峰脉冲。

因此,只要输出端的逻辑函数在一定条件下化简成_ _Y = A + A 或 Y = A A则可判断存在竞争冒险。

(3)消除竞争冒险现象的方法①接入滤波电路在输出端并接入一个很小的滤波电容Cf,足可把尖峰脉冲的幅度削弱至门电路的阈值电压以下。

②引入选通脉冲对输出引进选通脉冲,避开现象。

③修改逻辑设计在逻辑函数化简选择乘积项时,按照判断组合电路是否存在竞争冒险的方法,选择使逻辑函数不会使逻辑函数产生竞争冒险的乘积项。

也可采用增加冗余项方法。

选择消除险象的方法应根据具体情况而定。

组合逻辑电路的险象是一个重要的实际问题。

当设计出一个组合电路,安装后应首先进行静态测试,也就是用逻辑开关按真值表依次改变输入量,验证其逻辑功能。

然后再进行动态测试,观察是否存在冒险。

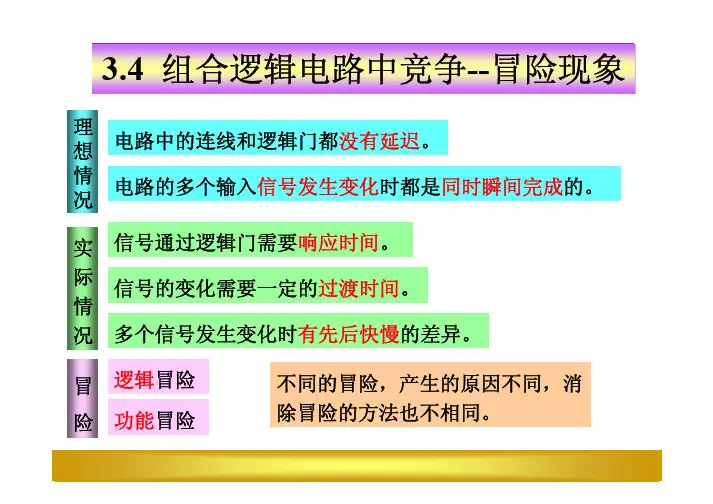

3.4组合逻辑电路中竞争--冒险现象理想情况电路中的连线和逻辑门都没有延迟。

电路的多个输入信号发生变化时都是同时瞬间完成的。

实际情况信号通过逻辑门需要响应时间。

信号的变化需要一定的过渡时间。

多个信号发生变化时有先后快慢的差异。

冒险逻辑冒险功能冒险不同的冒险,产生的原因不同,消除冒险的方法也不相同。

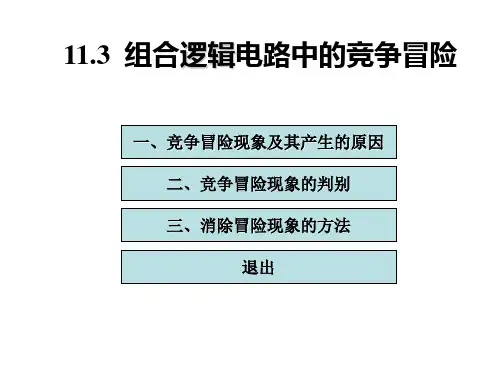

3.4.1 竞争 冒险现象及其成因两个输入信号(一个从1将出现毛刺竞争不一定都会产生尖峰脉冲不产生毛刺t pd2<t pd1+t 出现毛刺检查逻辑冒险的方法稳态时输出1,输入变化瞬间输出0的冒险,称为偏1型冒险。

稳态时输出0,输入变化瞬间输出1的冒险,称为偏0型冒险。

方法代数法卡诺图法方法比较繁琐,适用范围广,对两级(含)以上电路都适用。

注意:不能对函数进行化简。

方法简单,只适用于两级电路。

计算机模拟检查法实验检查法功能冒险输入从Ii 变到Ij时产生功能冒险的条件:2、有P个(P≥2)变量同时发生变化;1、输入变量变化前后函数值相同。

即F( I i)=F( I j);3 、由P个变量组合所构成的2P个格,既有1又有0。

例3-14:判断下面卡诺图所示逻辑函数,当输入ABCD从0110→1100,1111→1010,0011→0100,1000→1101变化时,是否存在功能冒险。

功能冒险的消除方法选通脉冲加入的位置和极性的确定:与非门实现函数F=AB+CD正极性脉冲加在第二级功能冒险的消除方法或非门实现函数F=(A+B)(C+D)负极性脉冲加在第一级功能冒险的消除方法负极性脉冲加在一个与门上功能冒险的消除方法方法二:在对输出波形边沿要求不高的情况下,可以在输,滤除毛刺。

出端接一个几十到几百皮法的滤波电容CL在输出端加小电容可以消除毛刺。

但是输出波形的前后沿将变坏,只适用于低速电路,在对波形要求较严格时,应再加整形电路。

3.4.2 消除竞争 冒险的方法加冗余项:只能消除逻辑冒险,而不能消除功能冒险,适用范围有限。

探索组合逻辑电路的竞争冒险现象及消除方法

组合逻辑电路是指一些由多个逻辑门组成的逻辑电路。

它们一般不具有记忆性,不涉及时钟信号,是根据输入信号直接输出结果的电路。

虽然组合逻辑电路看起来非常简单,但是在实际应用中存在着一些竞争冒险,这可能导致电路输出错误的结果。

本文将探讨组合逻辑电路的竞争冒险现象及消除方法。

竞争冒险是指当多个逻辑门的输入信号在不同的时间到达时,电路不能准确地确定输出信号。

这是由于电路中存在着多条不同的信号路径,当这些路径的信号到达的时间不同,就会发生竞争冒险。

这个现象如果不及时解决,就会导致电路输出错误的结果,甚至会使整个系统崩溃。

竞争冒险可以通过添加延迟元件来解决。

这些延迟元件包括反相器和缓冲器。

反相器可以改变输入信号的极性,并将输出信号延迟一定时间后输出。

缓冲器可以加强信号的强度,并将信号的延迟控制在很小的范围内。

通过添加这些延迟元件,可以精确地控制信号的延迟时间,从而避免竞争冒险。

另外,竞争冒险问题也可以通过优化电路结构来解决。

由于冒险问题是由信号路径的不同导致的,我们可以尽可能地减少信号路径的长度和数量。

在优化电路时,需要考虑到电路的性能和延迟时间之间的平衡。

如果性能过于复杂,就会增加信号延迟时间,从而导致冒险问题。

如果性能过于简单,就会降低电路的效率和稳定性。

总之,竞争冒险是组合逻辑电路中常见的问题之一。

通过添加

延迟元件和优化电路结构,可以有效地解决这个问题。

在实际应用中,我们必须注意电路的稳定性和效率,以便顺利地解决竞争冒险问题,保证电路的正确性。

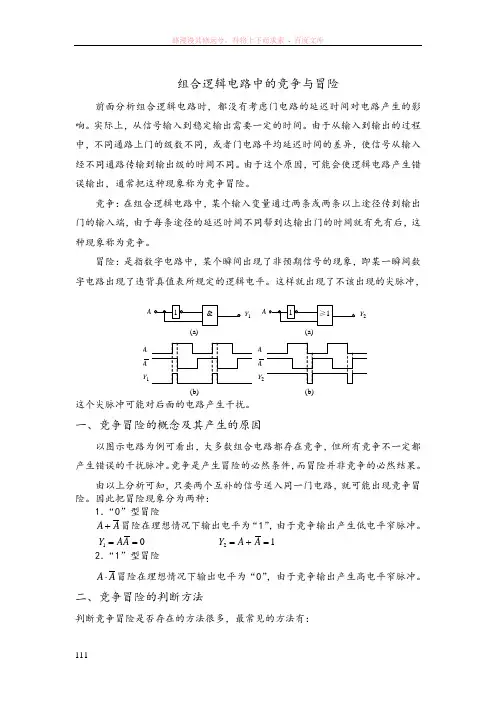

组合逻辑电路中的竞争冒险

前面分析组合逻辑电路时,都没有考虑门电路的延迟时间对电路产生的影响。

实际上,从信号输入到稳定输出需要一定的时间。

由于从输入到输出的过程中,不同通路上门的级数不同,或者门电路平均延迟时间的差异,使信号从输人经不同通路传输到输出级的时间不同。

由于这个原因,可能会使逻辑电路产生错误输出。

通常把这种现象称为竞争冒险。

一、产生竞争冒险的原因

首先来分析下图所示电路的工作情况,可以建立竞争冒险的概念。

在图中,与门G2的输入是A和两个互补信号。

由于G1的延迟,的下降沿要滞后于A的上升沿,因此在很短的时间间隔内,G2的两个输入端都会出现高电平,致使它的输出出现一个高电平窄脉冲(它是按逻辑设计要求不应出现的干扰脉冲),见图中的波形部分所示。

与门G2的2个输入信号分别由G1和A端两个路径在不同的时刻到达的现象,通常称为竞争,由此而产生输出干扰脉冲的现象称为冒险。

下面进一步分析组合逻辑电路产生竞争冒险的原因。

设有一个逻辑电路如上图所示,其工作波形如下图所示。

它的输出逻辑表达式为。

由此式可知,当A和B都为1时,L=1,与C的状态无关。

但是,由波形图可以看出,在C由1变0时,C由0变1有一延迟时间,在这个时间间隔内,G2和G3的输出AC和同时为0,而使输出出现一负跳变的窄脉冲,即冒险现象。

这是产生竞争冒险的原因之一,其他原因这里不作详述。

由以上分析可知,当电路中存在由反相器产生的互补信号,且在互补信。

3.4组合逻辑电路中竞争--冒险现象理想情况电路中的连线和逻辑门都没有延迟。

电路的多个输入信号发生变化时都是同时瞬间完成的。

实际情况信号通过逻辑门需要响应时间。

信号的变化需要一定的过渡时间。

多个信号发生变化时有先后快慢的差异。

冒险逻辑冒险功能冒险不同的冒险,产生的原因不同,消除冒险的方法也不相同。

3.4.1 竞争 冒险现象及其成因两个输入信号(一个从1将出现毛刺竞争不一定都会产生尖峰脉冲不产生毛刺t pd2<t pd1+t 出现毛刺检查逻辑冒险的方法稳态时输出1,输入变化瞬间输出0的冒险,称为偏1型冒险。

稳态时输出0,输入变化瞬间输出1的冒险,称为偏0型冒险。

方法代数法卡诺图法方法比较繁琐,适用范围广,对两级(含)以上电路都适用。

注意:不能对函数进行化简。

方法简单,只适用于两级电路。

计算机模拟检查法实验检查法功能冒险输入从Ii 变到Ij时产生功能冒险的条件:2、有P个(P≥2)变量同时发生变化;1、输入变量变化前后函数值相同。

即F( I i)=F( I j);3 、由P个变量组合所构成的2P个格,既有1又有0。

例3-14:判断下面卡诺图所示逻辑函数,当输入ABCD从0110→1100,1111→1010,0011→0100,1000→1101变化时,是否存在功能冒险。

功能冒险的消除方法选通脉冲加入的位置和极性的确定:与非门实现函数F=AB+CD正极性脉冲加在第二级功能冒险的消除方法或非门实现函数F=(A+B)(C+D)负极性脉冲加在第一级功能冒险的消除方法负极性脉冲加在一个与门上功能冒险的消除方法方法二:在对输出波形边沿要求不高的情况下,可以在输,滤除毛刺。

出端接一个几十到几百皮法的滤波电容CL在输出端加小电容可以消除毛刺。

但是输出波形的前后沿将变坏,只适用于低速电路,在对波形要求较严格时,应再加整形电路。

3.4.2 消除竞争 冒险的方法加冗余项:只能消除逻辑冒险,而不能消除功能冒险,适用范围有限。

组合逻辑电路中的竞争与冒险前面分析组合逻辑电路时,都没有考虑门电路的延迟时间对电路产生的影响。

实际上,从信号输入到稳定输出需要一定的时间。

由于从输入到输出的过程中,不同通路上门的级数不同,或者门电路平均延迟时间的差异,使信号从输入经不同通路传输到输出级的时间不同。

由于这个原因,可能会使逻辑电路产生错误输出,通常把这种现象称为竞争冒险。

竞争:在组合逻辑电路中,某个输入变量通过两条或两条以上途径传到输出门的输入端,由于每条途径的延迟时间不同帮到达输出门的时间就有先有后,这种现象称为竞争。

冒险:是指数字电路中,某个瞬间出现了非预期信号的现象,即某一瞬间数字电路出现了违背真值表所规定的逻辑电平。

这样就出现了不该出现的尖脉冲,一、 竞争冒险的概念及其产生的原因以图示电路为例可看出,大多数组合电路都存在竞争,但所有竞争不一定都产生错误的干扰脉冲。

竞争是产生冒险的必然条件,而冒险并非竞争的必然结果。

由以上分析可知,只要两个互补的信号送入同一门电路,就可能出现竞争冒险。

因此把冒险现象分为两种:1.“0”型冒险A A +冒险在理想情况下输出电平为“1”,由于竞争输出产生低电平窄脉冲。

A A ⋅冒险在理想情况下输出电平为“0”,由于竞争输出产生高电平窄脉冲。

二、 竞争冒险的判断方法判断竞争冒险是否存在的方法很多,最常见的方法有:AA1&Y 1A A Y 1(a)(b)1≥1Y 2A A Y 2(a)(b)01==A A Y 12=+=A A Y1.代数法在逻辑函数表达式中,是否存在某变量的原变量和反变量。

若去掉其他变量得到A A Y +=,电路有可能产生“0”冒险;若得到A A Y ⋅=,则可能产生“1”冒险。

2.卡诺图法画出逻辑函数的卡诺图,当卡诺图中两个合并最小项圈相切,即两个合并最小项圈相邻—有相邻项,各合并最小项圈各自独立—不相交时,这个逻辑函数有可能出现冒险现象。

三、 消除竞争冒险的方法1.修改逻辑设计 (1)代数法①逻辑变换消去互补量))((C A B A Y ++=当B =C=0时,A A Y ⋅=,存在竞争冒险。

组合逻辑电路中的竞争冒险一、定义1、竞争:组合电路中,若某个变量通过两条以上途径到达输入端,由于每条路径上的延迟时间不同,到达逻辑门的时间就有先有后的现象。

2、冒险:因竞争使真值表描述的逻辑关系受到短暂的破坏,在输出端产生错误结果的现象。

(毛刺) 有竞争存在时不一定产生冒险。

二、冒险的类型“1”型冒险:使输出出现高电平窄脉冲的冒险;(恒为0时不为0,A A∙)“0”型冒险:使输出出现低电平窄脉冲的冒险。

(恒为1时不为1,A A+)三、0型冒险和1型冒险的判断在一个逻辑函数式Y中,如果某个变量以原变量和反变量的形式在式中出现,那么该变量就是具有竞争条件的变量。

1.如果令其它变量为0或1消去后式子中出现类似下式形式:=则电路中就会产生0型冒险。

AY+A2.如果令其它变量为0或1消去后式子中出现类似下式形式:四、判断方法:(1)找出以原、反变量同时出现的变量;(2)以其它变量为自变量列真值表求Y 的表达式;(3)Y 中有A A ∙则存在“1”型冒险;有A A +则存在“0”型冒险五、消除办法:(1)修改逻辑设计;(2)增加选通脉冲;(3)使用滤波电容。

例24 判断C A B A AC Y ++=是否存在冒险。

解:(1)判断条件:函数式中以原、反变量形式出现同时出现的A 是C 和,先判断A 见表。

A 变量判断表(2)判断结果:从表中可以看出当1==C B 时有A A Y +=则电路中A 信号在“0型冒险”。

同理判断变量C ,会发现变量C 不存在冒险。

1型冒险的判断方法同上面一样。

四、修改逻辑设计以消除竞争冒险利用逻辑代数中的公式对存在冒险的逻辑函数式进行变换,增加多余项,来消除冒险。

例如AC=,Y+AB在1==CB时有0型冒险。

如果利用公式将Y变换为:+Y+=A=,则当1=+ACBCBBAACB时结果变为1=Y,从=C而消除了冒险。

组合逻辑电路中的竞争冒险 精品资料

仅供学习与交流,如有侵权请联系网站删除 谢谢1 精品资料

仅供学习与交流,如有侵权请联系网站删除 谢谢1 目 录 摘要 1 关键词 ........................................................................................................................................ 1 Abstract ....................................................................................................................................... 1 Key words ................................................................................................................................... 1 1 引言 ......................................................................................................................................... 1 2 竞争冒险现象及产生的原因 ................................................................................................. 1 2.1竞争冒险现象 ..................................................................................................................... 1 2.2竞争冒险现象产生的原因 ................................................................................................. 2 2.3竞争冒险的危害 ................................................................................................................. 2 2.4竞争冒险的分类 ................................................................................................................. 2 2.4.1静态冒险 ........................................................................................................................... 2 2.4.2动态冒险 ........................................................................................................................... 2 3竞争冒险的判断 ..................................................................................................................... 2 3.1代数法 ................................................................................................................................. 2 3.2卡诺图法 ............................................................................................................................. 3 3.3仿真法和实验法 ................................................................................................................. 4 3.4通过实验判断竞争冒险现象 ............................................................................................. 4 3.4.1实验分析 ........................................................................................................................... 6 3.4.2实验总结 ........................................................................................................................... 7 4竞争冒险的消除方法 ............................................................................................................. 7 4.1增加冗余项法 ..................................................................................................................... 7 4.2消除互补项法 ..................................................................................................................... 7 4.3接入滤波电容 ..................................................................................................................... 7 4.4引入选通脉冲 ..................................................................................................................... 8 4.5引入封锁脉冲 ..................................................................................................................... 8 4.6采用可靠性编码 ................................................................................................................. 8 4.7输出加D触发器 ................................................................................................................. 8 5实际应用中竞争冒险的敏感度问题 ..................................................................................... 8 6总结 ......................................................................................................................................... 8 致谢 10 参考文献 .................................................................................................................................. 10 精品资料

仅供学习与交流,如有侵权请联系网站删除 谢谢1 组合逻辑电路中的竞争冒险 网络工程专业学生 郭翔 指导教师 吴俊华

摘要:在组合逻辑电路中,当输入信号改变状态时,输出端可能出现由于竞争冒险而产生的干扰脉冲信号,如果负载是对干扰脉冲信号十分敏感的电路,有可能引起电路的误动作,因此应该采取措施消除竞争冒险。从理论上分析了组合逻辑电路竞争冒险的产生,及其判断和消除的方法,其产生原因包括:门电路开关电平的时间差和门电路延迟时间。竞争冒险可以通过代数法、卡诺图法、仿真法和实验法进行判断,采用引入选通脉冲、引入封锁脉冲、增加冗余项、接入滤波电容等手段以消除竞争冒险。 关键词:组合逻辑电路 竞争冒险 干扰消除 门电路

Competitive Adventure in Assembled Logical Circuit

Student Majoring in Network Engineering Guo Xiang Tutor Wu Junhua

Abstract: The disturbance pulse caused by competition and adventure may be emerged in the out put terminal of assembled logic circuit when the statement of input signals changes. The misact caused by the disturbance may appear if the load is very sensitive to the pulse. So the measures should be taken to eliminate the competition and adventure. The reasons of competition and adventure in assembled logic circuit are analyzed and the judging and eliminating method are provided in the paper. The interval between on/off levels in a gate circuit and the delay time of gate circuits is resulted in by competitive adventure. Competitive adventure can be detected by a circuit’s logical function, listing the truth table of circuit in sequence and testing the circuit. The methods of exerting gating pulse and blocking pulse, transforming function of a circuit, and adding redundancy product term, parallel connection capacitance at the output terminal, etc are applied to eliminate competitive adventure. Key words: Assembled logic circuit; Competition and adventure; Disturbance eliminating; Gate circuits