低能电子束照射集成电路芯片时的静态电容衬度分析

- 格式:pdf

- 大小:201.59 KB

- 文档页数:6

40nm工艺下电容的失配40nm工艺下电容的失配是集成电路设计中一个常见且影响深远的问题。

在现代集成电路设计中,电容是一种非常重要的元件,它在保证电路稳定性、性能优化等方面扮演着重要角色。

然而,在40nm工艺下,电容的失配问题却成为了制约集成电路性能的一个关键因素。

电容失配是指在设计中理论上相等的两个电容,在实际制作中却会因为工艺因素、布局因素等原因导致在电容值上存在一定程度的差异。

这种失配会对电路性能造成严重的影响,例如在模拟电路中导致增益、带宽等参数的不稳定,甚至在数字电路中引起时序问题、功耗增加等。

因此,研究40nm工艺下电容失配的原因及解决方法对于提高集成电路设计的质量和性能具有重要意义。

在研究40nm工艺下电容失配问题时,首先需要了解工艺对电容特性的影响。

40nm工艺是一种先进的半导体制造工艺,其特点是线宽和间距均为40纳米。

在这种工艺下,电容主要由金属导线之间的氧化层构成。

然而,由于工艺制作的不可控因素,导致不同电容之间的氧化层厚度、面积等参数存在一定差异,从而导致了电容失配的问题。

其次,40nm工艺下电容失配还受到布局因素的影响。

在集成电路设计中,电容往往是分布在不同位置的,而40nm工艺下的电容布局会受到互连线、晶体管等因素的影响,进而影响到电容的失配情况。

因此,在进行电容失配研究时,需要考虑到布局对电容失配的影响,并通过合理的布局设计来减小失配带来的影响。

除此之外,40nm工艺下电容失配还受到温度、工作频率等因素的影响。

在实际应用中,集成电路往往需要在不同温度下、不同工作频率下正常工作,而这些因素会对电容的失配情况造成一定的影响。

因此,为了减小40nm工艺下电容失配带来的影响,需要在设计中考虑到温度、工作频率等因素,并在实际测试中进行相应的验证。

基于40nm工艺下电容失配问题的研究,可以采取多种方法来减小失配带来的影响。

首先,可以通过工艺优化来减小电容之间的失配。

例如,优化氧化工艺、金属导线布局等方式来减小电容失配带来的影响。

浅谈FD-SOI与深度耗尽沟道DDC mos器件4)FD-SOI MOS器件:4.1 当MOS器件的特征尺寸不断缩小至22nm及以下时,提高沟道的掺杂浓度和降低源漏结深已仍不能很好的改善短沟道效应。

在SOI绝缘层上的平面硅技术基础上提出FD-SOI晶体管。

研究发现要使FD-SOI有效抑制短沟道效应,并能正常工作,绝缘层上硅膜的厚度应限制在栅长的四分之一左右。

FD-SOI晶体管的沟道厚度很小,下面紧贴着埋层氧化物,栅的垂直电场可以有效的控制器件的沟道,从而降低了器件关闭时的漏电流,抑制短沟道效应。

SOI晶片有三层:1. 硅的薄表面层(形成晶体管);2.绝缘材料埋层;3.用于支撑的硅衬底。

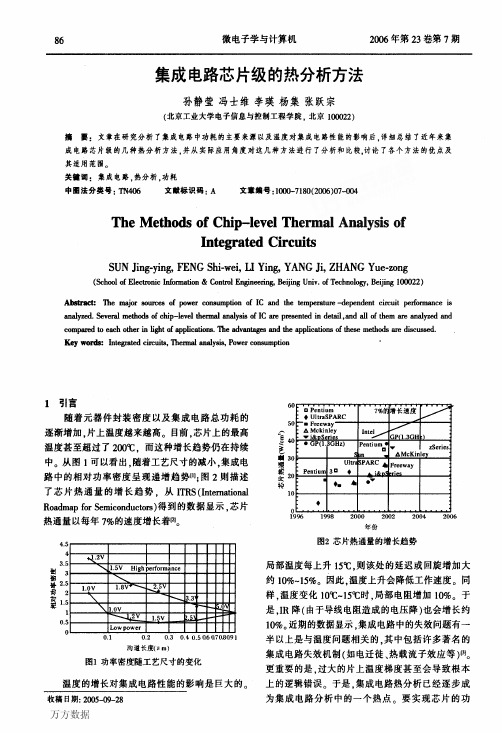

图3.和图4是CMOS集成电路体硅平面结构、FD-SOI结构与FinEFT结构对比。

掩埋氧化层是为了减少寄生结电容。

寄生电容越小,晶体管工作越快。

埋入氧化层薄到与沟道的深度相同,硅薄膜限定了源漏结深,且不存在远离栅极的泄漏路径。

同时也限定了源漏结的耗尽区,减少源漏耗尽区横向扩展宽度,可改善DIBL,短沟道效应,亚阈特性,降低电路的静态功耗。

此外,FDSOI晶体管无需沟道掺杂,可以避免随机掺杂涨落效应,从而保持稳定的阈值电压,同时还可以避免因掺杂而引起的迁移率退化。

采用FD-SOI的功耗更低,成本更少。

(图5B)4.2 FD-SOI特点如下4.2.1FD-SOI优势1.FD-SOI具有低功耗,防辐射,低软错误率,耐高温和EMC。

2.漏/源寄生电容减小,,提高了器件频率,降低漏电流与功耗。

与体硅CMOS相比,器件的延迟和动态功耗更低。

3.具有背面偏置能力,还可以降低电源电压,20nm厚度的氧化埋层类似第二个栅氧化层(衬底是栅极)衬底加偏置电压可以获得调节阈值电压VT效果。

(加强栅对沟道的控制能力)4.消除了闩锁效应。

5.与硅工艺相容,可减少13-20%工序,具有更好的mos器件特性,SOI器件的亚阈值特性更好。

5.浮体效应很小。