Altera-软件无线电数字下变频技术研究及FPGA实现-何立松

- 格式:pdf

- 大小:3.00 MB

- 文档页数:24

基于FPGA的数字上/下变频SOPC的设计与实现

汪东华;俞晓磊;赵志敏

【期刊名称】《电光系统》

【年(卷),期】2007(000)003

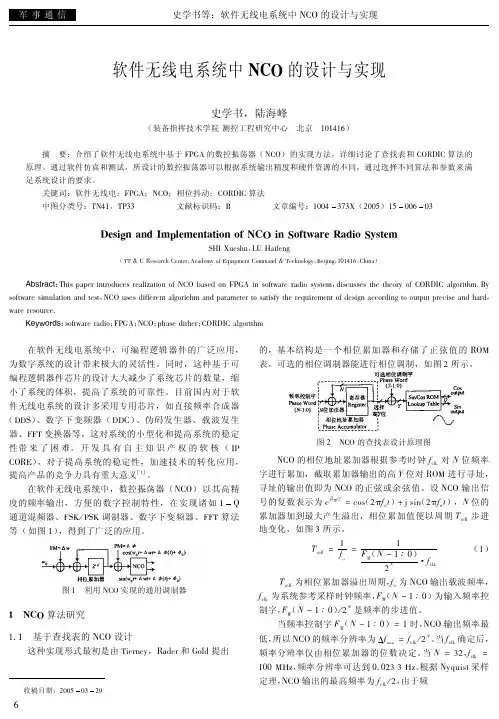

【摘要】在宽带中频软件无线电通信系统中,数字上变频(DUC)及下变频(DDC)是其核心技术之一。

本文介绍了数字上/下变频的原理,给出了一种基于现场可编程逻辑器件(FPGA)的数字上/下变频片上可编程系统(SOPC)的设计方案,并重点讨论了有限冲击响应(FIR)滤波器的设计、内插器和抽取器的实时处理结构一多相滤波器结构以及数控振荡器(NCO)的实现。

在Xilinx公司的FPGA集成开发软件ISE7.1中编写了相应的通信程序,并对整个系统进行了实验验证。

结果表明系统稳定可靠,方案是可行的。

【总页数】4页(P36-38,42)

【作者】汪东华;俞晓磊;赵志敏

【作者单位】江苏省产品质量监督检验研究院,江苏南京210000;南京航空航天大学,江苏南京210016

【正文语种】中文

【中图分类】TN914.3

【相关文献】

1.基于软件无线电数字下变频的FPGA设计与实现 [J], 殷兆云

2.基于FPGA的数字下变频的设计与实现 [J], 贺莹;王闯

3.基于FPGA的数字下变频设计与实现 [J], 赵艳杰;王东;刘志红;贾晨

4.数字下变频基于FPGA的软件设计与实现 [J], 马纯

5.基于FPGA的在线可重配置数字下变频器的设计与实现 [J], 田黎育;袁一丹;李晓阳;吕佳

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的高速数字下变频系统设计摘要:基于FPGA设计了一高速数字下变频系统,在设计中利用并行NCO和多相滤波相结合的方法有效的降低了数据的速率,以适合数字信号处理器件的工作频率。

为了进一步提高系统的整体运行速度,在设计中大量的使用了FPGA中的硬核资源DSP48。

Xilinx ISE14.4分析报告显示,电路工作速度可达360MHz。

最后给出了在Matlab和ModelSim中仿真的结果,验证了各个模块以及整个系统的正确性。

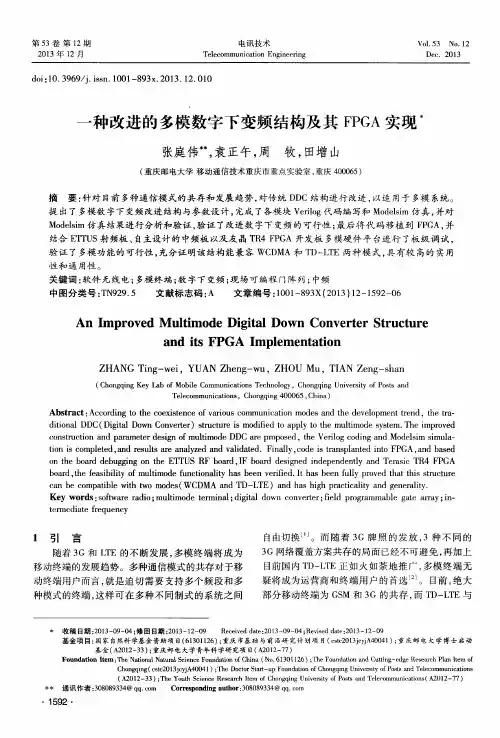

数字下变频(Digital Down Conversion,DDC)是软件无线电系统的关键模块之一,其可将高频数据流信号变成易于后端数字信号处理器(Digital Signal Processor,DSP)设备实时处理的低频数据流信号。

在数字下变频实现中,随着信号采样率的不断提高,数据率也会相应的提高,但是实际应用中随着数据速率的不断提高,数据处理器件(如FPGA)的处理速度会无法满足要求而不能正常工作,从而带来了数字信号处理的瓶颈问题。

本设计就是以多路并行NCO技术为基础,研究了如何在FPGA中用多路并行采样数据的方式来解决数据处理器件无法提供高速率的匹配信号的问题,并给出了高速DDC实现的架构和仿真结果。

1 数字下变频基本原理数字下变频主要由频谱搬移和抽取两部分组成,如图1所示,其中频谱搬移包含数控振荡器(Numerically Controlled Oscillators,NCO)、乘法器和低通滤波器(LPF,Low Pass Filter);抽取包含抽取滤波器(LPF2)和D倍的抽取,LPF2是为了限制信号的频谱,以免抽取后发生混叠。

模拟信号经过A/D转换后分成两路信号,一路信号和NCO输出的正弦信号相乘(同相分量),一路和NCO输出的余弦信号相乘(正交分量),之后经过低通滤波器(LPF1)将高频分量滤除,然后信号经过抽取滤波以降低速率,最终输出的两路信号就可以送往后续的数字信号处理器中做进一步的处理。

数字下变频的FPGA实现

贾雪琴;李强;王旭;李景宏

【期刊名称】《仪表技术与传感器》

【年(卷),期】2006(000)001

【摘要】研究了高倍抽取的数字下变频设计,重点分析了基于级联积分梳状滤波器和级联半带滤波器的多级抽样频率算法.并提出了用最新的Systemgenerator软件实现FPGA的设计、仿真方案,缩短了开发周期,简化了设计流程,增加了系统的集成度和稳定性,降低了开发成本.对于混频器、级联积分梳状滤波器和数字下变频器都给出了仿真波形.

【总页数】3页(P56-58)

【作者】贾雪琴;李强;王旭;李景宏

【作者单位】东北大学信息科学与工程学院,辽宁,沈阳,110004;东北大学信息科学与工程学院,辽宁,沈阳,110004;东北大学信息科学与工程学院,辽宁,沈阳,110004;东北大学信息科学与工程学院,辽宁,沈阳,110004

【正文语种】中文

【中图分类】TN77

【相关文献】

1.宽带信号接收机中数字下变频的设计与FPGA实现 [J], 覃荣捷;袁晓;辛超;陆大海

2.用MATLAB在FPGA芯片中实现数字下变频设计的研究 [J], 温浪明

3.宽带信号数字下变频技术的FPGA实现 [J], 李芾

4.用MATLAB在FPGA芯片中实现数字下变频设计的研究 [J], 温浪明

5.基于快行FIR滤波器的数字下变频设计及FPGA实现 [J], 孙星;李刚;姜童;孙宝华

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的高效数字下变频设计

卢卿;王钢;韩方景

【期刊名称】《电子信息对抗技术》

【年(卷),期】2010(25)3

【摘要】介绍了一种高效数字下变频的实现方法,重点介绍采用坐标转换数字计算机(CORDIC)在实现NCO的同时也完成了混频器功能.改进了滤波器组结构,在减少资源消耗的同时,实现了数字下变频功能.通过ISE和Modelsim仿真实验证明,该方案正确,且有效节省硬件资源,在短波电台的应用中取得了较好的效果.

【总页数】4页(P77-80)

【作者】卢卿;王钢;韩方景

【作者单位】国防科技大学电子科学与工程学院,长沙,410073;国防科技大学电子科学与工程学院,长沙,410073;国防科技大学电子科学与工程学院,长沙,410073【正文语种】中文

【中图分类】TN773

【相关文献】

1.数字下变频中的FPGA高效滤波器设计 [J], 李夏;刘皓

2.一种基于FPGA的高效多路独立数字下变频的实现方法 [J], 弥宪梅;刘亭亭;杨鑫;刘芬

3.基于FPGA的数字下变频设计 [J], 许丹

4.基于FPGA的高速高效率数字下变频 [J], 戴曜泽;张棋;徐小淇

5.基于快行FIR滤波器的数字下变频设计及FPGA实现 [J], 孙星;李刚;姜童;孙宝华

因版权原因,仅展示原文概要,查看原文内容请购买。

文章编号:1001-893X(2004)03-0016-04用FPGA 实现数字下变频杨力生,谭晓衡,杨士中(重庆大学通信工程学院,重庆400044)摘 要:在接收信号的数字化、软化的实现中,数字下变频起着重要的作用。

本文首先介绍了数字下变频的组成结构,然后详细分析了数字下变频的工作原理,描述了在实现数字下变频时,设计方案所采用的高效滤波器 CIC 滤波器和多相抽取滤波器的结构和原理。

最后,用通过Simulink 对数字下变频的性能进行了仿真。

在仿真的基础上使用Insight 公司的FPGA 开发系统,用测试电路实测了数字下变频的性能。

关键词:数字下变频器;FPGA;CIC 数字滤波器;多相滤波器中图分类号:TN773 文献标识码:ARealize Digital Downconversion by FPGAY ANG Li -shen g ,TAN Xiao -heng ,Y ANG Shi -zhong(Communication Engineering School,Chongqing University,Chongqing400044,China)Abstract:Digital downcoversion plays a key role in the digitized and software-oriented process of the received signal.First,the architec ture of the digital downc onvertor(DDC)is introduced.Then the operational principle of DDC is analysed.At the same time,the efficient struc ture of digital filter is described in which DDC is adopted.Finally,the performance simulation results of the DDC is given by Simulink,and on this base,the perfomance of DDC is tested with the FPGA devoloping system of Insight corp.Key words:Digital downcovertor;FPGA;CIC digital filter;Polyphase filter一、序 言在数字接收机中,数字下变频器(DDC)一般执行信道的访问功能。

基于FPGA的数字下变频设计与实现赵艳杰;王东;刘志红;贾晨【摘要】数字下变频是全数字解调器中的关键技术之一,其性能好坏直接决定解调器的工作性能.给出一种基于FPGA的数字下变频设计,详细介绍正交变换、CIC抽取滤波及根升余弦滚降FIR低通滤波器的原理设计,并可编程设置各个模块参数,自动生成及动态配置滤波器系数.该设计在Xilinx公司XC3S4000 FPGA芯片的硬件平台和ISE 9.2开发环境下,采用Verilog语言编程实现,经过实际通信系统验证,在全数字解调器中很好地完成了多载波、多速率信号的数字下变频处理功能,具有很强的灵活性、稳定性和可扩展性.【期刊名称】《农业科技与装备》【年(卷),期】2014(000)006【总页数】4页(P51-54)【关键词】数字下变频;CIC;FPGA【作者】赵艳杰;王东;刘志红;贾晨【作者单位】;;;【正文语种】中文【中图分类】TN92为了更好地体现软件无线电体系中在尽可能靠近天线的地方使用A/D 的核心思想,全数字化解调器的设计大多采用直接在中频进行信号采样,即高频模拟信号先经过模拟下变频到适当中频,然后在中频阶段对其进行A/D 采样以输出高速的数字中频信号[1],经过数字下变频技术的抽取和低通滤波处理,使其变为较低速率的基带信号再送给后端数字信号处理模块进行解调、译码等相关处理。

数字下变频(DDC)技术连接着前端ADC 和后端DSP,其性能好坏直接影响解调器的可靠性与稳定性,是全数字解调器的核心技术之一。

目前,数字下变频模块的实现基本分两种方式:一种是利用专用DDC 芯片完成数字下变频功能,另一种是利用自主搭建的软硬件平台编程设计实现。

专用数字下变频芯片具有抽取比率大、性能稳定等优点,但专用数字下变频芯片价格昂贵、灵活性不强,不能充分体现软件无线电的优势[2]。

近年来,FPGA 器件在工艺方面的进步,为之带来了前所未有的逻辑规模和强大的处理性能,用FPGA 来实现比用专用芯片可以带来更多的好处。

基于FPGA的数字下变频的实现

朱运航;邓知辉

【期刊名称】《微处理机》

【年(卷),期】2010(31)6

【摘 要】针对软件无线电接收机中数字下变频的特点,提出了一种合理的基于

FPGA实现宽带数字下变频的方案,并利用Matlab中的Dspbuilder提供的IP核

得到了总体的仿真结果.该接收系统用于WCDMA移动通信网络的基站体系中,能

很好地实现手机信号覆盖和传输.

【总页数】3页(P27-29)

【作 者】朱运航;邓知辉

【作者单位】湖南信息职业技术学院,长沙,410200;湖南信息职业技术学院,长

沙,410200

【正文语种】中 文

【中图分类】TN92

【相关文献】

1.基于FPGA的水声信号数字下变频的实现 [J], 唐伟杰

2.基于软件无线电数字下变频的FPGA设计与实现 [J], 殷兆云

3.基于FPGA的数字下变频的设计与实现 [J], 贺莹;王闯

4.数字下变频基于FPGA的软件设计与实现 [J], 马纯

5.基于快行FIR滤波器的数字下变频设计及FPGA实现 [J], 孙星;李刚;姜童;孙宝

华

因版权原因,仅展示原文概要,查看原文内容请购买

用FPGA实现数字下变频

杨力生;谭晓衡;杨士中

【期刊名称】《电讯技术》

【年(卷),期】2004(44)3

【摘要】在接收信号的数字化、软化的实现中,数字下变频起着重要的作用.本文首先介绍了数字下变频的组成结构,然后详细分析了数字下变频的工作原理,描述了在实现数字下变频时,设计方案所采用的高效滤波器--CIC滤波器和多相抽取滤波器的结构和原理.最后,用通过Simulink对数字下变频的性能进行了仿真.在仿真的基础上使用Insight公司的FPGA开发系统,用测试电路实测了数字下变频的性能.【总页数】4页(P16-19)

【作者】杨力生;谭晓衡;杨士中

【作者单位】重庆大学,通信工程学院,重庆,400044;重庆大学,通信工程学院,重庆,400044;重庆大学,通信工程学院,重庆,400044

【正文语种】中文

【中图分类】TN773

【相关文献】

1.宽带信号接收机中数字下变频的设计与FPGA实现 [J], 覃荣捷;袁晓;辛超;陆大海

2.用MATLAB在FPGA芯片中实现数字下变频设计的研究 [J], 温浪明

3.宽带信号数字下变频技术的FPGA实现 [J], 李芾

4.用MATLAB在FPGA芯片中实现数字下变频设计的研究 [J], 温浪明

5.基于快行FIR滤波器的数字下变频设计及FPGA实现 [J], 孙星;李刚;姜童;孙宝华

因版权原因,仅展示原文概要,查看原文内容请购买。