eetop[1].cn_Xilinx fpga 设计培训中文教程-同步设计技术

- 格式:pdf

- 大小:529.36 KB

- 文档页数:27

![eetop[1].cn_FPGA设计环境中加时序约束](https://img.taocdn.com/s1/m/1bff4c53ad02de80d4d840bd.png)

在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。

通常,在FPGA设计工具中都包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑。

通常,需要对这几种路径分别进行约束,以便使设计工具能够得到最优化的结果。

下面对这几种路径分别进行讨论从输入端口到寄存器:这种路径的约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。

约束名称:input delay. 约束条件的影响主要有4个因素:外部芯片的Tco,电路板上信号延迟Tpd,FPGA的Tsu, 时钟延迟Tclk。

Tco的参数通常需要查外部芯片的数据手册。

计算公式:input delay = Tco+Tpd+Tsu-Tclk. FPGA的Tsu也需要查FPGA芯片的手册。

FPGA速度等级不同,这个参数也不同。

Tpd和Tclk需要根据电路板实际的参数来计算。

通常,每10cm的线长可以按照1ns来计算. 例如:系统时钟100MHz, 电路板上最大延迟2ns, 时钟最大延迟 1.7ns, Tco 3ns,FPGA的Tsu为0.2ns. 那么输入延迟的值: max Input delay = 2+3+0.2-1.7=3.5ns. 这个参数的含义是指让FPGA的设计工具把FPGA的输入端口到第一级寄存器之间的路径延迟(包括门延迟和线延迟)控制在 10ns-3.5ns=6.5ns 以内。

寄存器到寄存器:这种路径的约束是为了让FPGA设计工具能够优化FPGA内寄存器到寄存器之间的路径,使其延迟时间必须小于时钟周期,这样才能确保信号被可靠的传递。

由于这种路径只存在于FPGA内部,通常通过设定时钟频率的方式就可以对其进行约束。

对于更深入的优化方法,还可以采用对寄存器的输入和寄存器的输出加入适当的约束,来使逻辑综合器和布线器能够对某条路径进行特别的优化。

Xilinx_FPGA中文教程Spartan-3E Starter Kit Board User GuideChapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock SourcesChapter 4: FPGA Configuration Options Chapter 5: Character LCD ScreenChapter 6: VGA Display PortChapter 7: RS-232 Serial PortsChapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture CircuitChapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial FlashChapter 13: DDR SDRAMChapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion ConnectorsChapter 16: XC2C64A CoolRunner-II CPLDChapter 17: DS2432 1-Wire SHA-1 EEPROMChapter 1:Introduction and OverviewSpartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。

设备支持设备支持::Spartan-3E 、CoolRunner-II关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash(XCF04S-VO20C)时钟时钟::50 MHz 晶体时钟振荡器存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器显示器: VGA 显示端口,16 字符- 2 线式 LCD电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。

fpga xilinx课程设计一、教学目标本课程的目标是让学生了解和掌握FPGA和Xilinx的基本概念、原理和应用。

通过本课程的学习,学生应能理解FPGA的工作原理,掌握Xilinx软件的基本操作,并能够利用Xilinx工具进行简单的FPGA设计。

1.理解FPGA的基本概念和原理。

2.掌握Xilinx软件的基本操作。

3.了解FPGA在数字电路设计中的应用。

4.能够使用Xilinx工具进行简单的FPGA设计。

5.能够进行FPGA的编程和配置。

6.能够对FPGA设计进行仿真和测试。

情感态度价值观目标:1.培养学生的创新意识和实践能力。

2.增强学生对电子技术的兴趣和热情。

3.培养学生团队合作和解决问题的能力。

二、教学内容本课程的教学内容主要包括FPGA的基本概念和原理、Xilinx软件的基本操作以及FPGA在数字电路设计中的应用。

1.FPGA的基本概念和原理:介绍FPGA的定义、工作原理和特点,以及FPGA在数字电路设计中的应用。

2.Xilinx软件的基本操作:介绍Xilinx软件的安装和启动,以及基本的FPGA设计流程,包括设计输入、综合、布局布线和编程配置等步骤。

3.FPGA在数字电路设计中的应用:介绍FPGA在数字电路设计中的典型应用案例,如数字信号处理、数字逻辑控制等,并通过实例讲解FPGA设计的具体过程和方法。

三、教学方法本课程采用多种教学方法,包括讲授法、案例分析法和实验法等,以激发学生的学习兴趣和主动性。

1.讲授法:通过教师的讲解,让学生了解和掌握FPGA和Xilinx的基本概念和原理。

2.案例分析法:通过分析典型的FPGA应用案例,让学生了解FPGA在数字电路设计中的应用和实现方法。

3.实验法:通过实验操作,让学生亲手实践FPGA的设计和编程,培养学生的实际操作能力和实践能力。

四、教学资源本课程所需的教学资源包括教材、参考书、多媒体资料和实验设备等。

1.教材:选用合适的教材,用于引导学生学习和理解FPGA和Xilinx的基本概念和原理。

fpga培训课程设计一、教学目标本课程的教学目标是使学生掌握FPGA(现场可编程门阵列)的基本原理、设计和应用。

具体目标如下:1.知识目标:–了解FPGA的基本概念、结构和分类。

–掌握FPGA的编程语言(如VHDL或Verilog)。

–理解FPGA在数字电路设计中的应用。

2.技能目标:–学会使用FPGA设计工具(如Altera的Quartus或Xilinx的Vivado)。

–能够编写简单的FPGA程序,实现基本的逻辑功能。

–具备分析和解决FPGA设计中问题的能力。

3.情感态度价值观目标:–培养对FPGA技术的兴趣和好奇心,认识到其在现代电子技术中的重要性。

–培养团队合作精神和沟通协调能力,学会与他人合作完成FPGA项目。

二、教学内容根据课程目标,教学内容主要包括以下几个部分:1.FPGA的基本概念和结构:介绍FPGA的定义、特点、工作原理和常见类型。

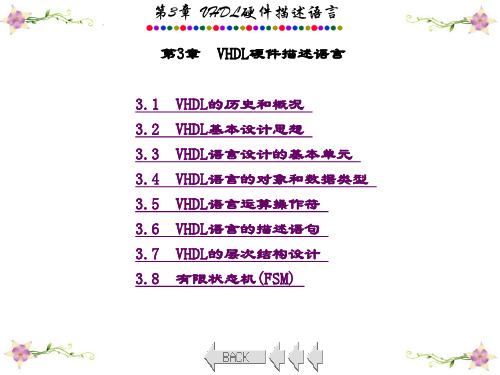

2.FPGA的编程语言:学习VHDL和Verilog的基本语法和编程技巧。

3.FPGA的设计流程:掌握FPGA设计的整个流程,包括硬件描述语言编写、代码编译、逻辑综合、布局布线和编程下载。

4.FPGA应用案例:分析和学习FPGA在数字电路设计中的应用实例,如数字信号处理、数字逻辑控制等。

三、教学方法为了达到课程目标,我们将采用以下教学方法:1.讲授法:通过讲解FPGA的基本概念、原理和编程语言,使学生掌握相关知识。

2.案例分析法:分析和学习实际的FPGA应用案例,提高学生的应用能力。

3.实验法:安排实验室实践环节,让学生亲手操作FPGA设计工具,锻炼其实际操作能力。

4.小组讨论法:鼓励学生分组合作,共同完成FPGA项目,培养团队合作精神和沟通协调能力。

四、教学资源为了支持课程的顺利进行,我们将准备以下教学资源:1.教材:选用权威、实用的FPGA教材,为学生提供系统性的学习资料。

2.多媒体资料:制作PPT、教学视频等多媒体资料,丰富教学手段,提高学生的学习兴趣。