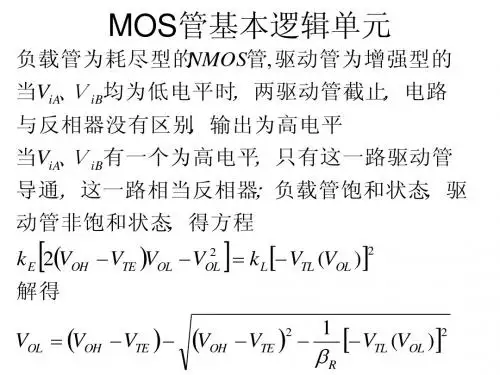

最坏情况, 只有一个驱动管导通时 的VoL 值, 对于给定

2 Gon Ron

2 VOL I D kE VOH VTE VOL 2 I D / VOL k E VOH VTE VOL

Gon k A VOH VTE VOL k B VOH VTE VOL

改进多米诺CMOS逻辑

• 省掉多米诺缓冲器,级联的各逻辑块交替地 由P型管和N型管构成 • 当¢=0,第一级预充到高电平(NMOS管逻辑), 第二级预充到低电平,第三级预充到高电平. • 由于第二级由PMOS管构成,在预充电期间, PMOS管都处于截止状态. • 由于第二级预充到低电平,第三级NMOS管也 都处于截止状态. • 因此可以进行多米诺连接

A B R L L

2VTL (VOL )

2 2 OL

VOH

VTD VOL

V 2

NMOS与非门

R 相当倒相器的两倍 , 要得到相同的

VOL 与非门每个驱动门所占 芯片面积相 当倒相器的两倍 ; 两个驱动管相串联 , 导通时等效电阻等于两 者之和 RON RONA RONB RON 2 RONA 2 RONB

NMOS与非门输出电容

VB VOH VB 0 或 V A VOH V A VOH COUT CGDA CGSA CGDB CGDL C LINE CG k (VOH , VOL )(C DBA C SBA C DBB C SBL ) V A 0 VB 0 或 VB VOH V A 0 COUT CGDA CGDL C LINE CG k (VOH , VOL )(C DBA C SBL )